## POLITECNICO DI MILANO

Scuola di Ingegneria Industriale e dell'informazione Corso di Laurea Magistrale in Ingegneria Elettronica

# Sigma-Delta Analogue-to-Digital converter for column-parallel CMOS image sensors

Relatore: Prof. Marco Sampietro

Correlatore: Ing. Iain Sedgwick

Tesi di laurea di:

Michele SANNINO Matr. 817325

Anno accademico 2015/2016

## Acknowledgements

I would like to thank Iain Sedgwick whose precious, patient and close support in both technical and formal matters has greatly helped me in the accomplishment of this work. I would also like to thank Renato Turchetta and the whole CMOS Sensor Design Group of the Rutherford Appleton Laboratory (in Harwell, Oxfordshire), for the passionate contribution they offered.

Special thanks also to Professors Marco Sampietro and Giorgio Ferrari, who devoted some of their own time to help me move forward with my work.

# **Summary**

| Acknowledg   | gements                                          | 3  |

|--------------|--------------------------------------------------|----|

| Summary      |                                                  | 5  |

| List of Figu | res                                              | 9  |

| List of Tabl | es                                               | 13 |

| Introduzion  | ıe                                               | 14 |

| Introduction | n                                                | 17 |

| Chapter 1    | CMOS Image Sensor basics                         | 21 |

| 1.1 Pri      | inciple of operation                             | 21 |

| 1.1.1        | Non-linearity                                    | 22 |

| 1.1.2        | Full well and dynamic range                      | 22 |

| 1.2 No       | oise contributions                               | 23 |

| 1.2.1        | Shot noise                                       | 23 |

| 1.2.2        | Reset noise                                      | 23 |

| 1.2.3        | Fixed Pattern Noise                              | 24 |

| Chapter 2    | Analogue-to-Digital-Converters for image sensors | 25 |

| 2.1 AI       | OCs figures of merit                             | 25 |

| 2.1.1        | ENOB                                             | 26 |

| 2.1.2        | DNL                                              | 27 |

| 2.1.3        | INL                                              | 27 |

| 2.2 Re       | eadout topologies for fast imagers               | 27 |

| 2.2.1        | Frame rate versus conversion and readout time    | 27 |

| 2.2.2        | Column-parallel                                  | 29 |

| 2.2.3        | Stacked chip                                     | 29 |

| 2.2.4        | Pixel-level ADC                                  | 30 |

| 2.3 Tr       | ade-offs in ADC architectures for image sensors  | 31 |

| 2.4 Pu       | rpose of the project                             | 33 |

| 2.4.1        | Objective                                        | 33 |

| 2.4.2        | Specifications                                   | 33 |

| 2.4.3        | Expected achievable frame-rate                   | 35 |

| 2.4.4        | Tools used                                       | 35 |

| Chapte | r 3 | Sigma-Delta ADC basics                             | 37 |

|--------|-----|----------------------------------------------------|----|

| 3.1    | Wo  | orking principle                                   | 37 |

| 3.1    | .1  | Structure: modulator and decimator                 | 37 |

| 3.1    | .2  | Oversampling - 0th order modulator                 | 38 |

| 3.1    | .3  | Noise shaping                                      | 39 |

| 3.1    | .4  | Stability and full scale range                     | 42 |

| 3.1    | .5  | Input noise                                        | 44 |

| 3.2    | Inc | remental Sigma Delta                               | 44 |

| 3.2    | .1  | First order ISD resolution analysis                | 45 |

| 3.3    | No  | n idealities                                       | 47 |

| 3.3    | .1  | Limit cycles and dead zones                        | 47 |

| 3.3    | .2  | Noise-shaping degradation                          | 49 |

| Chapte | r 4 | Architecture design and behavioural simulations    | 51 |

| 4.1    | Tin | ne discrete versus time-continuous converters      | 51 |

| 4.2    | Co  | mposite structures versus high-order architectures | 52 |

| 4.3    | Co  | mposite structures                                 | 53 |

| 4.3    | .1  | MASH                                               | 53 |

| 4.3    | .2  | Two-step conversion                                | 54 |

| 4.3    | .3  | Extended counting                                  | 54 |

| 4.4    | Hig | gher order architectures                           | 55 |

| 4.4    | .1  | Noise shaping and resolution                       | 55 |

| 4.4    | .2  | Advantages over first-order composite structures   | 58 |

| 4.4    | .3  | Disadvantages                                      | 59 |

| 4.4    | .4  | Typical architectures                              | 61 |

| 4.5    | Imj | plemented architecture                             | 62 |

| 4.5    | .1  | Order, oversampling ratio and input range          | 62 |

| 4.5    | .2  | InFF versus DiFF                                   | 63 |

| 4.5    | .3  | Comparison through behavioural simulations         | 65 |

| 4.6    | De  | riving analogue specifications                     | 67 |

| 4.6    | .1  | OTA gain                                           | 67 |

| 4.6    | .2  | Comparator's offset and resolution                 | 68 |

| 4.6    | .3  | Noise                                              | 69 |

| Chapte | r 5 | Switched capacitors circuits                       | 71 |

| 5.1    | Pri | nciple of operation                                | 71 |

| 5.2     | Sw                 | itched Capacitor Integrator                       | 72  |

|---------|--------------------|---------------------------------------------------|-----|

| 5.3     | Set                | tling error                                       | 75  |

| 5.4     | Sle                | wing                                              | 75  |

| 5.5     | Finite op-amp gain |                                                   | 76  |

| 5.6     | Cha                | arge injection and clock feed-through             | 77  |

| 5.7     | Wh                 | nite noise in SC circuits                         | 80  |

| 5.8     | 1/f                | noise in periodically reset SC circuits           | 83  |

| Chapter | r 6                | Analogue design – the modulator                   | 85  |

| 6.1     | Cha                | aracteristics of the process                      | 85  |

| 6.2     | Sup                | pplies used                                       | 86  |

| 6.3     | Mo                 | odulator overview                                 | 86  |

| 6.4     | Inte               | egrator stages                                    | 88  |

| 6.4     | .1                 | OTA architecture                                  | 88  |

| 6.4     | .2                 | Sizing of the integrator stages                   | 89  |

| 6.4     | .3                 | Under-damping issue                               | 94  |

| 6.4     | .4                 | Impact of charge injection and clock feed-through | 97  |

| 6.4     | .5                 | Spread of second integrator's gain                | 97  |

| 6.5     | Co                 | mparator/DAC                                      | 98  |

| 6.5     | .1                 | Overview                                          | 98  |

| 6.5     | .2                 | Architecture                                      | 99  |

| 6.5     | .3                 | Operation                                         | 101 |

| 6.5     | .4                 | Power consumption and simulated performance       | 103 |

| Chapte  | r 7                | Digital design and layout                         | 105 |

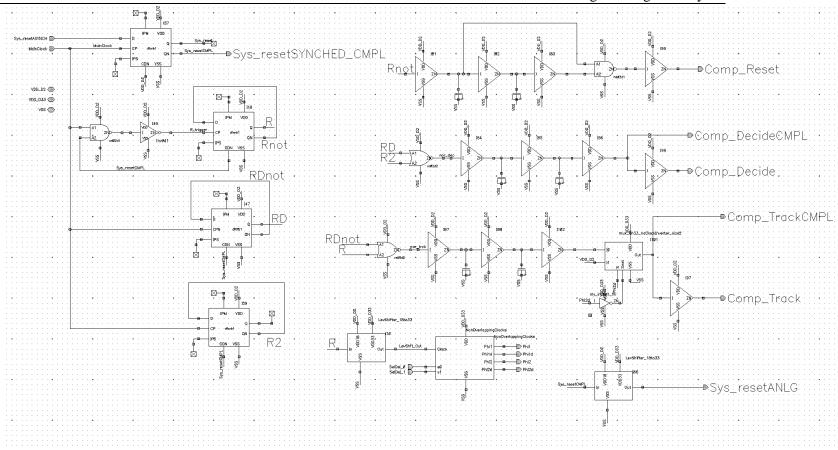

| 7.1     | Tin                | ning signals generator                            | 105 |

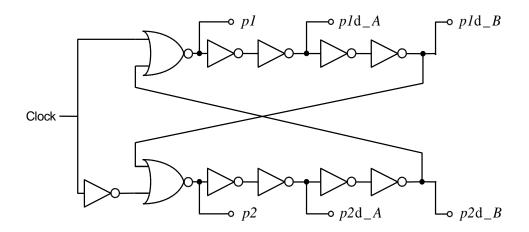

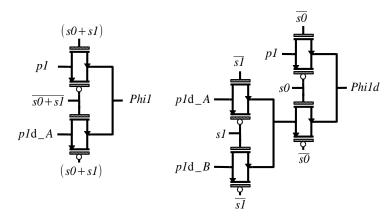

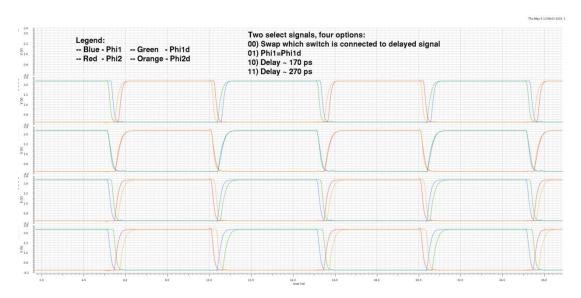

| 7.1     | .1                 | Signals synthesis                                 | 108 |

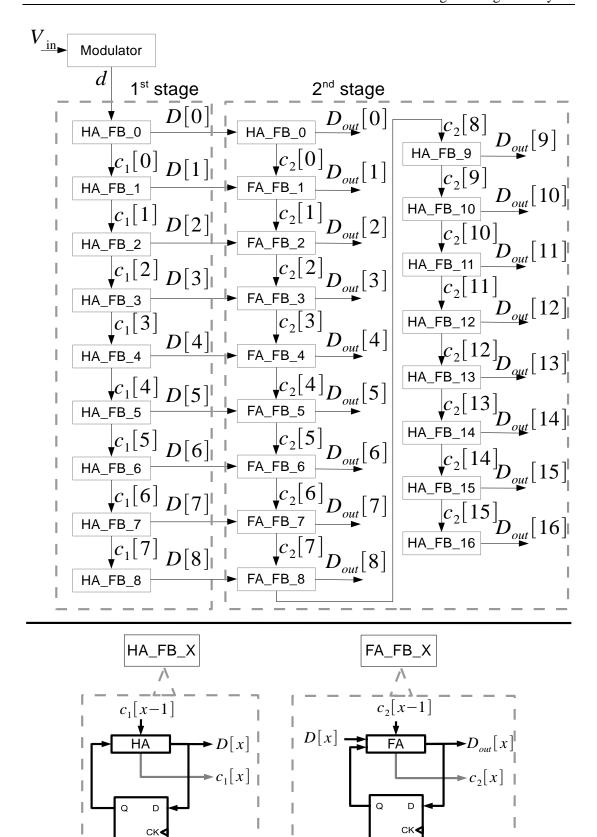

| 7.2     | Dec                | cimator                                           | 112 |

| 7.3     | Lay                | yout and dimensions                               | 114 |

| 7.4     | Spl                | lits                                              | 118 |

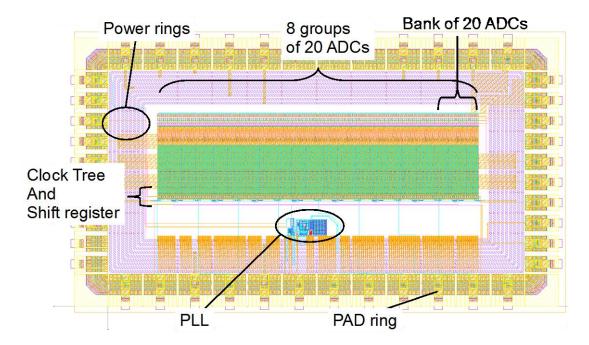

| 7.5     | Tes                | st chip core architecture                         | 120 |

| 7.5     | .1                 | Clocks generation                                 | 120 |

| 7.5     | .2                 | Clocks distribution                               | 120 |

| 7.5     | .3                 | Readout                                           | 120 |

| Chapter | r <b>8</b>         | Simulated performance and future developments     | 123 |

| 8 1     | No                 | n-linearity                                       | 123 |

| Bibliog | raphy . |                                                    | 137 |

|---------|---------|----------------------------------------------------|-----|

| Appen   | dix B.  | Input noise of the telescopic cascode OTA          | 133 |

| Appen   | dix A.  | Integrator boundaries in a first order Sigma-Delta | 131 |

| Conclu  | sions   |                                                    | 129 |

| 8.3     | Powe    | er consumption                                     | 126 |

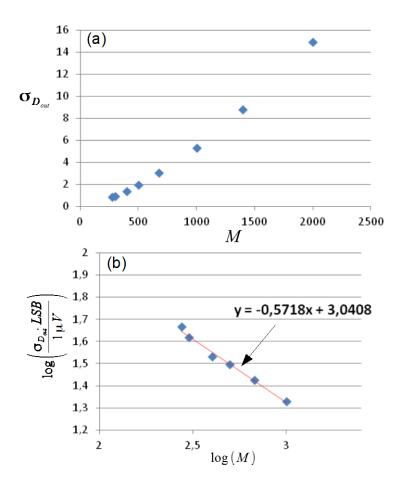

| 8.2     | Noise   | e performance                                      | 125 |

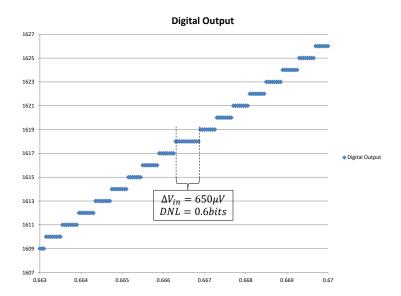

| 8.1     | 1.2     | DNL                                                | 124 |

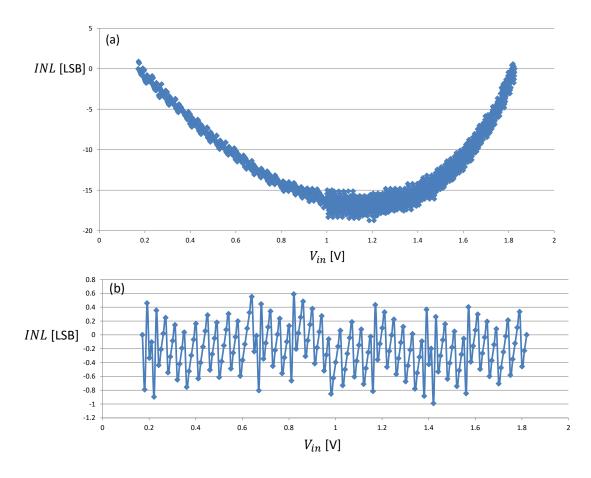

| 8.1     | 1.1     | INL                                                | 123 |

# **List of Figures**

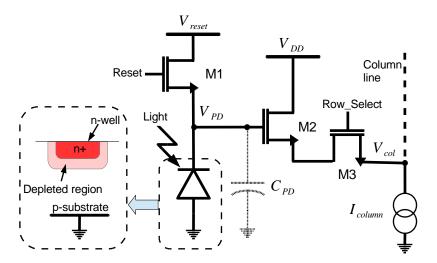

| Figure 1.1  | Basic architecture of a 3-transistors pixel                                       | 21 |

|-------------|-----------------------------------------------------------------------------------|----|

| Figure 1.2  | Time diagram of a pixel operation                                                 | 22 |

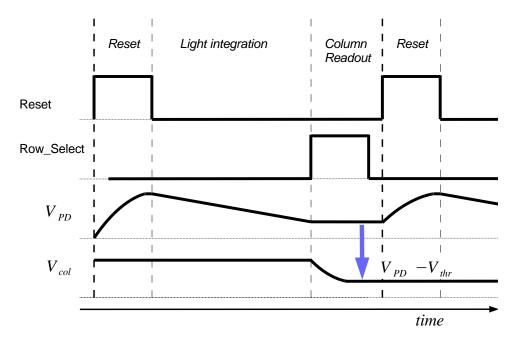

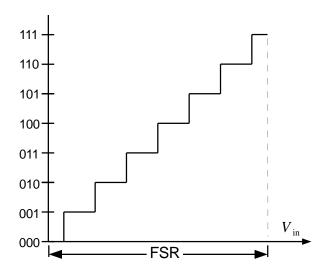

| Figure 2.1  | Trans-characteristic of an ideal ADC with 3 bits of resolution                    | 26 |

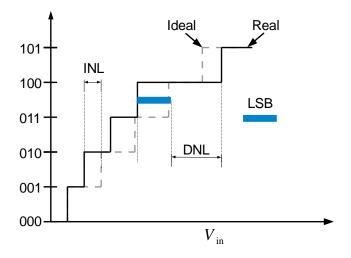

| -           | Transfer curve of an ADC with INL and DNL in evidence                             |    |

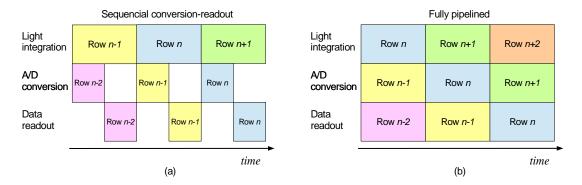

| Figure 2.3  | Pixel readout time diagrams. Conversion and readout operated in series (a) and    |    |

|             | conversion and readout operated in parallel (b)                                   | 28 |

| Figure 2.4  | Column parallel architecture diagram                                              | 29 |

| Figure 2.5  | Conceptual illustration of a stacked chip                                         | 30 |

| Figure 2.6  | Ramp ADC                                                                          | 32 |

| Figure 2.7  | SAR ADC                                                                           | 32 |

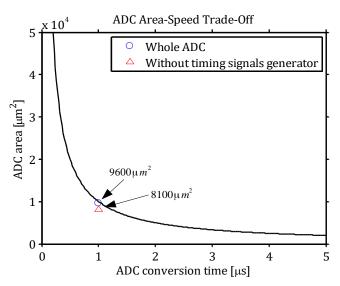

| Figure 2.8  | Trade-off between ADC area and conversion time. As a specification, the           |    |

|             | point corresponding to the developed ADC has to lie below the curve               | 34 |

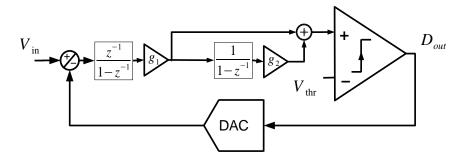

| Figure 3.1  | General architecture of a Sigma-Delta                                             | 37 |

| Figure 3.2  | Block diagram of a basic oversampler (left) and corresponding signal and          |    |

| -           | quantization noise frequency spectrum                                             | 38 |

| Figure 3.3  | Architecture of a first order, time-discrete, Sigma-Delta with binary quantizer   | 39 |

| Figure 3.4  | Linear equivalent model of a first order Sigma Delta                              | 40 |

| Figure 3.5  | Frequency spectrum of the noise transfer function with and without noise          |    |

| -           | shaping                                                                           | 41 |

| Figure 3.6  | Waveforms in an ideal Sigma-Delta (top), with offset at the quantizer input       |    |

|             | (middle) and comparison of the corresponding transfer curves in the case          |    |

|             | <i>M</i> =256 (bottom)                                                            | 43 |

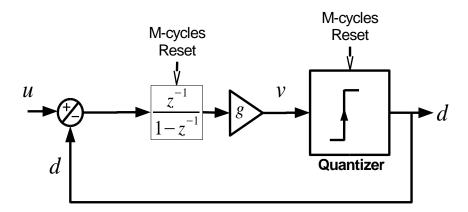

| Figure 3.7  | First order Incremental Sigma Delta                                               | 45 |

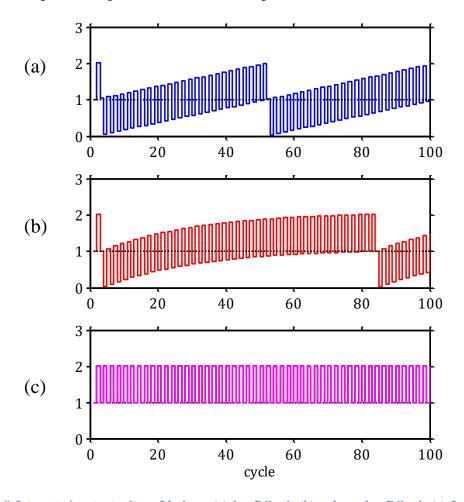

| Figure 3.8  | Integrator's output voltage. Ideal case (a), low DC gain (b) and very low DC      |    |

|             | gain (c). Case (c) is unable to break out of a limit cycle                        | 48 |

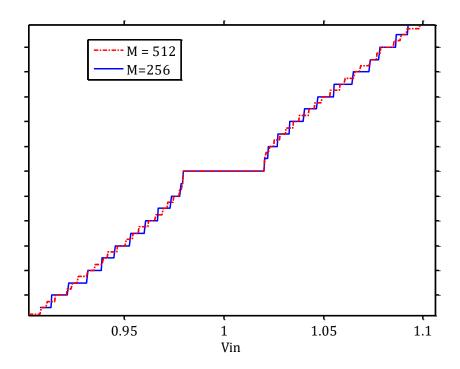

| Figure 3.9  | Transfer curve showing the independence of dead zones on the oversampling         |    |

|             | rates. Values on ordinate axes are not shown because the digital output is        |    |

|             | different for the two curves.                                                     | 49 |

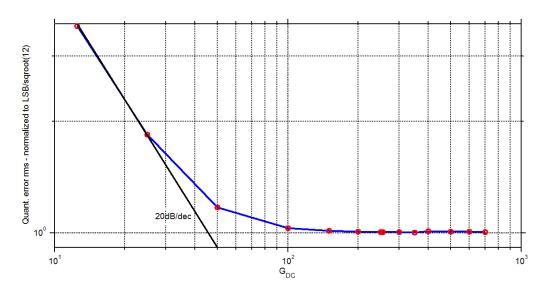

| Figure 3.10 | 0 Rms of the quantization error noise increase for low OpAmp DC gain              | 50 |

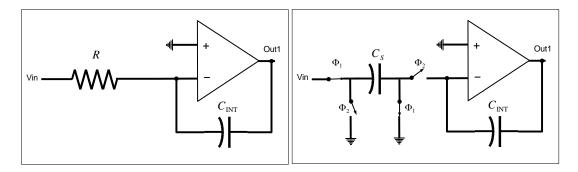

| Figure 4.1  | Blocks in a Sigma-Delta modulator can be implemented with either time-            |    |

| -           | continuous (left) and time-discrete (right) integrators.                          | 52 |

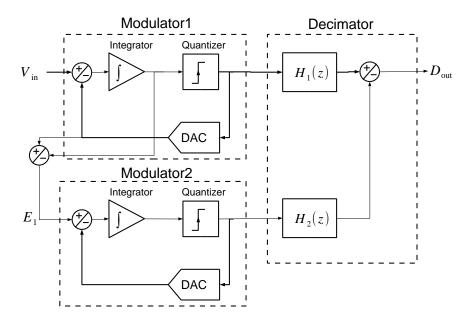

| Figure 4.2  | Block diagram of a MASH modulator                                                 |    |

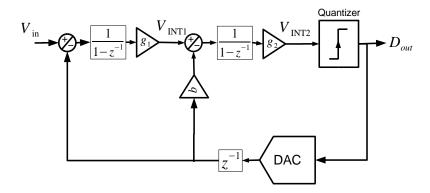

| Figure 4.3  | Example of a 2 <sup>nd</sup> order SDM                                            | 56 |

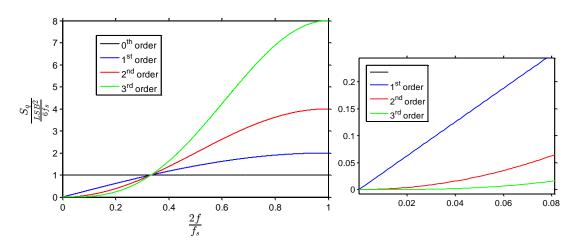

|             | NTF for different values of the order $l$ (left) and detail around $f=0$ (right), |    |

|             | where the pass-band of the DLPF is                                                | 56 |

|             |                                                                                   |    |

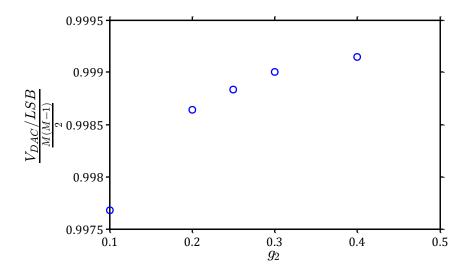

| Figure 4.5 Dependence of the LSB on the gain of the second integrator $g_2$ . On the           |    |

|------------------------------------------------------------------------------------------------|----|

| ordinate is the ratio between the extracted LSB and that estimated with Eq.                    |    |

| (4.10)                                                                                         | 57 |

| Figure 4.6 Noise filtering at different SDM nodes                                              | 58 |

| Figure 4.7 Non monotonic transfer curve for input close to the bottom of the FSR: effect       |    |

| of quantizer overloading                                                                       | 59 |

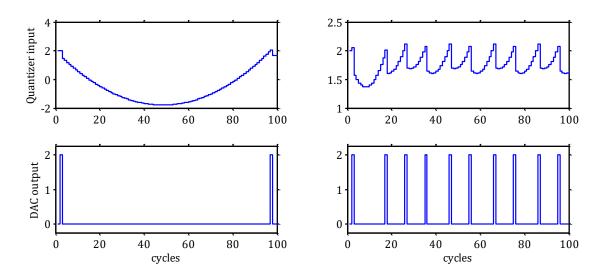

| Figure 4.8 Quantizer input and output waveforms when it is overloaded (left, <i>Vin</i> at 96% |    |

| of FSR) and when it's not (right, Vin at 80% of FSR). Note the clearly lower                   |    |

| autocorrelation of the waveform to the right compared to that on the left                      | 60 |

| Figure 4.9 2 <sup>nd</sup> order SDM which is stable regardless of coefficient g1              | 61 |

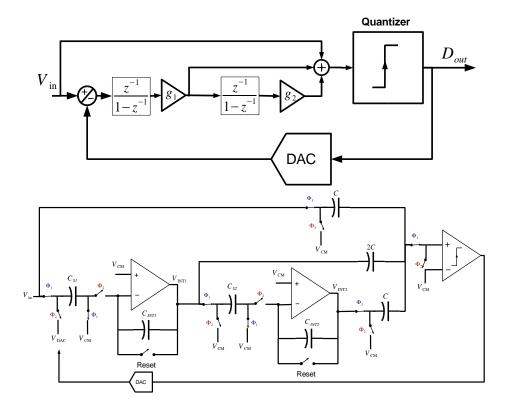

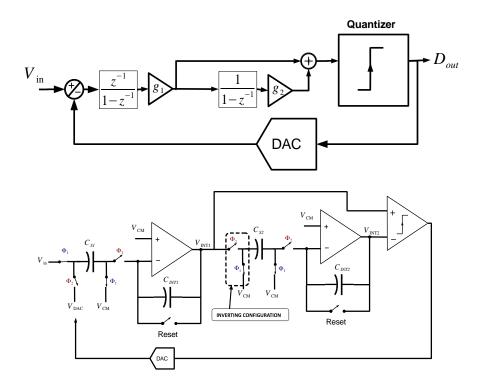

| Figure 4.10 Silva-Steensgard feed forward configuration (InFF). Block diagram (top) and        |    |

| circuit schematic (bottom)                                                                     | 64 |

| Figure 4.11 Simplified feed forward configuration (DiFF). Block diagram (top) and              |    |

| schematic (bottom). The input feed forward branch has been removed to allow                    |    |

| the elimination of the summing capacitors                                                      | 65 |

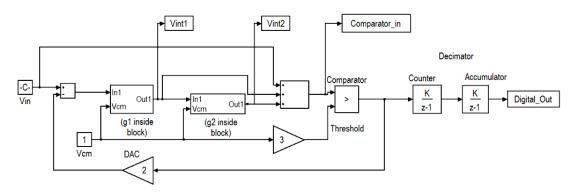

| Figure 4.12 Behavioural simulations architecture block diagram - Input Feed Forward            |    |

| configuration                                                                                  | 65 |

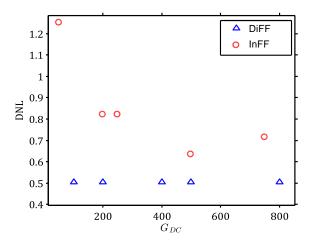

| Figure 4.13 Maximum DNL (in bits) of DiFF and InFF architectures as a function of the          |    |

| amplifiers' DC gain                                                                            | 66 |

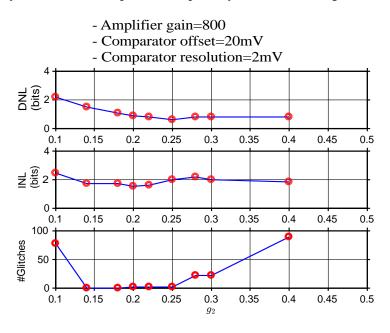

| Figure 4.14 DNL, INL and total number of glitches in the transfer curve as function of         |    |

| g2. Results obtained simulating a non-ideal SDM, with finite DC gain of                        |    |

| OTAs and finite offset and resolution of the comparator                                        | 67 |

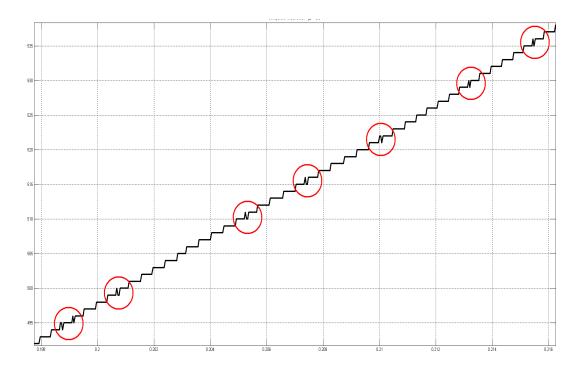

| Figure 4.15 Glitches in the ADC I/O caused by the comparator's offset                          | 68 |

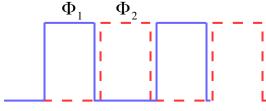

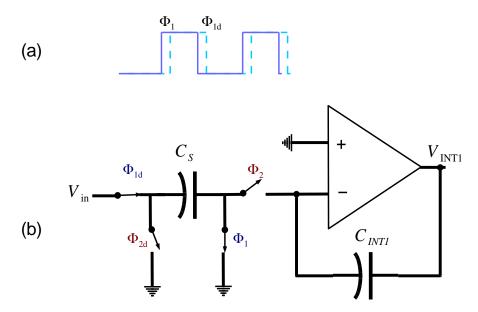

| Figure 5.1 Non-overlapping clocks                                                              | 71 |

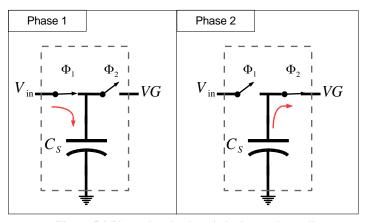

| Figure 5.2 Phases in a basic switched capacitor cell                                           | 72 |

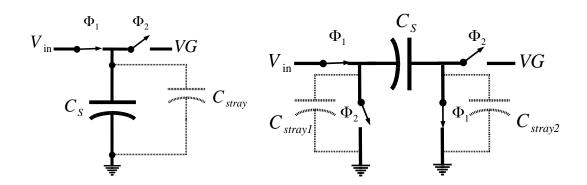

| Figure 5.3 Stray capacitances in a simple SC cell (left) and in a stray-insensitive SC cell    |    |

| (right)                                                                                        | 72 |

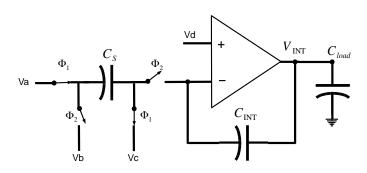

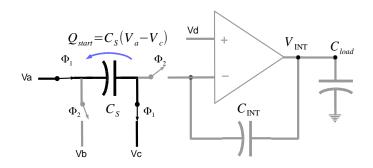

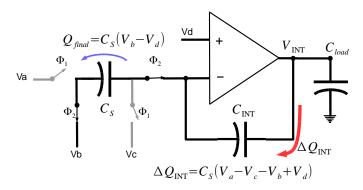

| Figure 5.4 SC integrator                                                                       | 73 |

| Figure 5.5 SC integrator: sampling phase (phase 1)                                             | 74 |

| Figure 5.6 SC integrator: integrating phase (phase 2)                                          | 74 |

| Figure 5.7 Negative spikes - caused by inability of <i>Csample</i> to instantaneously release  |    |

| its charge - increase minimum SR specification                                                 | 76 |

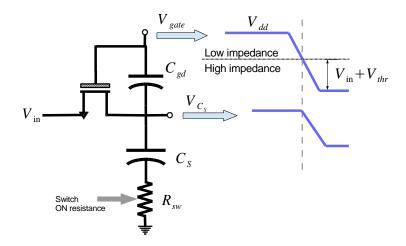

| Figure 5.8 Clock feed-through: qualitative visualization in the case of slow clock             |    |

| transition                                                                                     | 78 |

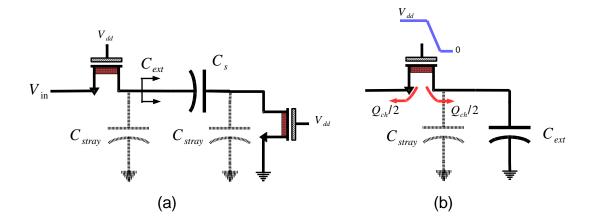

| Figure 5.9 MOSFET switches connected to the sampling capacitance with channel charge           |    |

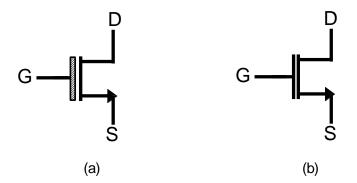

| $Q_{ch}$ in evidence (a) and charge injection to the external capacitance $C_{ext}$ (b)        | 79 |

| Figure 5.10 Delayed clocks for phase 1 (a) and relative connections in a switched              |    |

| capacitor integrator                                                                           | 79 |

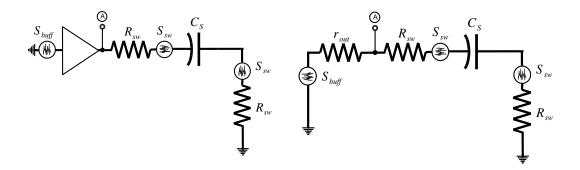

| Figure 5.11 Noise sources during phase 1: ideal buffer (left) and its Thevenin equivalent      |    |

| (right)                                                                                        |    |

| Figure 5.12 Noise sources during phase 2                                                       | 82 |

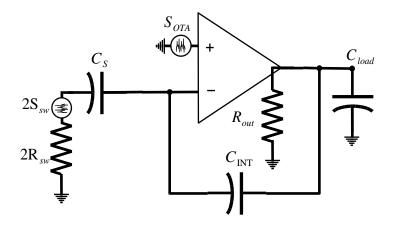

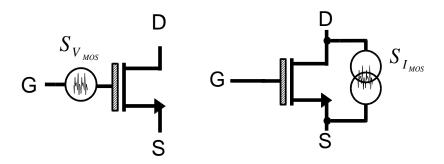

| Figure 6.1 Symbols used for thick oxide, HV MOSFET (a) and thin oxide, LV MOSFET               |    |

| (b)                                                                                            |    |

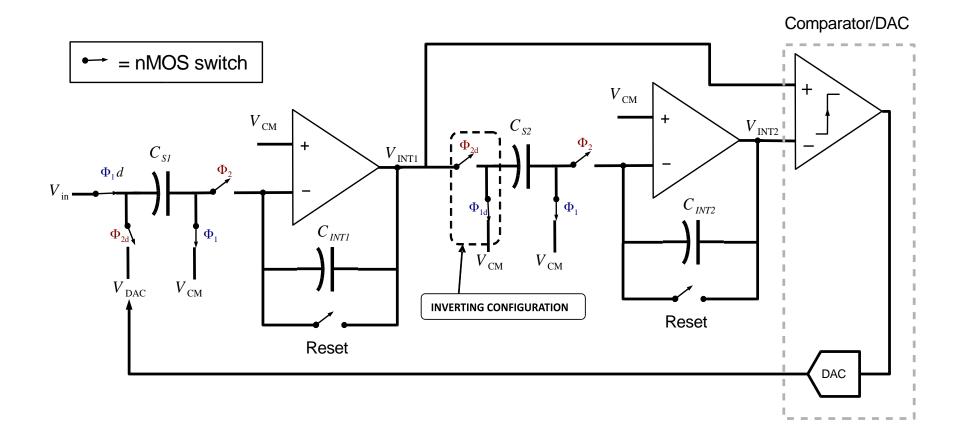

| Figure 6.2 Schematic of the designed Sigma Delta Modulator                                     | 87 |

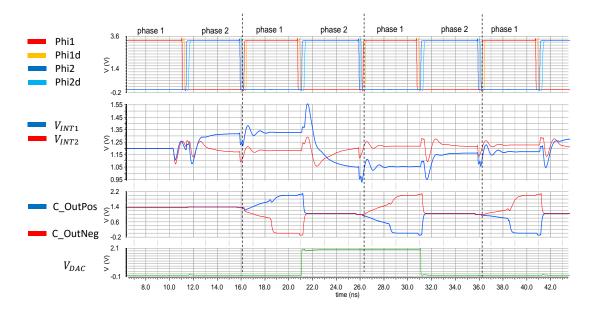

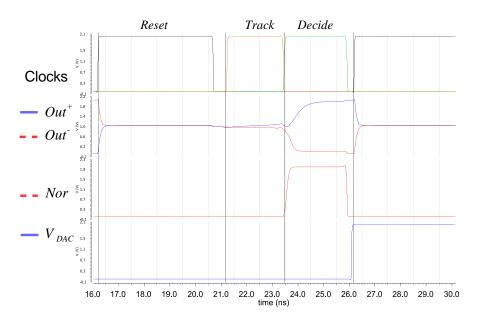

| Figure 6.3 Waveforms of clocks, integrators and comparator's inverting and non inverting       |    |

| outputs in the developed Sigma Delta Modulator                                                 | 88 |

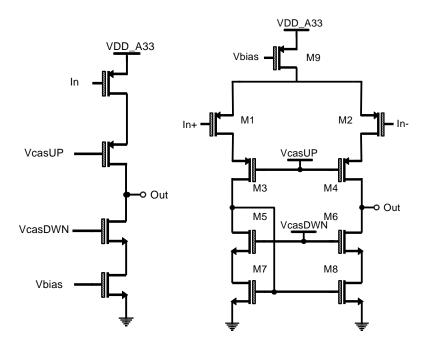

| Figure 6.4 Telescopic cascode OTA: single branch (left) and differential (right)              | 89   |

|-----------------------------------------------------------------------------------------------|------|

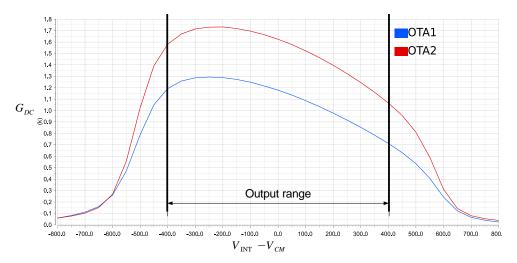

| Figure 6.5 Linear plot of the DC gain of each OTA as a function of its output                 | 92   |

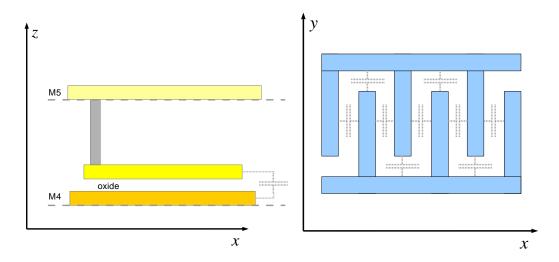

| Figure 6.6 MIM capacitor cross-section (left) and metal-fringe capacitor top view (right) and | 93   |

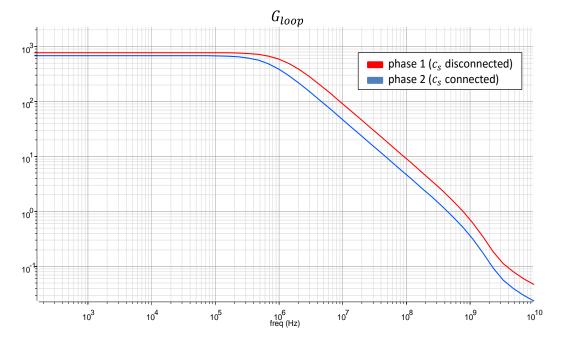

| Figure 6.7 Bode plot of first OTA's loop gain: comparison between phase 1 and phase 2         | 94   |

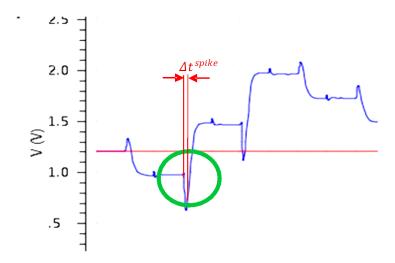

| Figure 6.8 OTA switching and oscillations. The different traces correspond to different       |      |

| process corners; the nominal is in red                                                        | 95   |

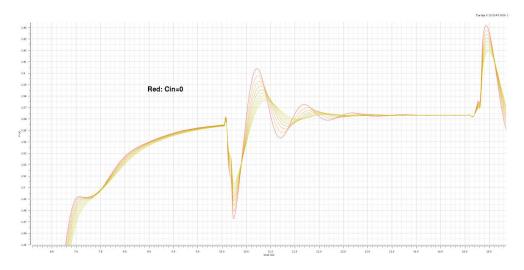

| Figure 6.9 Detail of oscillations after the end of phase 2 for different values of a          |      |

| compensating capacitor $C_{in}$ connected to the input. The red curve corresponds             |      |

| to $C_{in}=0$                                                                                 | 96   |

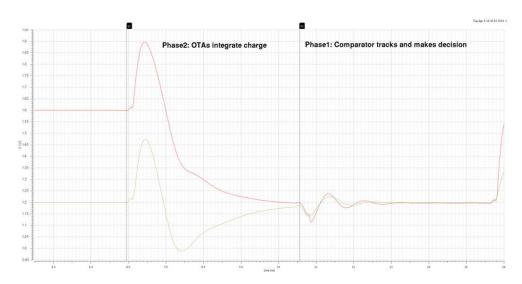

| Figure 6.10 OTAs' outputs coming close together and oscillating after phase 2                 | 96   |

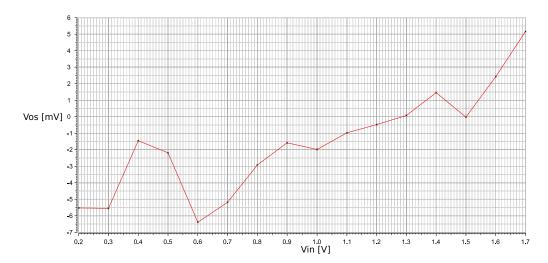

| Figure 6.11 Measured input offset of integrator's first stage as a function of its input (all |      |

| nodes except for the input were kept at the common mode)                                      | 97   |

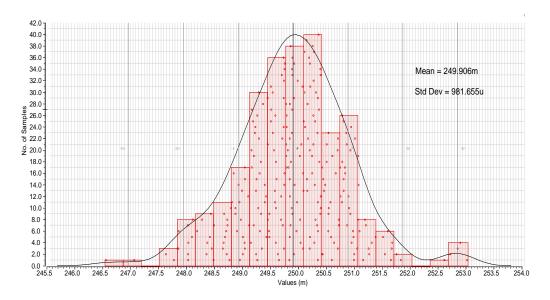

| Figure 6.12 Statistics of measured second stage's integrator gain $g_2$ from Monte Carlo      |      |

| simulations.                                                                                  | 98   |

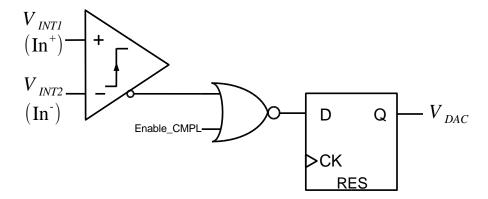

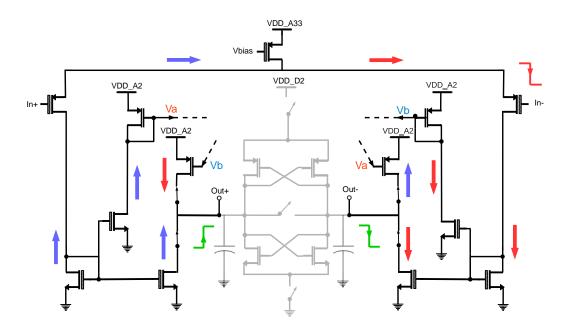

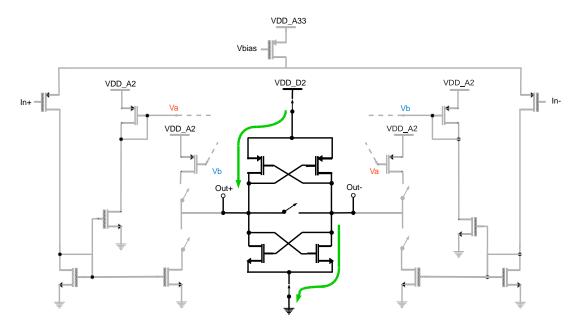

| Figure 6.13 Comparator and DAC buffers                                                        | 99   |

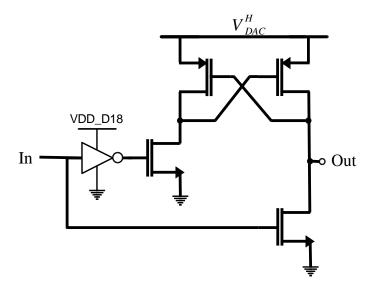

| Figure 6.14 Structure of a level-shifter from VDD_D18 to VDACH                                | 99   |

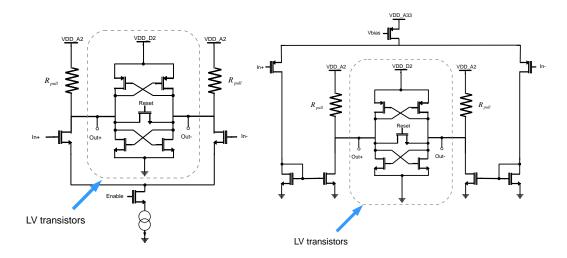

| Figure 6.15 Two ways of connecting the LV transistors to HV transistors                       | 100  |

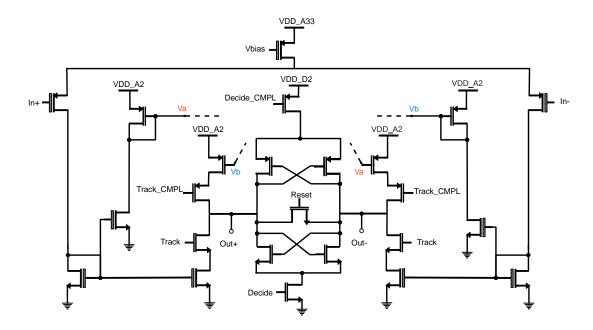

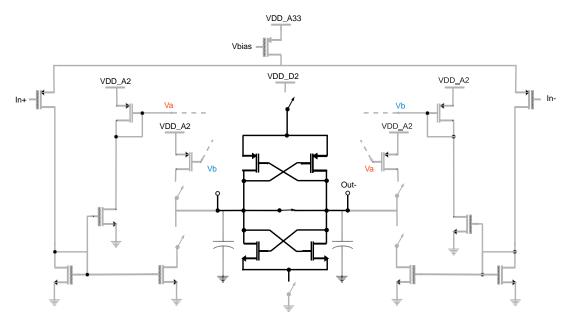

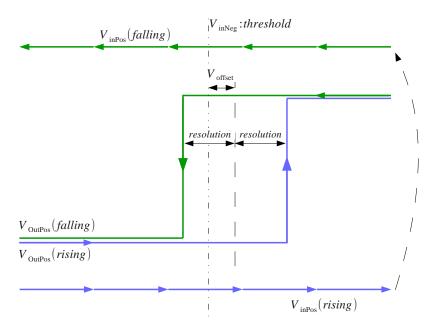

| Figure 6.16 Comparator's configuration. Nodes Va and Vb are connected to the node with        | 1    |

| the same name. Signals Track_CMPL and Decide_CMPL are the inversion of                        |      |

| Track and Decide, respectively                                                                | 101  |

| Figure 6.17 Phases and operation of the comparator                                            | 102  |

| Figure 6.18 Reset phase                                                                       | 102  |

| Figure 6.19 Track phase                                                                       | 103  |

| Figure 6.20 Reset phase                                                                       | 103  |

| Figure 6.21 Diagram of measurement of comparator's offset and resolution                      | 104  |

| Figure 7.1 Schematic of the timing signal generator. To the left, the four flop flops that    |      |

| synchronize the reset and generate signals R, RD, R2 and their complements.                   |      |

| To the bottom, R is level-shifted to 3.3V to drive the non-overlapping clocks                 |      |

| generator with outputs Phi1, Phi1d, Phi2, Phi2d. To the right, three delay                    |      |

| chains are used for the comparator clocks to make their phases match the                      |      |

| delay of the non-overlapping clocks generator.                                                | 107  |

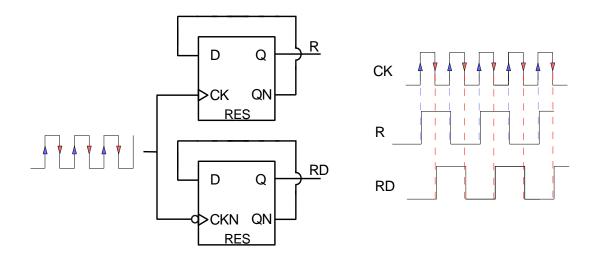

| Figure 7.2 Toggle flip flops and their output waveforms                                       | 108  |

| Figure 7.3 Generation of Reset, Track and Decide signals using phase-shifted signals R        |      |

| and RD.                                                                                       |      |

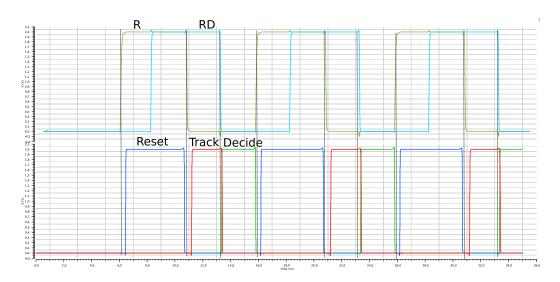

| Figure 7.4 Non overlapping clock generator - core                                             |      |

| Figure 7.5 Non-overlapping clocks generator: multiplexer stage for Phi1 and Phi1d             |      |

| Figure 7.6 Signals Phi1, Phi1d, Phi2, Phi2d in the four selectable options                    | 111  |

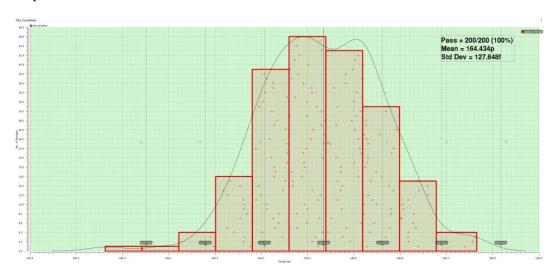

| Figure 7.7 Monte Carlo simulation measuring the delay between the falling edge of             |      |

| Decide signal and rising edge of Reset. The extracted standard deviation,                     |      |

| 128fs, is several orders of magnitude lower than the delay between the edges.                 |      |

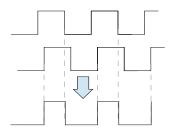

| Figure 7.8 Shrinking the duty cycle with a delay and a AND gate                               | 112  |

| Figure 7.9 Decimator block diagram (top) and detail of adder blocks (bottom). HA              |      |

| denotes a half adder, FA a full adder                                                         |      |

| Figure 7.10 ADC area specification and position of developed ADC (including all blocks)       | )114 |

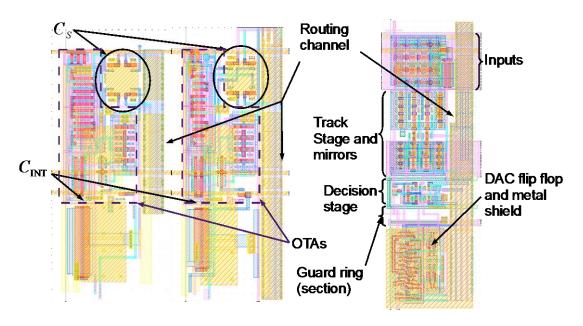

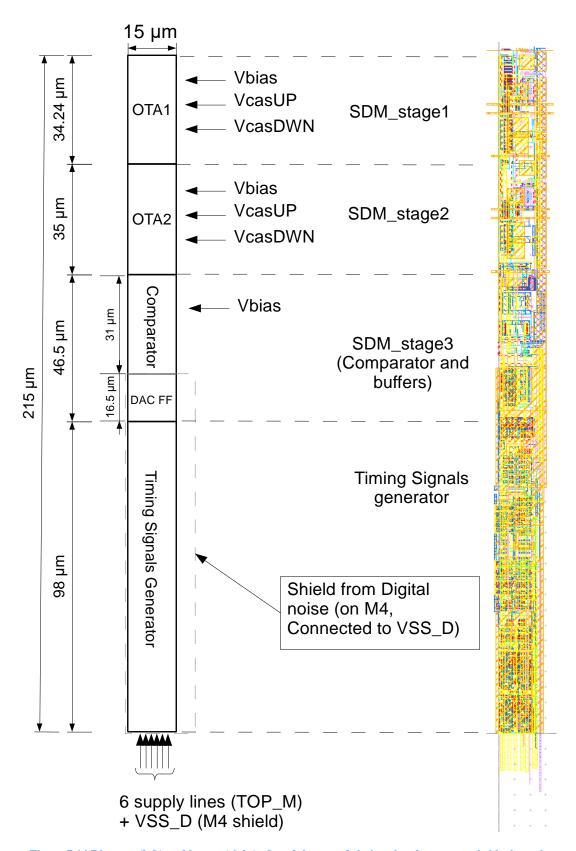

| Figure 7.11 Layout of the three modulator's blocks. From left to right, shown is the first |     |

|--------------------------------------------------------------------------------------------|-----|

| switched capacitor stage, the second switched capacitor stage and the                      |     |

| comparator with buffers                                                                    | 115 |

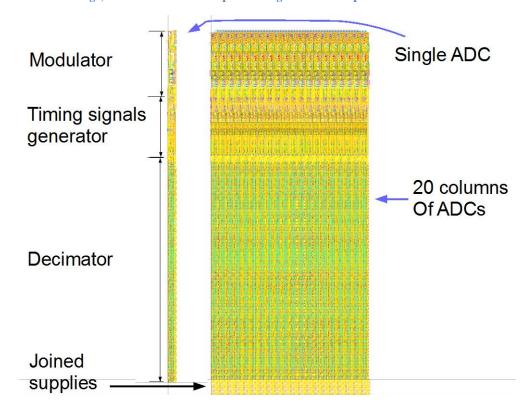

| Figure 7.12 ADC top view. Single ADC (left) and 20 column-parallel ADCs (right)            | 115 |

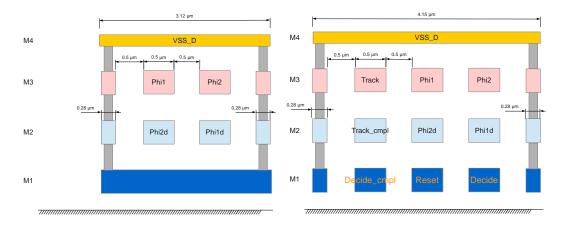

| Figure 7.13 Routing channel cross section. Beside the OTAs (left) and beside the           |     |

| comparator (right)                                                                         | 116 |

| Figure 7.14 Diagram (left) and layout (right) of modulator and timing signals generator's  |     |

| blocks and dimensions – dimensions scaled                                                  | 117 |

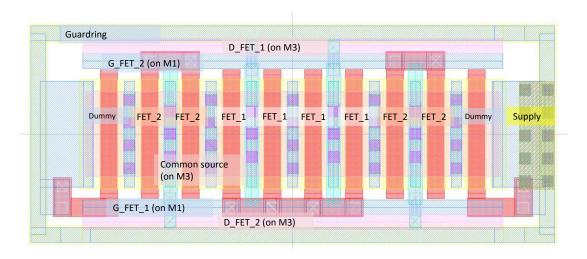

| Figure 7.15 Common centroid of type "AABBBBAA" top view                                    | 118 |

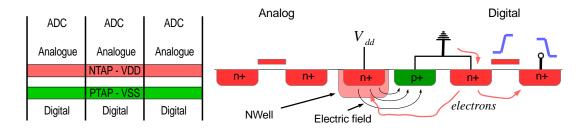

| Figure 7.16 Two arrays of substrate contacts filter the substrate noise towards analogue   |     |

| transistors. Top view (left) and cross-section (right)                                     | 118 |

| Figure 7.17 Test chip layout top view                                                      | 120 |

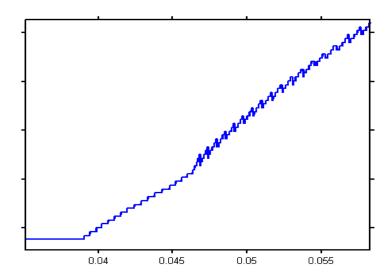

| Figure 8.1 Simulated INL against ADC input. With real nMOS switches (a) and with           |     |

| ideal switches (b)                                                                         | 124 |

| Figure 8.2 Transfer curve near the dead zone at 1/3 of the full scale. Maximum extracted   |     |

| DNL is where shown in figure                                                               | 125 |

| Figure 8.3 Noise performance vs number of cycles M. In (a) the plot is linear and the      |     |

| standard deviation is calculated on the output code; in (b) the plot is bi-                |     |

| logarithmic, and the noise is referred to the input                                        | 126 |

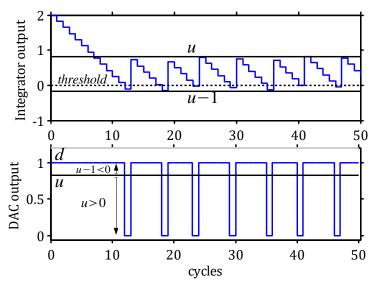

| Figure A.1 Integrator's output gets locked within the range $[u-1, u]$ . In the example,   |     |

| u=0.825                                                                                    | 131 |

| Figure B.1 Series (left) and parallel (right) equivalent noise sources of a MOSFET         | 133 |

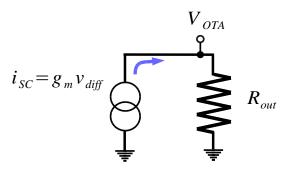

| Figure B.2 Norton theorem applied to the OTA output                                        | 134 |

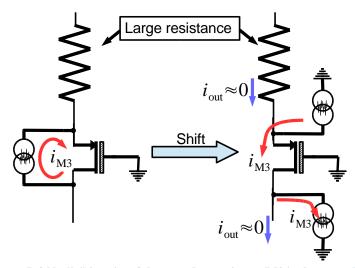

| Figure B.3 Negligible noise of the cascode transistors (M3 in the example)                 | 135 |

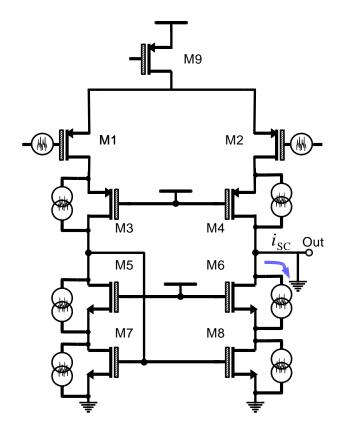

| Figure B.4 OTA noise sources                                                               | 135 |

## **List of Tables**

| Table 2.1 Global specifications of the developed ADC                                 | 35  |

|--------------------------------------------------------------------------------------|-----|

| Table 2.2 Estimated frame-rate (in Hz) achievable with the developed ADC. Comparison | on  |

| between topologies                                                                   | 35  |

| Table 4.1 Comparison between time discrete and time continuous modulators            | 52  |

| Table 4.2 Maximum expected ENOB as a function of the oversampling ratio for differe  | nt  |

| digital filters                                                                      | 58  |

| Table 4.3 Summary of ADC characteristics of operation                                | 63  |

| Table 4.4 Best coefficients for DiFF and InFF architectures                          | 66  |

| Table 4.5 Comparison between the two considered architectures of Sigma-Delta         | 67  |

| Table 4.6 Analogue specifications derived from behavioural simulations               | 69  |

| Table 6.1 Supplies used in the design and blocks supplied                            | 86  |

| Table 6.2 Parameters of the two integrator stages                                    | 93  |

| Table 6.3 Transistors sizes in the two OTAs                                          | 94  |

| Table 6.4 Effect of sampling capacitance on the gain-bandwidth-product and on the    |     |

| OTAs compensation                                                                    | 95  |

| Table 6.5 Transistors' sizes in the comparator                                       | 101 |

| Table 7.1 Outputs of the timing signals generator                                    | 106 |

| Table 7.2 Logical synthesis of the comparator's clocks                               | 109 |

| Table 7.3 Four possible combinations for Phi1 (Phi2) and Phi1d (Phi2d)               | 110 |

| Table 7.4 ADC blocks dimensions                                                      | 116 |

| Table 7.5 List of all splits included in the test chip                               | 119 |

| Table 8.1 Power consumption summary                                                  | 127 |

## **Introduzione**

Il mondo dell'imaging digitale ha visto una crescita stabile negli ultimi anni, con i sensori d'immagine CMOS (CMOS Image Sensors, CIS) alla guida dell'espansione grazie alla loro versatilità e capacità di prestazioni ad alta velocità senza compromettere la qualità dell'immagine. I CIS stanno così diventando la scelta designata per un crescente numero di applicazioni, di tipo industriale - da fotocamere per telefoni cellulari, al campo automobilistico (ad esempio nei cosiddetti Advanced Driver Assistance Systems, "ADAS") e di tipo scientifico (ad esempio in ingegneria aerospaziale, balistica e microscopia). Una costante per tutte queste applicazioni è la richiesta di una sempre maggiore velocità, il che costituisce una stimolante sfida, sia a livello tecnologico che progettuale.

Uno dei componenti chiave nella catena di lettura in un CIS è il convertitore analogico-digitale (Analogue-to-Digital Converter, ADC), la cui rapidità contribuisce a determinare il numero di fotogrammi per secondo (frame-rate) ottenibili dal sensore. Il chip di un CIS può ospitare diversi ADC per permettere una parallelizzazione della lettura (ossia la conversione dell'informazione di svariati gruppi di pixel in simultanea): la soluzione più comunemente adottata è la topologia a "colonne parallele" (column-parallel), con un ADC assegnato a ciascuna colonna della matrice di pixel del sensore.

In aggiunta ai requisiti sull'alta velocità di conversione, le principali specifiche di un ADC per sensori d'immagine riguardano basso rumore, dimensioni ridotte e un contenuto mismatch tra le prestazioni dei diversi ADC. Rispettare questi vincoli è una sfida, poiché migliorare uno di questi aspetti (ad esempio velocità di conversione e contenimento del mismatch) porta spesso al peggioramento di un altro (ad esempio rumore e dimensioni).

Gli ADC Sigma-Delta ( $\Sigma\Delta$ ) sono una promettente soluzione per il superamento di questi limiti. Nonostante la loro applicazione nell'ambito dei sensori d'immagine sia stata suggerita sin dal 1997 [1], questi convertitori hanno iniziato ad attirare l'interesse della comunità dell'imaging solo in tempi recenti, dopo essere stati utilizzati tradizionalmente in altre applicazioni - quali ad esempio quelle del mondo audio.

I  $\Sigma\Delta$  sfruttano una ben nota proprietà degli anelli di retroazione, ovverosia il fatto che non idealità introdotte nel cammino di andata dell'anello – come mismatch e distorsione – hanno un impatto ridotto sul trasferimento complessivo, poiché il segnale è per la maggior parte trasferito nel cammino di retroazione. I  $\Sigma\Delta$  ADC applicano questo concetto in un sistema misto analogico-digitale, dove il percorso d'andata è completamente analogico mentre l'uscita ed il percorso di retroazione sono quantizzati: la loro peculiare architettura e l'uso di

oversampling (il campionamento dell'ingresso ad una frequenza maggiore della minima necessaria) permettono di operare conversioni in grado di dare la risoluzione desiderata, ottenendo allo stesso tempo basso rumore e buona tolleranza alle variazioni di processo senza rinunciare alle ridotte dimensioni.

-----

Il presente lavoro di tesi descrive il progetto di un ADC  $\Sigma\Delta$  per sensori column-parallel, in grado di dare 12 bits di risoluzione nel competitivo tempo di conversione di  $1\mu s$ . Il sistema è stato realizzato nella tecnologia TowerJazz  $0.18\mu m$  per CIS. È stato progettato all'interno del CMOS Sensor Design Group al Rutherford Appleton Laboratory, in Harwell (Oxfordshire), dove vengono realizzati CIS e sensori di radiazione a basso rumore allo stato dell'arte per applicazioni in ambito scientifico.

-----

Questo lavoro è suddiviso in otto capitoli, come di seguito riepilogato.

Nel Capitolo 1 sono descritti i fondamenti dell'operazione di un sensore d'immagine CMOS. L'esposizione degli argomenti in questo capitolo è indirizzata ad aspetti che verranno richiamati nelle successive discussioni riguardanti il progetto dell'ADC.

Il Capitolo 2 tratta gli ADC in generale ed in relazione al frame-rate del sensore. A partire da una revisione delle principali figure di merito degli ADC, si passa ad una esposizione delle principali topologie di readout in un CIS, spiegando in che modo migliorino le prestazioni del sensore. Successivamente, vengono analizzati i trade-off più rilevanti negli ADC per CIS, evidenziando le ragioni per cui i  $\Sigma\Delta$  promettano di essere un miglioramento rispetto ad altre soluzioni. Il capitolo termina con l'esposizione generale delle specifiche di progetto.

Il Capitolo 3 analizza in dettaglio l'architettura classica di un Sigma-Delta del primo ordine, fornendo le conoscenze necessarie per comprendere le sue principali caratteristiche (ossia oversampling e noise-shaping), il filtraggio del rumore in ingresso ed alcuni problemi di linearità legati a componenti non ideali. Il capitolo introduce peraltro una particolare tipologia di convertitore  $\Sigma\Delta$ , detta Incremental Sigma-Delta (ISD), comunemente utilizzate nei sensori d'immagine CMOS ed è la scelta adottata in questo progetto.

Il Capitolo 4 continua l'analisi dei  $\Sigma\Delta$ , allargando l'orizzonte ad architetture più complesse. Dopo aver descritto diverse possibili soluzioni, vien presentata la scelta finale sull'architettura del convertitore implementato in questo progetto, e vengono elencate le specifiche per i componenti analogici – opportunamente derivate da simulazioni globali del sistema. In particolare, l'architettura scelta per l'ADC è quella di un Incremental Sigma-Delta del  $2^{\circ}$  ordine, che compie 100 cicli per conversione e lavora dunque ad una frequenza di 100MHz.

Il Capitolo 5 è dedicato ai circuiti a capacità commutate: l'obiettivo di questo capitolo è spiegare il principio di funzionamento di tali circuiti e giustificare le formule utilizzate nel capitolo successivo, riguardante la progettazione analogica. Alla luce di quanto qui esposto il lavoro potrà quindi proseguire focalizzando la discussione sul *design flow*.

Il Capitolo 6 tratta la progettazione analogica del sistema, ossia l'implementazione del modulatore del  $\Sigma\Delta$ . Questo blocco è composto da due integratori a capacità commutate ed un comparatore, che costituiscono il cuore dell'operazione del  $\Sigma\Delta$ .

Il Capitolo 7 inizia esaminando il design digitale del decimatore dell'ADC e la sintesi dei clock del sistema, spiegando in particolare le misure prese per garantire la sincronizzazione di segnali con diverse alimentazioni. Si prosegue quindi illustrando il layout dell'ADC e la realizzazione della struttura di test, spiegando come i clock sono distribuiti, come il readout è organizzato e quali variazioni del design dell'ADC sono state aggiunte a scopo di test nel chip e perché.

Il Capitolo 8 conclude la dissertazione presentando i risultati delle simulazioni dell'ADC in termini di non-linearità integrale e differenziale, di rumore in ingresso e di consumo di potenza, evidenziando possibili miglioramenti di design per future implementazioni.

## Introduction

The world of digital imaging has seen a steady growth in the past years, with CMOS Image Sensors (CIS) leading the expansion thanks to their high versatility and their capability to give high speed performance without compromising the image quality. The variety of applications in which CIS are used is increasing, ranging from mobile phone cameras to the automotive field (e.g. Advanced Driver Assistance Systems, "ADAS") and to scientific applications - such as aerospace, ballistics and microscopy. In all of these applications, the demand for ever improving speed performance is a major requirement and challenge.

One of the key components in the readout chain of a CIS is the Analogue-to-Digital Converter (ADC), whose speed directly impacts the achievable frame-rate. A CIS can host several ADCs in order to allow for parallelization of the readout (i.e. the simultaneous conversion of the information from multiple groups of pixels): the most commonly employed solution is the column-parallel topology, with one ADC assigned to each column of the pixel matrix.

In an ADC for image sensors good noise performance, reduced size and contained spread of the converters' performance characteristics are required in addition to high conversion speed. Meeting these specifications is a challenge, since improving one (e.g. conversion speed and limited spread) often leads to a degradation of the other (such as size and noise).

Sigma-Delta ( $\Sigma\Delta$ ) ADCs are a promising solution to overcome these limitations. Despite having been suggested for image sensors as early as 1997 [1], these converters have become of interest to the image sensors community only in recent years: traditionally, this type of ADC had been used in other applications, for example audio.

$\Sigma\Delta$  exploit a well known property of feedback loops, i.e. that non idealities in the direct path, such as spread and distortion, have a low impact on the overall transfer, since the signal is mostly transferred through the feedback path.  $\Sigma\Delta$  ADCs apply this concept in a mixed analogue-digital system, where the direct path is completely analogue whereas the output and the feedback signal are quantized: their peculiar architecture and the use of oversampling (i.e. sampling the input at a frequency higher than the minimum) allow to perform conversions able to provide the desired resolution while achieving at the same time low noise and good tolerance to spread without giving up area efficiency.

-----

This dissertation describes the design of a  $\Sigma\Delta$  ADC for column-parallel image sensors, able to give 12-bits resolution in the competitive conversion time of  $1\mu s$ . The system was realised using TowerJazz 0.18 $\mu m$  process for CMOS Image Sensors. It was designed with the CMOS Sensor Design Group at the Rutherford Appleton Laboratory, in Harwell (Oxfordshire), who design state of the art, low noise CMOS image sensors and radiation detectors intended for scientific applications.

-----

This work is in eight chapters. Chapter 1 describes the fundamentals of operation of CMOS image sensors. The topics reviewed in this chapter target aspects that will be recalled in the following discussions regarding ADC design.

Chapter 2 deals with ADCs in general and their relation to the sensor's frame-rate. It starts with an overview of the main figures-of-merit of ADCs, followed by a review of the main readout topologies in CIS, explaining how they can improve a sensor's performance. Subsequently, the most relevant trade-offs in ADCs for CIS are analysed, providing the argument for why  $\Sigma\Delta$  ADCs promise to be an improvement with respect to other solutions. At the end of the chapter the target specifications of our design will be described.

Chapter 3 analyses the basic Sigma-Delta architecture in depth, providing the reader with the background necessary to understand its main features (i.e. oversampling and noise-shaping), the filtering of input noise and some linearity issues related to non-ideal components. The chapter also introduces a particular type of  $\Sigma\Delta$  converter, called Incremental Sigma-Delta, which is commonly used in CIS and was the adopted solution for this project.

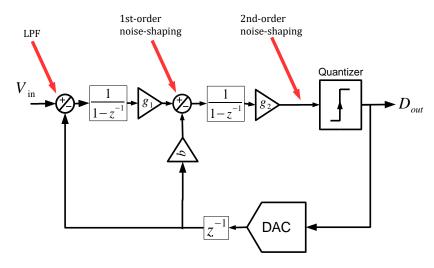

Chapter 4 continues the analysis of  $\Sigma\Delta$  ADCs, expanding the view to complex architectures. After describing and comparing different solutions, the final architecture of the converter implemented in this project is chosen, and the specifications for the analogue components - derived through system-level behavioural simulations – are listed. In particular, the ADC architecture chosen was a  $2^{nd}$  order Incremental Sigma Delta performing 100 cycles per conversion, thus working at a frequency of 100MHz.

Chapter 5 is dedicated to switched capacitor circuits: the purpose of this chapter is explaining the principle of operation of such systems and justifying the formulas that are used in the following analogue design chapter, where the discussion can thus be focused on the design flow.

Chapter 6 deals with the analogue design of the system, i.e. with the implementation of the modulator. This block is composed of two switched capacitors integrators and a comparator, which are the core of the  $\Sigma\Delta$  operation.

Chapter 7, on the other hand, deals in the first part with the digital design of the converter's decimator and with the synthesis of the system clocks, in particular explaining the measures taken to guarantee the synchronization of different signals at different supplies. The second part of this chapter covers the layout of the ADC and the realization of the test structure, explaining how the clocks are distributed, how the readout is organized and which design variations of the ADC were added for test purposes and why.

Chapter 8 concludes the dissertation by providing results from simulations of the ADC performance in terms of integral non-linearity, differential non-linearity, input noise and power consumption, and commenting about possible design changes for future improvements.

## **Chapter 1**

## **CMOS Image Sensor basics**

Before starting the discussion regarding Analogue-to-Digital Converters (ADCs) for CMOS image sensors, it is convenient to introduce the fundamentals of operation of the sensor itself. This chapter provides a brief description of a basic pixel in a CMOS image sensor and some of the most relevant noise sources in it. The topics reviewed in this chapter target aspects that will be recalled in the following discussions regarding ADC design.

### 1.1 Principle of operation

Figure 1.1 shows the basic architecture of an active pixel, employing three transistors. It works in three phases, whose diagram is shown in Figure 1.2:

- Reset: the voltage across the photodiode  $V_{PD}$  is brought to  $V_{reset}$ .

- Light integration: the light shining on the photodiode generates electron-hole pairs at a rate proportional to the incoming photon rate; each carrier will drift to the point of lower potential energy (ground for holes and the photodiode n-well for electrons), thus generating a current which gradually discharges the capacitance  $C_{PD}$  (which includes the photodiode's inversion capacitance, the gate capacitance of M2 and all other parasitic capacitances).

Figure 1.1 Basic architecture of a 3-transistors pixel

Figure 1.2 Time diagram of a pixel operation

• Column readout: the switch Row\_Select connects the source of M2 to the column bias current; M2 will hence turn on, acting as a source follower and buffering  $V_{PD}$  (offset by the threshold voltage  $V_{thr}$  of M2) to the column line. Here, the buffered voltage  $V_{col}$  will be sampled on a capacitor which will hold the information for the readout while the pixel is reset once again.

### 1.1.1 Non-linearity

The charge generated in the photodiode during the light integration phase is proportional to the incoming radiation intensity and the integration time  $T_{int}$ . However, the value read out of an active pixel is the voltage across the reverse-biased p-n junction, and its relation with the collected charge is — within reasonable approximation - quadratic rather than linear, as shown in Eq. (1.1): this is due to the fixed spatial charge in the junction's depleted region.

$$V_{PD} = -V_{bi} + \frac{(Q_{dep} - Q_{ph})^2}{A^2 \cdot 2q\varepsilon_{Si}N_A}$$

(1.1)

In Eq. (1.1)  $V_{bi}$  is the built-in potential across the junction,  $Q_{dep}$  the charge in the depleted region after reset,  $Q_{ph}$  the photo-generated charge, A the effective photosensitive area of the pixel, q is the charge of the electron,  $\varepsilon_{Si}$  the electric permeability of silicon and  $N_A$  the acceptor doping of the substrate.

As a consequence of the photodiode's voltage-charge relation, the bottleneck of an imager's linearity is often the pixel itself, thus loose requirements with respect to this specification are allowed for other components in the readout chain.

### 1.1.2 Full well and dynamic range

The photodiode can only retain a finite amount of charge in its n-well before becoming forward biased and saturating, which is normally referred to as the "full well". This parameter is key to the sensor's dynamic range, i.e. the ratio between the maximum and the minimum measurable, which for a pixel can be given by the ratio between the full well and the minimum noise.

### 1.2 Noise contributions

This section will review some of the main noise sources in a pixel: shot noise, reset noise and fixed pattern noise. The topics are limited to those that are relevant for the following discussions; other types of noise, such as 1/f and Fano noise are not mentioned although their contribution might be significant - especially 1/f. These are all treated in depth in [2].

### 1.2.1 Shot noise

Shot noise is associated to single events – such as the arrival of a photon - occurring at a certain rate. This type of process is described by Poisson statistics, and the main result is that the variance of the number of incoming photons is equal to their mean value:

$$\sigma_{N_{ph}}^2 = N_{ph} \tag{1.2}$$

Therefore, even if the number of incoming photons  $N_{ph}$  during the integration time  $T_{int}$  was measured with extreme precision, the associated photon rate  $r_{ph} = N_{ph}/T_{int}$  would still have some uncertainty: it is in fact possible that the light source intensity was higher (or lower) and just happened to emit a low (or high) amount of photons in the finite measurement time. The noise variance of the light source emission rate is thus:

$$\sigma_{r_{ph}}^2 = \frac{r_{ph}}{T_{int}} \tag{1.3}$$

A consequence of the proportionality between noise power and signal magnitude shown in Eq. (1.3) is that, for large input signals, the dominant source of noise will be shot noise.

Shot noise is also introduced by the photodiode's leakage current, which is caused by thermal generation of carriers; this noise is significant for low signal, thus contributing to the pixel's minimum readout noise.

#### 1.2.2 Reset noise

When the switch resetting the photodiode is on, its finite resistance introduces thermal noise, thus causing a fluctuation of the charge stored on the photodiode. Every time the switch is turned off, this noise charge will remain sampled on the photodiode and be read out together with the signal. This contribution is generally referred to as reset or kTC noise.

The variance of reset noise depends on the total capacitance  $C_{PD}$  connected to node  $V_{PD}$ , according to Eq. (1.4). This formula will not be derived here: we refer instead to Chapter 5.7, where the impact of white noise sampled on capacitors (of which reset noise is a special case) is treated in depth.

$$\sigma_0^2 = kTC_{PD} \tag{1.4}$$

### 1.2.3 Fixed Pattern Noise

Random variations in the chip fabrication process will cause each pixel to have different characteristics and each readout path to have a different offset and conversion gain: this causes fixed pattern noise (FPN). Unlike other noise contributions, FPN affects the transfer in the same way at every readout, and it can hence be strongly reduced by a calibration of the sensor.

### Offset

Offset FPN can be caused for example by the spread of the source follower's threshold voltage and – in chips hosting many ADCs, which will be discussed in Chapter 2.2- the spread of the ADCs input offset. It can be expressed as:

$$\sigma_{FPN-offset}^2 = \sigma_{V_{os}}^2 \cdot \frac{C_{PD}^2}{q^2}$$

(1.5)

In Eq. (1.5),  $\sigma_{FPN-offset}^2$  is the noise variance in electrons,  $\sigma_{V_{os}}$  the standard deviation of the offset in Volts – referred to node  $V_{PD}$  – q the charge of an electron and  $C_{PD}$  the total capacitance at node  $V_{PD}$ .

### Gain

Some sources of gain FPN are variations in the pixels sensitivity (such as its charge collection efficiency) and in the conversion gain of each stage of transduction of the signal, e.g. the LSB of the ADCs. The variance of such contribution is proportional to the square of the signal:

$$\sigma_{FPN-gain}^2 = \sigma_G^2 \cdot \eta \cdot N_{ph} \tag{1.6}$$

In Eq. (1.6)  $\sigma_{FPN-gain}^2$  is the noise variance in electrons,  $\sigma_G^2$  the variance of the gain,  $\eta$  the quantum efficiency and  $N_{ph}$  the number of photons arrived at the pixel.

## **Chapter 2**

# Analogue-to-Digital-Converters for image sensors

The aim of this chapter is to introduce the reader to Analogue-to-Digital Converters (ADC) for image sensor applications, outlining typical topologies that are employed in imagers and the typical requirements and trade-offs in their design. After this overview, the purpose of the project depicted in this dissertation and the specifications for the ADC developed will be explained.

### 2.1 ADCs figures of merit

Before entering the discussion about digital converter architectures and readout, it is important to review the main figures of merit of Analogue-to-Digital Converters (ADC).

An ADC is the interface between the analogue world and the digital world in an electronic system: it takes an analogue value at the input and outputs a digital binary number proportional to the input level within a fixed scale, the span of which is called full scale range (FSR). The main instrument to assess its operation is the transfer characteristic, or transfer curve, which plots the output code as a function of the input. The transfer curve of an ideal ADC is shown in Figure 2.1: the interval between two successive transitions is called the least-significant-bit<sup>1</sup> (LSB) of the ADC, since it corresponds to an increment of  $2^0 = 1$  in the digital output.

<sup>&</sup>lt;sup>1</sup> This term is a bit ambiguous since it refers to a bit but, rather than being a non-dimensional number, it is measured with the same units as the input; for this reason it is sometimes replaced by the term analog-to-digital-unit, ADU.

Figure 2.1 Trans-characteristic of an ideal ADC with 3 bits of resolution

Real ADCs however will suffer from some imperfections due to the complex nature of the electronic components that constitute them. Their transfer curves will be qualitatively similar to that in Figure 2.2, where the width of each step changes along the scale. The approximation of the input to a digital value (i.e. its quantisation) thus won't be optimal for a given number of coding bits. Several figures of merit exist to express quantitatively the conversion quality of an ADC: the main ones are the effective number of bits (ENOB), differential non linearity (DNL) and integral non linearity (INL).

Figure 2.2 Transfer curve of an ADC with INL and DNL in evidence

### 2.1.1 ENOB

The effective number of bits (ENOB) is the number of bits that an ideal ADC would have to give the same overall signal-to-noise (SNR) of the real ADC, including all the performance-degrading contributions, such as electronic noise, harmonic distortion and quantization error [3].

Given the peculiar nature of quantisation noise, which is correlated to the signal, it is not trivial to consider its contribution together with other non-idealities. Hence, for simplicity in

many cases only the quantisation noise is considered when assessing the ENOB, i.e. only the signal-to-quantisation-noise (SQNR) is calculated. In this dissertation, this is the procedure considered.

For an ideal ADC, a typical assumption is to consider the quantisation error to be uniformly distributed in an interval [-LSB/2, LSB/2], thus having a standard deviation:

$$\sigma_Q^2 = \frac{LSB^2}{12} \tag{2.1}$$

For a real ADC with a DC input, the ENOB can thus be calculated as the number of bits for which the measured *rms* of the quantization error equals that of an ideal ADC:

$$2^{ENOB} = \frac{\Delta V_{in}}{LSB_{id}} = \frac{\Delta V_{in}}{\sigma_O \cdot \sqrt{12}}$$

(2.2)

#### 2.1.2 DNL

Differential non linearity (DNL) is the difference between the actual step width and the LSB, normalised to the LSB (see Figure 2.2).

It can happen that a code is skipped in the trans-characteristic (this case is normally referred to as missing code): in this case, DNL=-1.

### 2.1.3 INL

Integral non linearity (INL) for a certain output code is measured as the difference between the inputs of a real ADC and an ideal ADC which give a transition to the same code in the transfer curve (see Figure 2.2). It is also usually measured in LSBs, although sometimes it is expressed as a percentage of the full scale.

For practicality of the measurement, the transfer curve of the ideal ADC is sometimes replaced with the best fitting straight line or with an endpoint line (i.e. a straight line connecting the first and last points of the transfer curve). In this dissertation the latter method is used.

If INL is defined as a deviation from the endpoint line, then INL at the  $k^{th}$  code is the integral of the DNL of all codes up to k.

### 2.2 Readout topologies for fast imagers

### 2.2.1 Frame rate versus conversion and readout time

The frame time of a camera depends on the conversion time of all the analog pixel values into digital numbers  $(T_{conv})$  and the time needed to readout all the resulting bits,  $(T_{RdOut})$ . The time to obtain a whole frame  $T_{frame}$  is a combination of these two times: if the two operations are performed in series (see Figure 2.3 (a)) then  $T_{frame} = T_{conv} + T_{RdOut}$ ; if they are performed in parallel (see Figure 2.3 (b)), then  $T_{frame} = \max(T_{conv}, T_{RdOut})$ . In the following discussion the former of the two relations will be used. Note that the time between the selection of a row and the complete settling of the pixel's output voltage is

being neglected: while it is, in practice, comparable to the other times  $T_{conv}$  and  $T_{RdOut}$ , it is in our interest to simplify the analysis and leave the focus entirely on the data conversion and readout.

Figure 2.3 Pixel readout time diagrams. Conversion and readout operated in series (a) and conversion and readout operated in parallel (b)

The expressions for  $T_{conv}$  and  $T_{RdOut}$  are [4]:

$$T_{conv} = b \cdot T_{ADC} \tag{2.3}$$

$$T_{RdOut} = N_R \cdot N_C \cdot \frac{n_{bits}}{n_{parallel}} \cdot \tau_{bitOut}$$

(2.4)

In Eqs. (2.3)-(2.4)  $N_R$  and  $N_C$  are the number of rows and columns respectively,  $n_{bits}$  the number of bits of one digitally converted value,  $n_{parallel}$  the number of bits that can be read out at the same time and b is a "burden" factor, defined as the number of pixels assigned to one ADC;  $\tau_{bitOut}$  is the time necessary to deliver one bit to the output, whereas  $T_{ADC}$  is the conversion time of one ADC.

$T_{conv}$  is usually dominant compared to  $T_{RdOut}$ , which constitutes a lower limit for  $T_{frame}$ , since the former typically entails delicate analogue operations whereas the latter simply represents the streaming of digital information. For this reason, the majority of design efforts are addressed towards reducing  $T_{conv}$  by working on both the burden factor b and the ADC latency  $T_{ADC}$ . The former is reduced by employing highly-parallelized topologies - some of which will be described in this section - while the latter by adopting smart and fast architectures for the ADC: the most commonly used options will be discussed in Section 2.3.

The basic conversion topology for CMOS image sensors employs only one ADC in the whole chip, converting the pixel outputs one by one. While there are clear advantages from a design point of view in terms of area budget and FPN, the achievable frame rate is heavily limited by the lack of parallelization: the ADC has to carry the burden of converting all the pixels in the chip in a serial way. For this topology, following Eqs. (2.3)-(2.4), we therefore have:

$$b = N_D \cdot N_C \tag{2.5}$$

$$T_{frame} = N_R \cdot N_C \cdot \left( T_{ADC} + \frac{n_{bits}}{n_{parallel}} \cdot \tau_{bitOut} \right)$$

(2.6)

In order to reach higher frame rates without trading off image resolution it is necessary to resort to topologies with higher parallelism, i.e. with many converters on the chip, each one having only a few pixels assigned to it. However, as it is often the case when increasing the speed of an electronic system, these topologies also give power dissipation and area occupation issues. A particular case where there is a trade-off between area and  $T_{conv}$  is the stacked chip sensor, which will be examined in Section 2.2.3. Moreover, FPN could increase due to statistical spread in parameters of the ADCs (such as offset and conversion gain), which may therefore require inconvenient calibrations.

The main topologies used for fast readout will now be overviewed: these are the column-parallel, stacked chip and in-pixel ADC topologies.

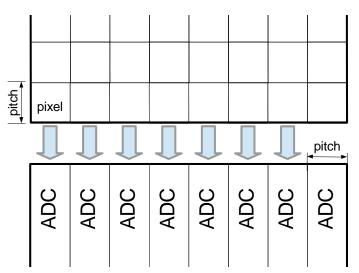

### 2.2.2 Column-parallel

In this topology, the sensor has  $N_C$  ADCs, each one assigned to one column of the pixel matrix, as shown in Figure 2.4 (although sometimes one column has assigned even more than one ADC). The burden factor and  $T_{frame}$  are thus, respectively:

$$b = N_{\rm p} \tag{2.7}$$

$$T_{frame} = N_R \cdot \left( T_{ADC} + N_C \cdot \frac{n_{bits}}{n_{parallel}} \cdot \tau_{bitOut} \right)$$

(2.8)

Column parallel image sensors are very commonly used, since they give a good compromise between routing simplicity, contained FPN and speed.

Figure 2.4 Column parallel architecture diagram

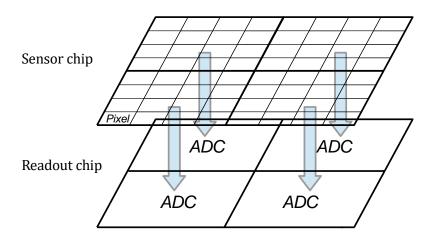

### 2.2.3 Stacked chip

A further step towards parallelisation is assigning a small group of pixels to one ADC: one way to make this possible is having two separate chips, one for the light-to-charge transduction and one for the readout: the former would be sitting on top of the latter, and the two would be connected with through-silicon vias (TSV). Figure 2.5 provides a visual understanding of the concept.

The technological challenges related to the process made the implementation of such a topology problematic until relatively recent years. However, this technology has now been employed in some commercial image sensors [5].

In this case we have:

$$b = \frac{N_{pixels}}{N_{ADC}} = \frac{Area_{ADC}}{Area_{pixel}}$$

(2.9)

$$T_{frame} = \frac{N_{pixels}}{N_{ADC}} \cdot T_{ADC} + N_R \cdot N_C \cdot \frac{n_{bits}}{n_{parallel}} \cdot \tau_{bitOut}$$

(2.10)

Combining Eqs (2.9)-(2.10) it can be shown that there is an inherent trade off between ADC area and conversion time, given by the fact that a large ADC would have more pixels to convert per frame (since there would be many of them lying on top of it), thus would need to be faster to achieve the same frame rate. This is expressed quantitatively in Eq. (2.11), where for simplicity it was considered  $\tau_{bitOut} \sim 0$ .

$$Area_{ADC} \cdot T_{ADC} = Area_{pixel} \cdot T_{frame}$$

(2.11)

Note that this is not the case for the column parallel topology where, while the pitch has to match the pixel's width, the ADC length could in principle be un-constrained.

Figure 2.5 Conceptual illustration of a stacked chip

### 2.2.4 Pixel-level ADC

The ultimate step in terms of parallelisation is when each pixel can rely on one ADC for the conversion: in this case, the dominant factor in  $T_{frame}$  is more likely to be the readout time. We have:

$$b = 1 \tag{2.12}$$

$$T_{frame} = T_{ADC} + N_R \cdot N_C \cdot \frac{n_{bits}}{n_{parallel}} \cdot \tau_{bitOut}$$

(2.13)

This solution has however several drawbacks: firstly, the displacement of charge in the substrate due to the operation of the ADC could interfere with the pixel's activity; secondly, it reduces the fill factor of the pixel (the ratio between active photodiode area and overall pixel area, comprising of circuitry) and, consequently, its sensitivity; lastly, the necessity to bring out an  $n_{bits}$  output for each pixel substantially complicates the layout of the routing, which can also potentially disturb the activity of the pixels. Despite these challenges, ADCs of this kind have been realised [6] and used in commercial sensors [7].

An interesting point can be made regarding the development of pixel-level Sigma-Delta ADCs. These ADCs need an analogue integrator to perform the conversion: in a pixel, the photodiode itself integrates the light intensity shining on it; therefore, ADCs of this kind could be realised inside the pixel, and the converted signal could be the light directly shining on the pixel rather than its output voltage. Moreover, in this sensor the negative feedback necessary for Sigma-Delta operation would be given by packets of charge partially resetting the photodiode: this would enable the pixel to receive more signal than its full well, thus effectively increasing the dynamic range [8].

### 2.3 Trade-offs in ADC architectures for image sensors

The discussion in Section 2.2 showed that to achieve high throughput the chip needs to host a large number of ADCs. As a consequence, together with providing a high conversion speed, an ADC for image sensors needs to be able to comply with other important requirements:

- small area occupation

- low spread in parameters (hence low susceptibility to device mismatch)

- low input noise.

The purpose of this paragraph is to analyse how some of the most commonly used ADC architectures for image sensors deal with these constraints and to argue why the converter of the type developed in this project – a Sigma Delta ( $\Sigma\Delta$ ) ADC - promises to be an improvement from this point of view.

The most common architectures used for image sensor converters are ramp, SAR, cyclic, pipeline and Sigma-Delta ADCs [4]: while it is not in the scope of this dissertation to review them all, two of these architectures will now be briefly overviewed by way of example in relation to the constraints listed above: these are ramp and SAR ADCs.

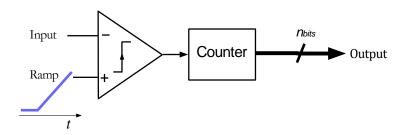

Ramp ADCs (Figure 2.6) use a comparator, a ramp (a voltage source increasing linearly with time) and a counter: the converted value is the output of the counter, given by the time needed by the ramp to overcome the input of the ADC.

In order to obtain an  $n_{bits}$  output,  $2^{n_{bits}}$  clock cycles are necessary; to improve the speed, many image sensors use multiple slope ADCs: in these ADCs, a coarse conversion with a fast ramp defines the first m most significant bits (MSB), which are used to set the offset of the ramp of the following conversion giving the remaining bits.

Despite its long conversion time, this type of ADC is widely used in image sensors thanks to its low area requirement, its simplicity and the predisposition for parallelism: in fact, many ADCs can share the same ramp voltage source, thus eliminating its contribution to FPN. This is not true, however, for most multi-slope architectures, where the spread of misalignment between the coarse conversion ramp and the fine conversion ramp can increase FPN [4].

Figure 2.6 Ramp ADC

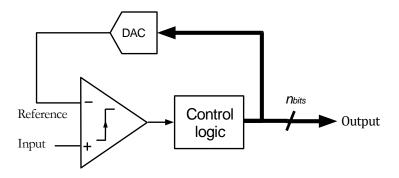

Successive Approximation Register (SAR) ADCs (Figure 2.7), instead, feature a comparator, a  $2^{n_{bits}}$  Digital-to-Analogue converter (DAC) and a digital block for the control logic. The digital output is obtained by a recursive comparison of the input to a variable reference voltage in the following way: after the  $k^{th}$  cycle, the results of the comparisons operated by the comparator form a k-bits binary representation of the ADC input; during cycle k+1 this number is converted to an analogue voltage by the DAC and subsequently compared to the input to obtain the following the  $(k+1)^{th}$  bit. Therefore, at each cycle one bit of resolution is added and only  $n_{bits}$  clock cycles are necessary to complete a conversion.

Their characteristics are complementary to a ramp ADC: they are significantly faster but have higher spread due to the unavoidable mismatches in the DAC components; furthermore, reducing the spread usually leads to designs of large area (since larger devices statistically have lower relative mismatch), making ADCs of this type hardly area-efficient.

Figure 2.7 SAR ADC

The examples of SAR and ramp ADCs show that there is a trade-off between high conversion speed, limited spread and good area efficiency: SAR ADCs tend to prioritize the speed performance, while ramp ADCs are a good compromise in terms of mismatch and size containment. Furthermore, in both ADCs the low noise constraint requires the comparator to have an input noise of the order of the LSB (the case of SAR ADCs is particularly delicate, since an incorrect firing of the comparator can affect a significant bit if it occurs early in the conversion), which can be a rather strict requirement at large bandwidth.

Sigma Delta ( $\Sigma\Delta$ ) ADCs have the potential to circumvent all of these limitations: as will be thoroughly explained in Chapter 3 and Chapter 4, the impact of the mismatch of most components is strongly reduced by noise shaping; the input noise is reduced thanks to oversampling and is not contributed to by the comparator, which can have very poor noise performance without affecting the conversion; since they don't require a  $2^{n_{bits}}$  DAC, their structure can be fairly simple and their size small with respect to a SAR - although they are not as competitive in terms of speed. Moreover, all of these characteristics make  $\Sigma\Delta$  ADCs suitable to be realized with scaled technologies without compromising their performance.

### 2.4 Purpose of the project

### 2.4.1 Objective

The CMOS Sensor Design Group (CSDG), working at the Rutherford Appleton Laboratory, in Harwell (Oxfordshire) designs state of the art, low noise CMOS image sensors and radiation detectors intended for scientific applications.

The next generation of image sensors will need to be able to achieve high data rates while maintaining good resolution and satisfying increasingly demanding noise requirements: in order to make this happen, the CSDG has decided to follow the image sensor community's increasing interest in  $\Sigma\Delta$  ADCs as components to be employed in the next generation of image sensors, and to investigate the feasibility of an ADC employing this architecture.

The objective of this work is to investigate the main characteristics of  $\Sigma\Delta$  ADCs, assess their feasibility in image sensor applications and lastly, design such a converter and its test chip.

### 2.4.2 Specifications

The ADC would need to be able to give a resolution of at least 12 bits, to have an input equivalent rms noise lower than  $100\mu V$  and to dissipate less than  $330\mu W$ . The specification for DNL was set to  $DNL^{(max)} < 1$ . In terms of integral non-linearity, ADCs for image sensors have generally loose specifications: as explained in Chapter 1 in fact, the main source of non-linearity in an active pixel is the photodiode itself, because of its non-linear charge-voltage relation. As a consequence, relatively high values of integral non-linearity (INL) are tolerated compared to other applications: INL < 0.5%.

FPN can be eliminated through calibration, although this operation can be inefficient in sensors where it is severe. For the ADC developed in this project, no FPN specification was set, but the aim was to implement a converter that would require as little calibration as possible.

### Topology and size-conversion time trade-off

As already stated in Section 2.2, state of the art high data rate imagers mainly employ the column parallel architecture. The quest for ever-increasing frame-rate however, makes it interesting to investigate a different configuration - the stacked chip topology seen in Section 2.2.3. The ADC developed in this project should have characteristics that make it compatible with both solutions, provided changes in layout and routing are applied. It was not designed to be associated with a specific imager: in fact, the objective is to make this ADC a standalone IP block for future development.

To provide some specifications for layout, we will assume that the initial application for this ADC will be a column-parallel sensor with a pitch of  $15\mu m$ . Note that this pitch is larger than that seen in commercial imagers, which can have pixel pitches as low as  $1\mu m$  [9]: the field of applications for which the sensors delivered by the CSDG are intended is in fact scientific, and in this case requirements such as high yield and large full well capacity (i.e. the maximum charge generated by the photodiode before saturating) are more important than area density.

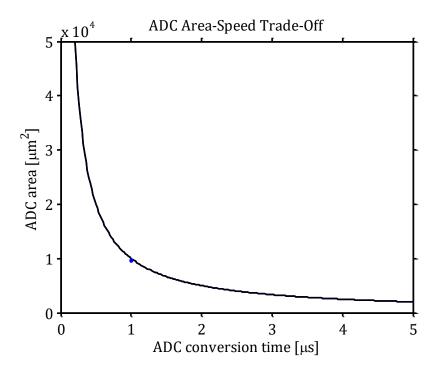

For the ADC to also be compatible with the stacked architecture, it will have to satisfy the constraint in Eq. (2.11): assuming that the performance wanted by the stacked chip is 22.5kfps we get the following area vs  $T_{ADC}$  curve:

Figure 2.8 Trade-off between ADC area and conversion time. As a specification, the point corresponding to the developed ADC has to lie below the curve.

We can see that an area of  $\sim 10000 \mu m^2$  corresponds to  $T_{ADC} = 1 \mu s$ : these values were set as specifications for the converter regardless of the topology adopted. In terms of layout, this would mean that a stacked chip ADC is expected to have a size of  $100 \mu m \times 100 \mu m$ , while a column parallel ADC would be  $15 \mu m \times 670 \mu m$ . The test chip designed for this project adopts the latter of the two topologies.

Number of bits12Conversion time  $T_{ADC}$  $1\mu s$ Maximum DNL1 LSBMaximum INL0.5% or 20 LSBsPower consumption $330\mu W$ Maximum size $10000\mu m^2$  or  $15\mu m \times 670\mu m$

Table 2.1 Global specifications of the developed ADC

### 2.4.3 Expected achievable frame-rate

It is interesting to estimate for each topology what would be the expected frame-rate of a sensor hosting the ADC developed in this project. Table 2.2 provides a comparison between all the alternatives discussed in Section 2.2. The assessments were carried out using Eqs. (2.3) through (2.13), and assuming  $N_R = N_C = 2^{10}$ ,  $Area_{ADC} = 10000 \mu m^2$ ,  $T_{ADC} = 1 \mu s$ ,  $n_{parallel} = 16$ ,  $n_{bits} = 12$  and  $\tau_{bitout} = 1 ns$ . Note that the readout time of the pixel is still being neglected, thus the results given in Table 2.2 should be taken only as approximations.

Table 2.2 Estimated frame-rate (in Hz) achievable with the developed ADC. Comparison between topologies.

| Frame-rate [Hz] | Serial readout | Parallel (pipelined) |  |

|-----------------|----------------|----------------------|--|

| Global ADC      | 0.95           | 0.95                 |  |

| Column parallel | 552            | 977                  |  |

| Stacked chip    | 1204           | 1272                 |  |

| In-pixel ADC    | 1270           | 1272                 |  |

### 2.4.4 Tools used

The ADC was first simulated on Matlab<sup>®</sup> Simulink<sup>®</sup> to study its behavior and to derive system level specifications; it was subsequently designed at schematic level with the assistance of Cadence<sup>®</sup> Virtuoso<sup>®</sup>, using the design kit provided by the foundry TowerJazz<sup>®</sup> for its 0.18µm CMOS image sensors process.

## **Chapter 3 Sigma-Delta ADC basics**

In Chapter 2 we have introduced the reader to the constraints regarding ADCs for image sensors and illustrated the potential of Sigma Delta ADCs in this field. The purpose of this chapter is to provide the background necessary to understand how these ADCs work and what are issues and advantages related to their design.

#### 3.1 Working principle

#### 3.1.1 Structure: modulator and decimator

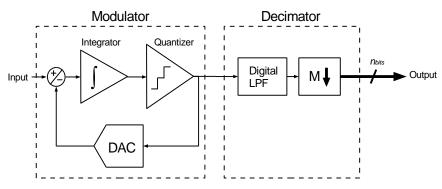

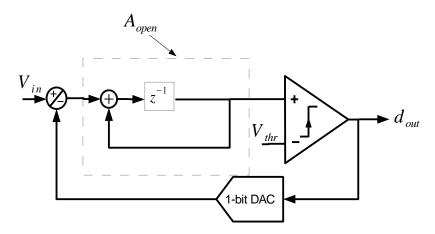

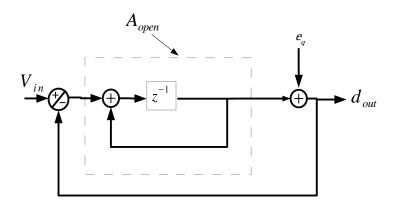

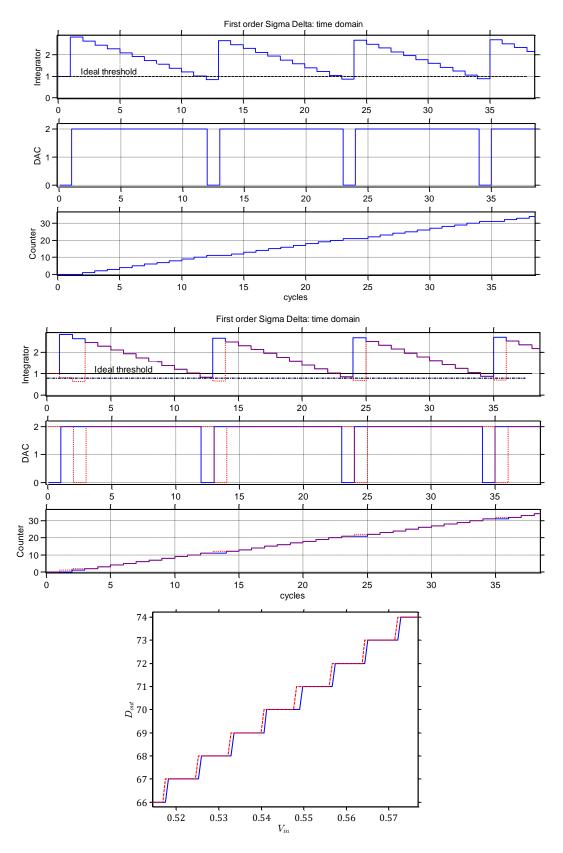

A  $\Sigma\Delta$  ADC is formed by two stages: a modulator and a decimator, as shown in Figure 3.1.

The input is connected to the modulator, which is composed of analogue circuitry and a quantizer (typically a 1-bit quantizer, i.e. a comparator): together, its components form a feedback loop which is essential to the operation of the  $\Sigma\Delta$ . The modulator performs oversampling, i.e. it samples the input at a frequency higher than the desired output sample rate: for DC inputs, this means that the input is sampled more than once. Because of this, the output of the quantizer corresponding to one sample is a continuous stream of bits (or digital numbers if the quantizer has more than one bit).

The output of the modulator is then delivered to the decimator; the role of this block is exploiting the redundancy in the bits to get rid of most of the quantization error and, at the same time, reducing the number of bits to be delivered to the output of the ADC. The simplest example of a decimator is a counter, which averages the continuous input bit-stream producing  $n_{bits}$  at the output. From now on, the decimator will also be referred to as digital low-pass filter (DLPF).

Figure 3.1 General architecture of a Sigma-Delta

Figure 3.2 Block diagram of a basic oversampler (left) and corresponding signal and quantization noise frequency spectrum

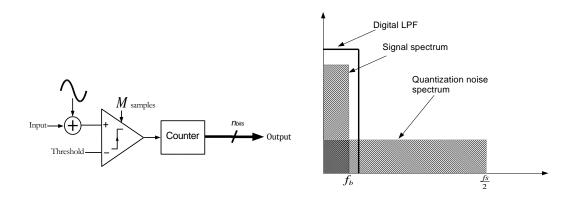

#### 3.1.2 Oversampling - 0th order modulator

It is known that the minimum frequency  $f_s$  at which an analogue signal can be sampled without aliasing is  $f_s = 2f_b$ ,  $f_b$  being the bandwidth of the input (Shannon-Nyquist theorem, [10]). It is moreover intuitive that sampling at a frequency higher than the minimum, despite being useless on its own, can reduce noise from quantization or other sources if the samples in excess are averaged and then discarded – i.e. if a digital low-pass-filter (digital LPF or DLPF) and a decimator are applied. A known example of this is sampling a DC signal to which a dither is added: multiple samples are taken and then averaged to quench the quantization noise  $e_q$  (see the diagram in Figure 3.2).

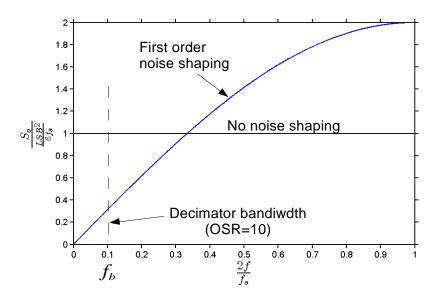

A quantitative assessment of the improvement given by oversampling alone on the resolution of the ADC can be carried out in both frequency and time domain. Arguments of both types can be found in literature (see for example [11] and [12]); in this section, we will use the frequency domain explanation - which lays the ground for the treatment of the other feature of  $\Sigma\Delta$  ADCs, i.e. noise shaping.

Let's consider an ideal ADC with full scale range FSR which operated at the Nyquist limit has a quantization step  $LSB_{Nyq}$ : for example, if a comparator is used, it would have a resolution  $LSB_{Nyq} = FSR/2$ . Our purpose is to study how its resolution can be improved by oversampling.

If the quantization noise is assumed to be uncorrelated to the signal, then the white noise model can be applied: its power spectrum  $S_q$  will be constant throughout the whole frequency range, i.e. from 0Hz until  $f_s/2$  (the maximum frequency containing information associated to a sampled signal). The necessary condition for this approximation to be valid is that the dithering signal magnitude be significantly larger than the quantization steps in the ADC.

Since the quantization error total standard deviation, computed by integrating its power spectrum from 0Hz to  $f_s/2$ , must always be equal to  $LSB_{Nyq}^2/12$ , it has to be that:

$$S_q = \frac{LSB_{Nyq}^2}{12} \cdot \frac{2}{f_s} \tag{3.1}$$

If a digital LPF with cut-off equal to the signal bandwidth  $f_b$  is applied, then the expected standard deviation of the noise will be:

$$(\sigma_q^2)_{OS} = \frac{LSB_{Nyq}^2}{12} \cdot \frac{2f_b}{f_s} = \frac{LSB_{Nyq}^2}{12} \cdot \frac{1}{OSR}$$

(3.2)

hence lower than the usual value  $LSB_{Nyq}^2/12$  by a factor OSR, called oversampling rate, defined as  $OSR = f_s/(2f_b)$ . The SQNR (signal-to-quantization-noise-ratio) will consequently increase by the square root of the same factor. The digital filter can be designed to perform also decimation: the redundant sampled values will be incorporated in one digital number composed of more bits. These numbers are hence the result of a conversion finer than that given by the ADC when sampling at the Nyquist frequency: the effective new LSB,  $LSB_{OSR}$ , will be given by:

$$LSB_{OSR} = LSB_{Nyq} \cdot \sqrt{\frac{\left(\sigma_q^2\right)_{Nyq}}{\left(\sigma_q^2\right)_{OSR}}} = \frac{LSB_{Nyq}}{\sqrt{OSR}}$$

(3.3)

In the case of DC signals, which is the one of interest for the conversion of a pixel output, OSR can equivalently be defined as the number of times M that the input has been sampled. Then:

$$LSB_{OS} = \frac{LSB_{Nyq}}{\sqrt{M}} \tag{3.4}$$

At every doubling of the OSR (or M), half a bit is gained.

#### 3.1.3 Noise shaping

The use of a frequency higher than the minimum does not only cause the noise spectrum to decrease: it also leaves a range of frequencies beyond  $f_b$  where no useful information is contained. A  $\Sigma\Delta$  modulator exploits this fact by shaping the quantization noise power spectrum, concentrating its energy at high frequencies. The in-band power of noise is hence further reduced.