SCUOLA DI INGEGNERIA INDUSTRIALE E DELL'INFORMAZIONE Corso di Laurea Magistrale in Materials Engineering and Nanotechnologies

# VERY LOW CONTACT RESISTANCE FOR GRAPHENE HIGH-FREQUENCY DEVICES

*Author:* LUCA ANZI Supervisor:

ROMAN SORDAN

## Very low contact resistance for graphene high-frequency devices

Luca Anzi

October 2014

# Abstract

Just one atom thick with newest and extraordinary properties, graphene is emerging as a fascinating material for many kind of applications. Thanks to its high carrier mobility at room temperature as well as to its saturation velocity, it reveals a great potential for high speed applications. Moreover it possess the largest heat transfer coefficient which allows better power dissipation. The 2D nature of graphene makes it a good candidate in substituting silicon, for which scaling is becoming problematic due to its intrinsic physical limitations. Because of the lack of a band gap, graphene field effect transistors (GFETs) are actually suitable for radio frequency (RF) applications, where a high power consumption can be acceptable in order to reach larger operational speeds. Despite its unusual properties, the route to large scale production is still long. The more studies on the material are done, the more problems have to be overcome to exploit its real potential. So far several integrated circuits (ICs) based on graphene transistors have been fabricated, but only few of them are able to perform operation at frequencies over 1 GHz. Increase of efficiency could be possible by scaling the dimensions of the IC components. However, once the sizes are reduced to the nanometric scale, the RF performances are deteriorated by the very high resistance of the metal-graphene contacts. Here it is reported a systematic study on the contact resistance including a novel methods for its reduction. This made possible to obtain the smallest value of the contact resistance so far reported in literature which are comparable with that of III-V High Electron Mobility Transistors. This result can open alternative ways to reach higher operational frequencies in graphene devices which today are seriously affected by the poor contact performance.

## Estratto

A cosa serve il Grafene? "Non lo so. É come presentare un pezzo di plastica a un uomo di un secolo fa e chiedergli cosa ci si può fare. Un po' di tutto, penso" Andre Geim premio Nobel per la Fisica 2010.

Sono passati dieci anni dal momento in cui Andre Geim e Kostya Novoselov, riuscirono nell'impresa di isolare il primo materiale bidimensionale della storia: il grafene. Da guel momento una vera e propria corsa all'oro si è sviluppata intorno a quello che è stato definito come "il materiale delle meravigle". Spesso solamente un atomo, il grafene risulta allo stesso tempo flessibile e più resistente dell'acciaio, è otticamente trasparente e possiede una conducibilità termica superiore a gualsiasi altro materiale conosciuto. Ciò che ha portato questo materiale alla ribalta, sono le sue proprietà elettroniche che ne fanno un conduttore migliore del rame. Gli elettroni all'interno del reticolo bidimensionale del grafene si comportano come fermioni di Dirac, ovvero particelle prive di massa. Questo, oltre a permettere mobilità estremamente elevate anche a temperatura ambiente, fa sì che la loro velocità di saturazione sia solamente 300 volte inferiore a quella della luce. Il grafene presenta inoltre un marcato "effetto di campo" necessario per la realizzazione del componente base dell'elettronica moderna: il transistor. Oggigiorno non è facile per un materiale entrare nel mercato dell'elettronica integrata, attualmente dominato dal silicio. D'altro canto la continua riduzione delle dimensioni dei dispositivi sta generando diversi problemi, alcuni dei quali presentano delle barriere fisiche apparentemente insormontabili. Da qualche anno si stanno testando svariati materiali nella speranza di trovare una soluzione al problema della "scalabilità" dei dispositivi. La natura bidimensionale del grafene può spingere l'elettronica oltre guesti limiti e guindi cospicui investimenti nella ricerca sono stati fatti anche da aziende leader nell'industria del silicio.

Benché le premesse siano molto incoraggianti, anche il grafene presenta alcuni problemi. Esso è infatti un semimetallo, ovvero non possiede un gap energetico che separa la banda di valenza da quella di conduzione, aspetto fondamentale per assicurare una buona distinzione tra gli stati di "on" e "off" di un transistor. Questo influenza la sua applicazione nel campo dell'elettronica digitale dove molti transistor vengono combinati per la realizzazione di reti logiche. É invece il campo dell'elettronica analogica in cui il grafene può portare diversi vantaggi. Grazie all'altissima mobilità dei suoi elettroni è teoricamente possibile la creazione di dispositivi con frequenze operative oltre 1 THz . Diversi circuiti analogici più o meno complessi come moltiplicatori di segnale, amplificatori, e oscillatori ad anello sono stati prodotti con transistor in grafene. Tuttavia la loro massima frequenza operativa non supera i pochi GHz. Per poter raggiungere valori più alti una riduzione delle dimensioni caratteristiche dei dispositivi è necessaria. Tuttavia, come per il silicio, effetti cosiddetti "parassitici" pesano sempre di più sul bilancio globale delle prestazioni mano a mano che i transistor vengono scalati. Attualmente la maggior problematica per quanto riguarda i dispositivi in grafene risiede nella difficoltà di "iniezione" ed "estrazione" di cariche attraverso un contatto metallico. All'interfaccia tra i due materiali si genera una cospicua resistenza che limita la massima frequenza raggiungibile dal dispositivo stesso.

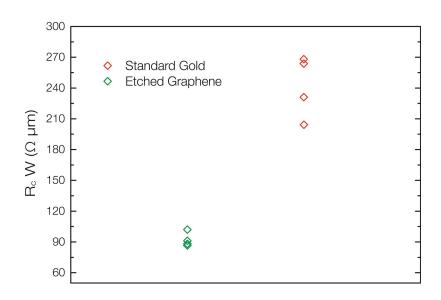

Questo lavoro di tesi si è proposto di analizzare l'interazione metallografene tramite l'estrazione della cosiddetta "resistenza di contatto" [ $R_c$ ]. Come primo step si è definito un processo produttivo standard per le strutture da analizzare, consistenti in un una serie di transistor con differenti lunghezze di canale depositati su una striscia rettangolare di grafene su un substrato rigido di  $SiO_2/Si$ . Campioni contenenti contatti di metalli differenti sono stati prodotti e testati tramite l'uso del Transfer Length Method (TLM) che consente l'estrazione dei valori di resistenza di contatto. In questo step sono stati ottenuti valori di  $R_c$  molto bassi per elettrodi in oro puro. Successivamente tramite semplici trattamenti di etching, la zona di grafene sottostante il metallo è stata "patternata" permettendo un incremento del bordo di contatto tra gli elettrodi ed il grafene stesso. Questo ha provocato un'ulteriore diminuzione della resistenza di contatto fino ad un valore intorno ai 90  $\Omega$  µm che all'oggi risulta essere il più basso mai registrato.

Questo lavoro apre quindi una strada alternativa per la creazione di nuovi dispositivi basati su grafene in grado di operare a frequenze sempre più alte.

# Contents

| Ab  | bstract                                                                                                                                                                                                                                                                                                                                                                      | i                                  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Es  | stratto                                                                                                                                                                                                                                                                                                                                                                      | ii                                 |

| Lis | ist Of Figures                                                                                                                                                                                                                                                                                                                                                               | v                                  |

| 1   | Graphene         1.1 Introduction         1.2 Electronic properties         1.3 "Exotic" behaviours of graphene         1.3.1 Quantum Hall Effect         1.3.2 Klein tunneling         1.4 Production methods         1.4.1 Micromechanical exfoliation         1.4.2 Liquid Phase Exfoliation         1.4.3 Epitaxial growth         1.4.4 Chemical Vapor Deposition (CVD) | 2<br>6<br>9<br>9<br>11<br>11<br>12 |

| 2   | <ul> <li>High Frequency Electronics</li> <li>2.1 Metal Oxide Semiconductor FETs</li> <li>2.2 FETs RF performance parameters</li> <li>2.3 Graphene FETs</li> <li>2.4 Graphene high frequency limiting factors</li> <li>2.4.1 Mobility</li> <li>2.4.2 Gate Stack</li> <li>2.4.3 Contact Resistance</li> </ul>                                                                  | 19<br>21<br>27<br>27<br>28         |

| 3   | <ul> <li>Contact Resistance Test Devices Fabrication</li> <li>3.1 Sample Preparation</li> <li>3.1.1 Substrate</li> <li>3.1.2 Graphene Transfer</li> <li>3.1.3 Quality assessment</li> <li>3.2 Fabrication Techniques</li> <li>3.2.1 Electron Beam Lithography (EBL)</li> <li>3.2.2 Reactive Ion Etching</li> </ul>                                                           | 33<br>34<br>35<br>37<br>37         |

|   |                   | Ab initio analysis of metal-graphene interaction             | 53<br>54             |

|---|-------------------|--------------------------------------------------------------|----------------------|

| 4 | <b>Res</b><br>4.1 | ultsTransfer Length Method4.1.1 TLM structure specifications |                      |

|   | 3.3               | 3.2.3 Electron Beam Evaporation                              | 45<br>46<br>46<br>46 |

# **List of Figures**

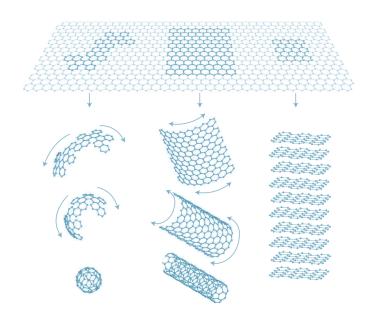

1.1 Mother of all graphitic forms graphene is the 2D building block for carbon based materials of all other dimensionalities. It can be wrapped up into a OD buckyballs, rolled into 1D nanotubes or stacked into 3D graphite. Picture adapted from [1]. . . . .

2

З

4

4

5

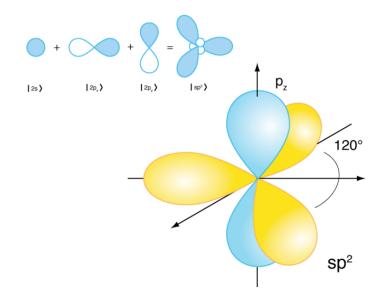

- 1.2  $sp^2$  utilizes the 2s orbital and two of the 2p orbitals in order to form three hybrid orbitals and an unchanged  $p_z$  orbital. The new set of formed hybrid orbitals creates trigonal structures, leading to a molecular geometry of  $120^\circ$ . When bonded to other carbon atoms, the remaining  $p_z$  orbital give rise to a delocalized  $\pi$  bond, responsible of the electrical conduction.

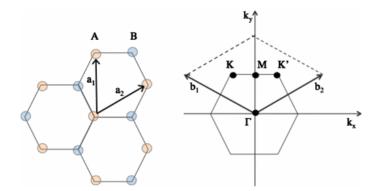

- 1.3 Left: the lattice structure of graphene is composed by two interpenetrating triangular lattices A and B with lattice unit vectors  $a_1$  and  $a_2$ . Right: hexagonal Brillouin zone representation in which  $b_1$  and  $b_2$  are the reciprocal lattice vectors; in the Kand K' points, also called Dirac points, the conduction and the valence bands touch each other [2].

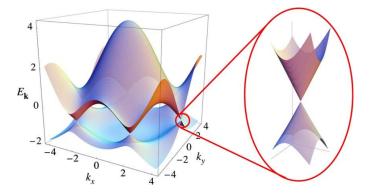

- 1.4 Electron band structure in the honeycomb lattice of graphene. In the right side the conical shape is shown, therefore near K and K' the dispersion relation is relativistic with an effective mass being zero. Picture taken from [3]

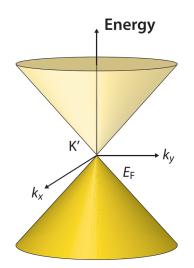

- 1.5 Graphene band structure zoomed in the proximity of the Dirac point. It is clearly visible its conical shape, which is responsible of the massless Dirac fermions behavior of the electrons. Picture adapted from [4].

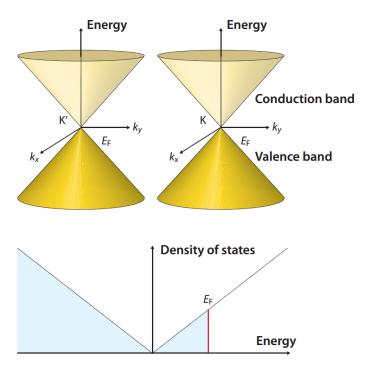

- 1.6 Graphene Density of the States (DOS) calculated starting from the linear dispersion relation in the proximity of the Dirac point. At the energy where the conduction and the valence bands meet, the DOS have a vanishing point. Picture adapted from [4].

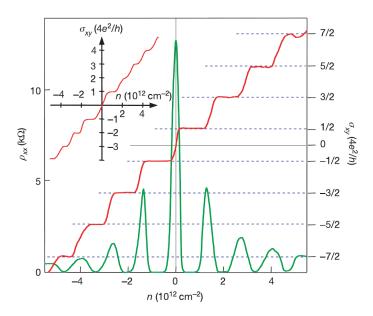

- 1.7 Hall conductivity  $\sigma_{xy}$  and longitudinal resistivity  $\rho_{xx}$  of graphene as a function of their concentration at B = 14 T and T = 4 K. The value of  $\sigma_{xy} = (4e^2/h)$  is calculated from the measured dependences of  $\rho_{xy}(V_G)$  and  $\rho_{xx}(V_G)$ . The inset show  $\sigma_{xy}$  in "twolayer graphene" where the quantization sequence is normal and occurs at integer values. Picture taken from [5]. . . . . . 8

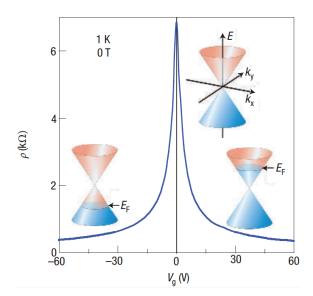

| 1.8   | Ambipolar electric field effect in single-layer graphene. The insets show its conical low-energy spectrum $E(k)$ , indicating changes in the position of the Fermi energy $E_F$ with changing gate voltage $V_G$ . Picture taken from [1]                                                                                                                                                                                                                                                                                                                                                                    | 10 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

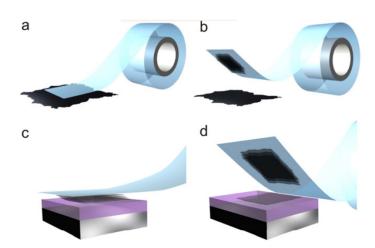

| 1.9   | Micromechanical exfoliation of 2D crystals. (a) Adhesive tape<br>is pressed against a 2D crystal so that the top few layers are<br>attached to the tape (b). (c) The tape with crystals of layered<br>material is pressed against a surface of choice. (d) Upon peel-<br>ing off, the bottom layer is left on the substrate. Picture taken                                                                                                                                                                                                                                                                   |    |

| 1.1(  | from [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12 |

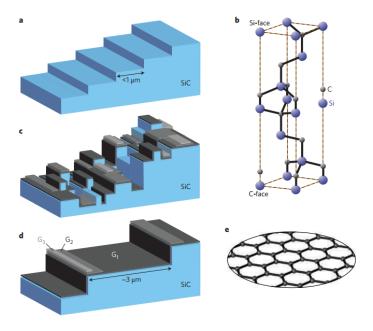

| 1 1 4 | and trilayer (G3) graphene near the upper edge of the sub-<br>strate steps. Picture taken from [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13 |

|       | of graphene. Picture reproduced from [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|       | reproduced from [8].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15 |

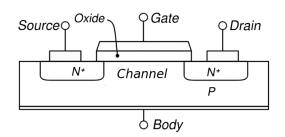

| 2.2   | (a): Sketch of an n-type MOSFET device, based on a p-type substrate. The gate stack is formed by an insulator sandwiched between the substrate and the gate metal electrode. Two highly n-doped regions are implanted at the edges of the channel corresponding to the source and drain electrodes. (b): In the off-state of the MOSFET a negative $V_G$ induces in the channel an high concentration of holes; the n-p-n double junction prevents the onset of a current. (c): When $V_G > V_{th}$ in the channel, previously depleted by holes, negative carriers are attracted thus conduction is allowed | 17 |

|       | that depends on $V_{DS}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18 |

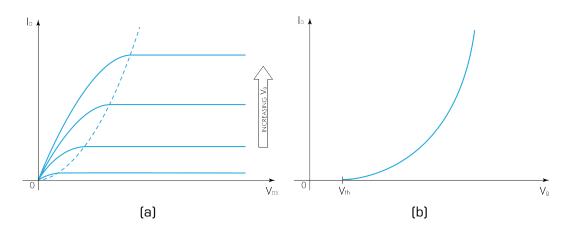

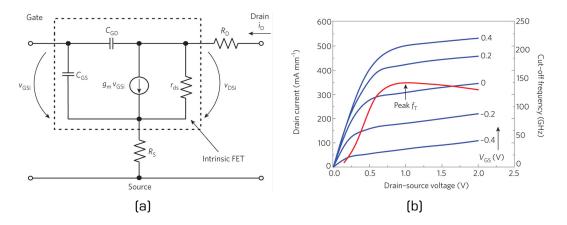

- 2.3 (a): Small-signal equivalent FET circuit. Here  $C_{GS}$  and  $C_{GD}$  are respectively the gate-source and the gate-drain capacitance. The intrinsic transconductance,  $g_m$ , is related to the internal small-signal gate-source and drain-source voltages, whereas the output transconductance,  $g_0$ , is related to the applied gate-source and drain-source voltages. (b): The dependence of the cut-off frequency ( $f_T$ ) on the controlling parameter shows a peak in the region where both the transconductance  $g_m$  and the output resistance ( $r_0$ ) are high. Pictures taken from [9] . . 20

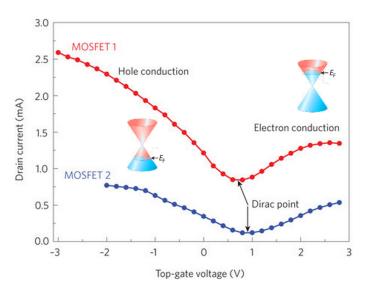

- 2.5 Typical transfer characteristic for two GFETs with large area graphene channels. It is clearly visible the ambipolar conduction: when  $V_G$  is less then the Dirac point,  $E_F$  goes in the valence band and the conduction is performed by holes. Once  $V_G$  goes beyond the Dirac point,  $E_F$  falls in the conduction band and electrons transport is promoted. Picture taken from [9] . 22

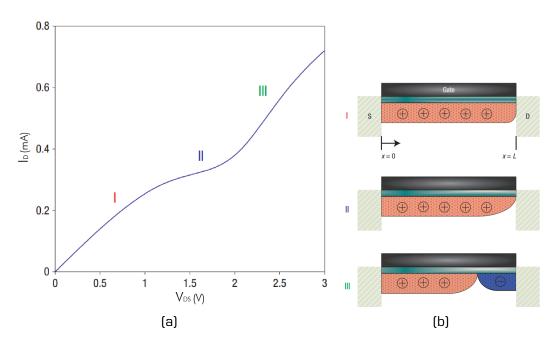

- 2.6 (a): GFET characteristic with a sort of saturation like behavior placed between two regions in which current increase linearly with respect to drain voltage. (b): Schematic representation of the carrier concentration under the top-gated region. In point I the channel is entirely p-type and the GFET operate in the linear region. In zone II the drain side of the channel changes carrier type, promoting the recombination between electrons and holes and therefore saturating the current. In zone III the Dirac point, moving toward the source side, promotes the conduction of electron and the current starts growing again. Pictures taken from [10]

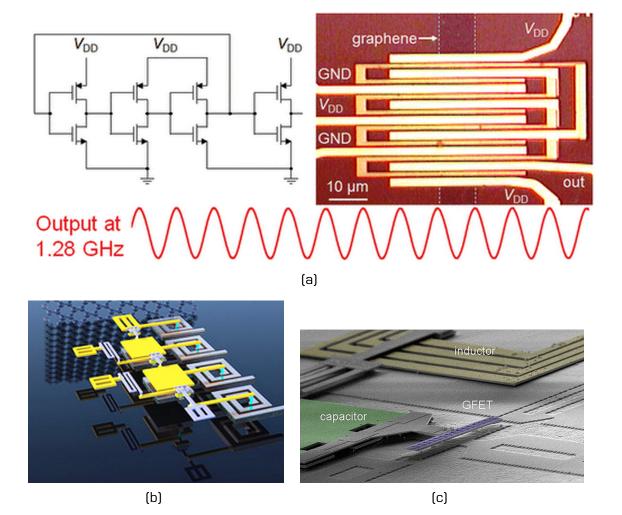

| 2.8 | (a): Ring oscillator produced by Guerriero et al. [11] at the  |

|-----|----------------------------------------------------------------|

|     | L-NESS laboratories. It is composed by 8 integrated graphene   |

|     | transistors and the maximum frequency of operation goes be-    |

|     | yond the GHz barrier. (b) and (c): Images taken from [12] rep- |

|     | resenting the new graphene based integrated circuit (by IBM)   |

|     | working with on a wireless network band of 4.3 GHz; the de-    |

|     | vice was able to receive and restoring a text message without  |

|     | distortions                                                    |

26

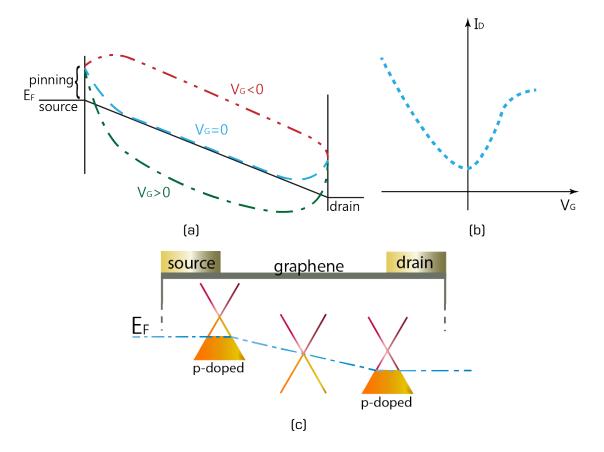

- 2.11(a): Schematic of the band diagram through the GFET section. The different tracks represent the "position" of the Dirac point for different applied voltages. Picture adapted from [14] (c): Transfer curve which shows the asymmetric behavior of the carrier flow due to the p-n junctions. (b): Representation of the graphene "doping" state in the FET. Once  $V_G > 0$  the Fermi level shift upwards leading to the formation of a p-n-p junction. 31

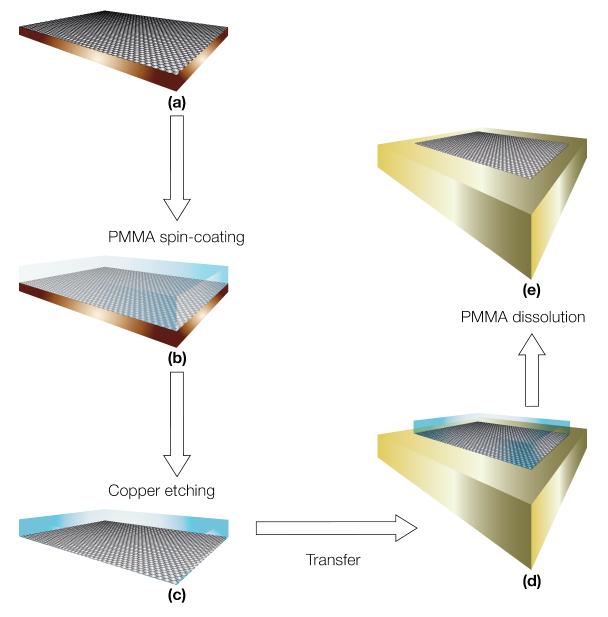

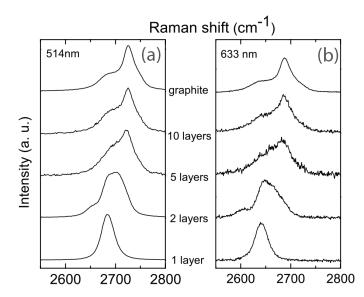

| 3.3  | Evolution of the Raman spectra under a 514 nm (a) and 633 nm (b) laser source with the number of layers. Picture taken from              |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

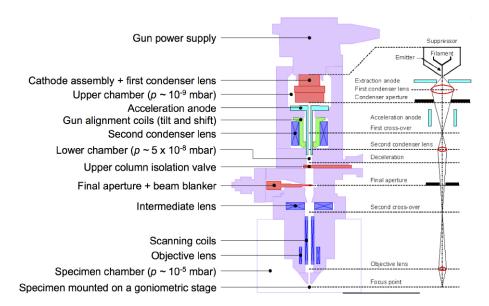

| 3.4  | Ferrari et al. [15]EBL system scheme. For study purpose SEM machine can be                                                               | 37 |

|      | adapted for lithography simply adding a beam blanker system<br>and modifying the gun alignment coils. This result in a cheaper           |    |

|      | but less precise instrument with respect to that dedicated to EBL.                                                                       | 38 |

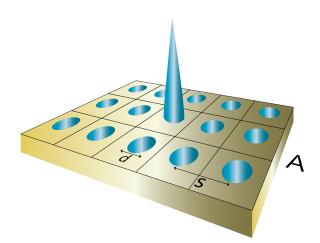

| 3.5  | Scheme of some EBL controlling parameters; the spot size (d)                                                                             | 00 |

|      | and the step size (s) are very important in the definition of the                                                                        | 40 |

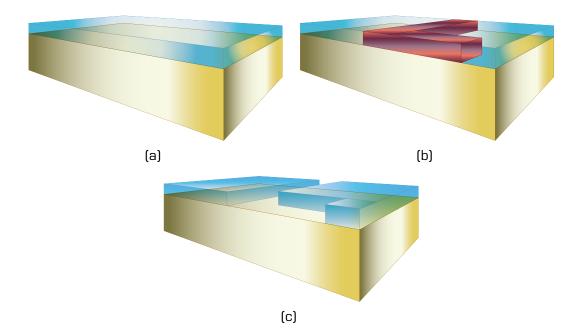

| 36   | exposure time for an area (A)                                                                                                            | 40 |

| 0.0  | posited on the top surface (a); the desired mask is patterned                                                                            |    |

|      | drawing with an electron beam (b) and finally the exposed poly-                                                                          | 11 |

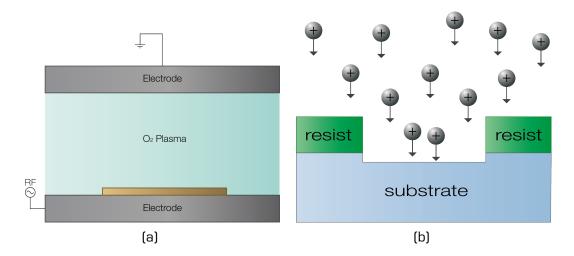

| 3.7  | mer is dissolved by a develop solution (c)                                                                                               | 41 |

|      | The plasma forms between the two electrodes under a radio                                                                                |    |

|      | frequency electric field. (b): The "heavy" ions are accelerated towards the surface where the part to be etched is uncovered             |    |

|      | by the resist mask.                                                                                                                      | 42 |

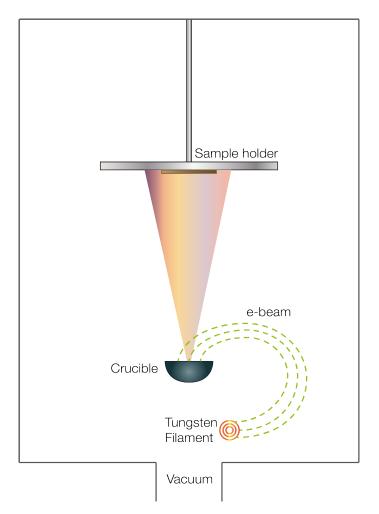

| 3.8  | Scheme of an electron beam evaporation system. The sample                                                                                |    |

|      | is hold face down exactly over the source crucible. Once the electron beam hit the metal it evaporate depositing on the cold             |    |

|      | surface of the chip.                                                                                                                     | 43 |

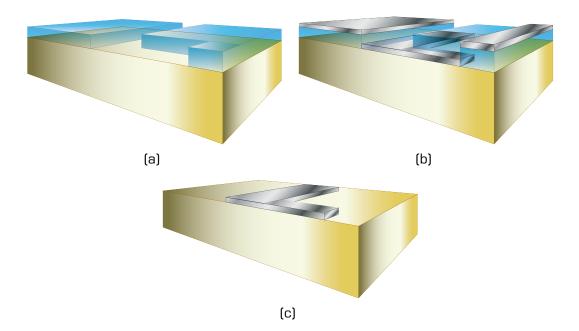

| 3.9  | Scheme of the evaporation process. Once the EBL mask is                                                                                  |    |

|      | ready (a), the evaporation process takes place, depositing a metal layer over the entire surface (b); during the lift-off proce-         |    |

|      | dure the resist is dissolved in a solvent and only the patterned                                                                         |    |

| ר ב  | metallization remains on the substrate(c)                                                                                                | 45 |

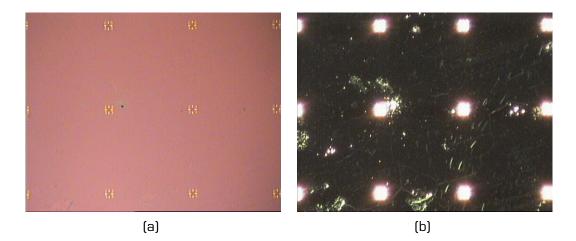

| 0.10 | and (b) dark field. Using the dark field it is easy to recognize                                                                         |    |

| 0 4  | the bigger defects on the surface.                                                                                                       | 47 |

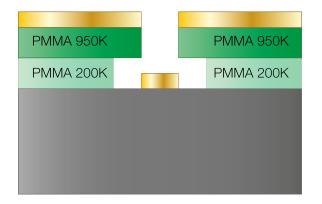

| 3.1  | 1The use of different molecular weight resists allows the forma-<br>tion of an undercut which makes easier the subsequent lift-off       |    |

|      | procedure                                                                                                                                | 47 |

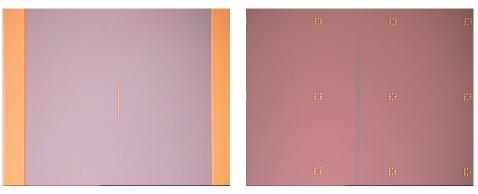

| 3.12 | 2Representation of the entire fabrication process. (a): an area                                                                          |    |

|      | of $1000 \times 1000 \mu m^2$ is completely exposed except of the stripe<br>at the center. After the subsequent etching procedure only a |    |

|      | $5\mu m$ width of graphene remains (b). The electrodes and the                                                                           |    |

|      | external connections are then patterned (c) and evaporated (d).                                                                          |    |

|      | The final result is showed in (e) through the use of a SEM. The entire chip is composed by nine different structures fabricated          |    |

|      | at the same time.                                                                                                                        | 49 |

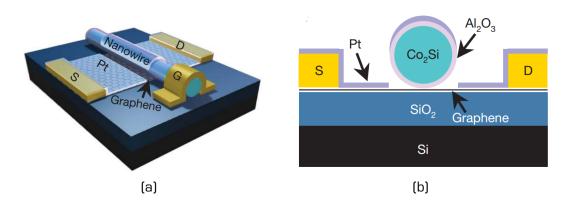

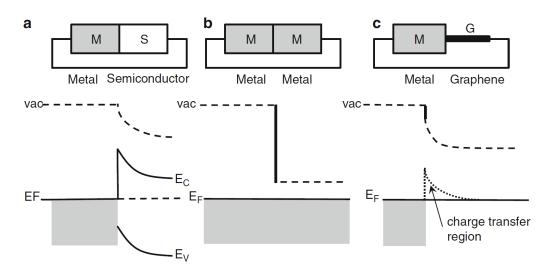

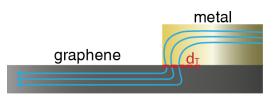

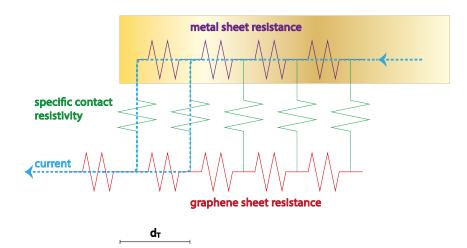

| 4.1         | Model of a metal-graphene contact. During its path the charges experience different resistive "forces" coming from the metal sheet resistance, the specific contact resistivity at the contact interface, and the graphene sheet resistance. Here it is also shown the "current crowding" effect, which involves the current flowing preferentially through the contact edges; precisely, the most of the charge transfer takes place in a distance $d_T$ from |          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

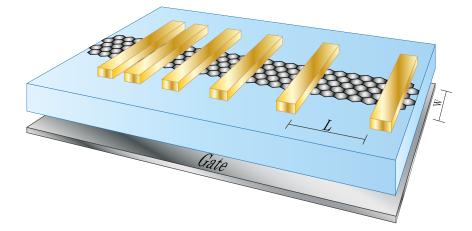

| 4.2         | the contact boundary corresponding to the transfer length Transfer Length Method based on the measurement of the resistance in the flow of charges between two neighboring electrodes. Here $W$ and $L$ identify respectively the width and the                                                                                                                                                                                                                |          |

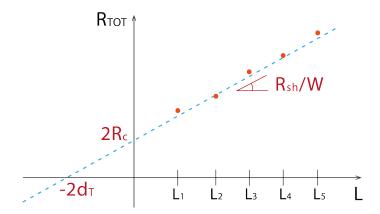

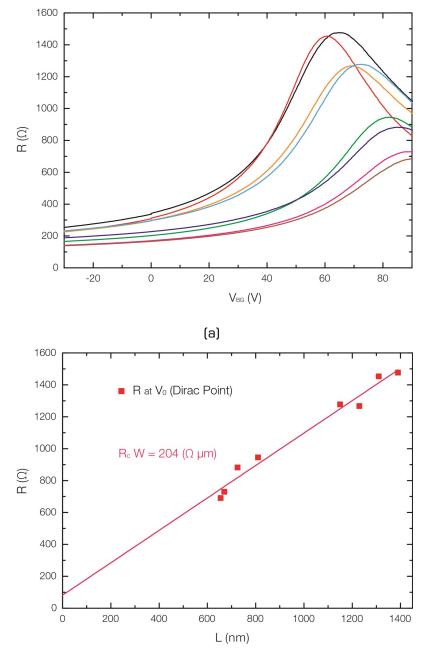

| 4.3         | length of the channel. $R_{TOT}$ versus $L$ plot. The red points represent the experimental values taken by the resistance measurements. A linear fit is made in order to find the complete set of parameters which characterize the contact resistance and the graphene sheet                                                                                                                                                                                 | 52       |

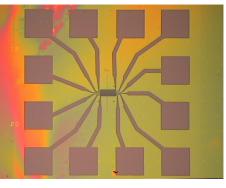

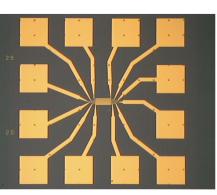

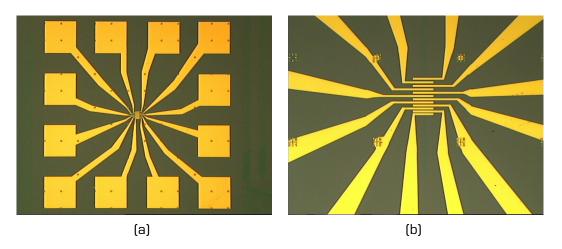

| 4.4         | <ul> <li>(a): Image taken at the optical microscope of an entire TLM structure. The test probes are placed on the squared metal pads which allows the connection with the inner active part.</li> <li>(b): 100x zoom of (a). In the middle of the electrodes the string of graphone is barghy visible.</li> </ul>                                                                                                                                              | 52<br>54 |

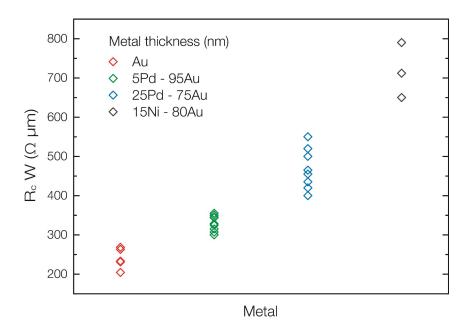

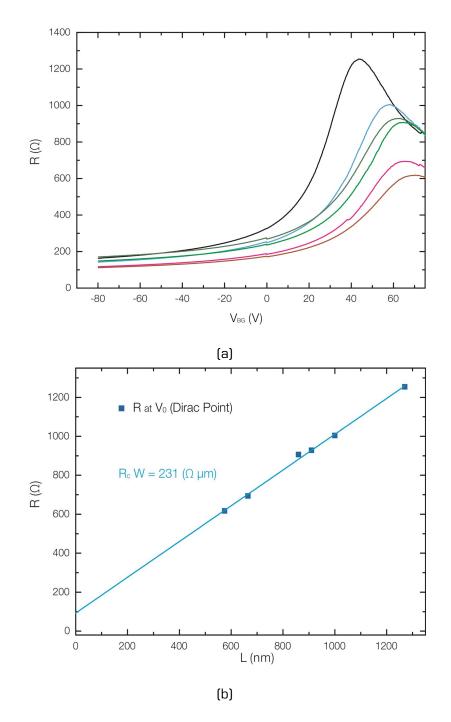

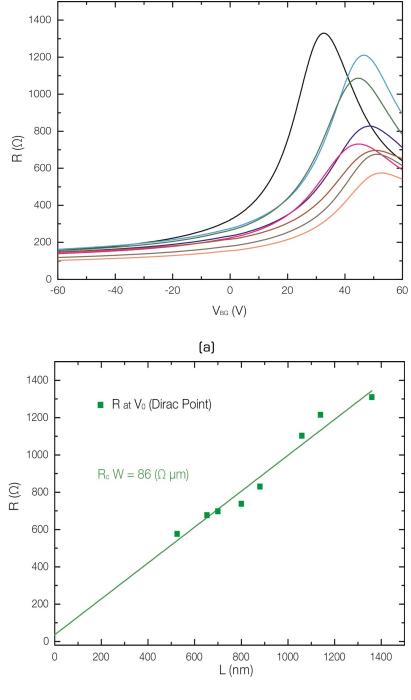

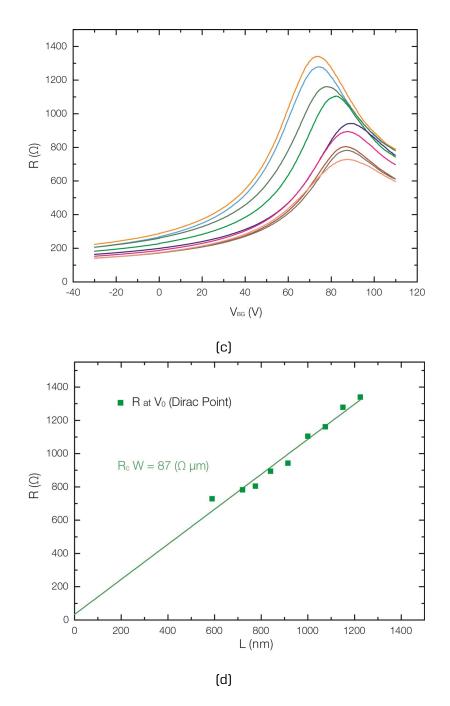

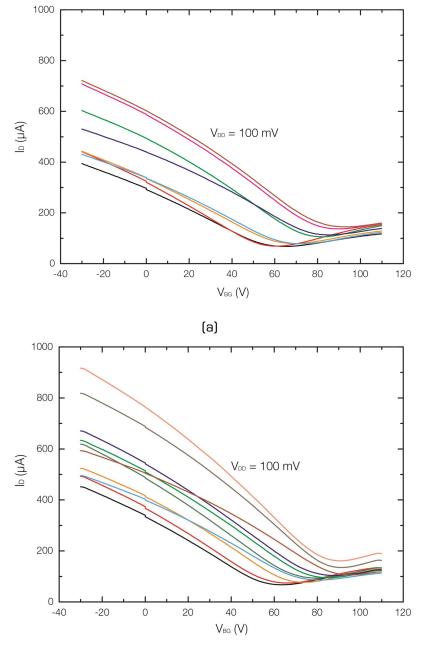

| 4.5         | stripe of graphene is barely visible. $\dots \dots \dots$                                                                                                                                                                                                                                                                                                      | 54       |

| 4.6         | in the order of $250 \Omega \mu m$                                                                                                                                                                                                                                                                                                                                                                                                                             | 55<br>56 |

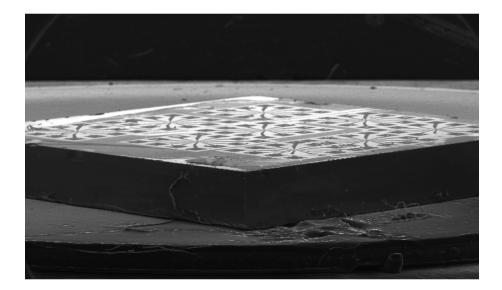

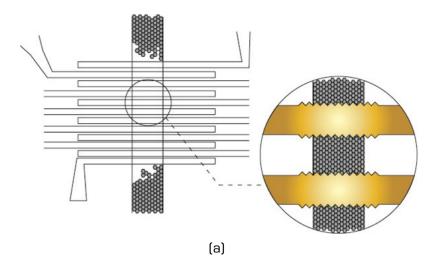

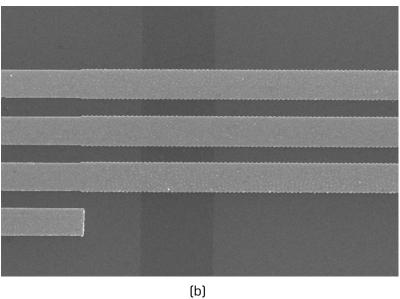

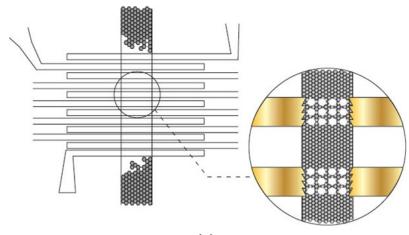

| 4.7         | (a): design sketch of a "zig-zag" patterned TLM structure. (b):<br>SEM image of the same structure after the electrodes deposi-<br>tion. Graphene is clearly visible in the center of the structure                                                                                                                                                                                                                                                            |          |

| 4.8         | (dark stripe)                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57       |

| 4.9<br>4.10 | beneath the metal is clearly visible                                                                                                                                                                                                                                                                                                                                                                                                                           | 58<br>59 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62       |

# **1** Graphene

This chapter provide an overview on graphene as the building block for a new technological areas. Section 1.1 introduce graphene and its properties; section 1.2 gives a brief description of the band structure and carrier transport in graphene; section 1.3 go deeply exploring the new "exotic" properties of this 2D material. The principal production methods, with drawbacks and advantages, are finally described in section 1.4.

## **1.1** Introduction

In the early 60's Hanns-Peter Boehm were studying single-layer carbon atoms which, stacked one above another result in graphite, giving it the name of "graphene" [16]. Although the existence of this kind of material were known from years, only in 2004 A.K Geim and K.S. Novoselov, researchers of the center for Mesoscopic and Nanotechnology at the University of Manchester, were able to isolate and study a single layer of graphene [17] [5]. From that time, graphene has attracted the attention of a large part of the world's science community. Less then 4 Angstroms (Å) thick, it is composed by a set of carbon atoms with a  $sp^2$  hybridization, packed in an hexagonal honeycomb lattice structure. The very high ratio between its flakes size and thickness, makes graphene the firs stable 2-dimensional crystal ever observed in nature. It can be considered as the building block for all the carbon-based systems (Figure 1.1): graphite is an ordered stack of graphene layers with an interplanar distance of about 3,34 Å, carbon nanotubes are rolled-up sheets of carbon atoms, and fullerenes, also known as "buckyballs", are spherical shape nanostructures obtained wrapping-up graphene.

Since it re-discovery graphene caught the attention of many scientists because of its remarkable properties which promise future improvements in numerous technological areas. The possibility to make faster and smaller electronic devices, thanks to the very high carriers mobility [1] [18] and its stability even at room temperature [19], have been leaded to the rise of many new research groups which are currently building the scaffold for the develop of graphene-based devices. Other possible applications come from properties such as an extraordinary strength and flexibility [20], a very high thermal conductivity [21] and low interfacial thermal resistance [22], an optical transparency of about 98% of visible light [23], which make graphene suitable for purposes like optoelectronics [24], molecular sensors, energy storage systems [25], and many else.

Many eyes are focused on this new material and many critics have been

**Figure 1.1:** Mother of all graphitic forms graphene is the 2D building block for carbon based materials of all other dimensionalities. It can be wrapped up into a OD buckyballs, rolled into 1D nanotubes or stacked into 3D graphite.

Picture adapted from [1].

made on it, however in 2013 Europe financed a research project for one billion euros which involves a lot of groups and companies for ten years, with the aim to explore and develop graphene technology, making it competitive and ready for a large scale production<sup>1</sup>.

### **1.2 Electronic properties**

Carbon is the fourth most abundant chemical element in the universe by mass, and can present itself under several forms showing particular characteristics as a result of the different interaction of the electron clouds. In the base form it has six protons and six electrons; two of them are strongly bonded to the nucleus occupying the 1s orbital thus they are irrelevant for chemical reactions, whereas the remaining four, placed in the 2s and 2p orbitals, are available for covalent bonds. The comparable energies of this latter orbitals lead to the possibility of mixing them forming new *hybrid* orbitals which result from the linear combination of the electron wave functions. Depending of how many p orbitals are involved in this process it is possible to speak about  $sp^1$ ,  $sp^2$ , or  $sp^3$  hybridization. The 2D nature of graphene is related to the creation of three  $sp^2$  hybrid orbitals which laid in a plane orthogonal to that of the remaining p orbital enabling the formation of three

<sup>&</sup>lt;sup>1</sup>http://graphene-flagship.eu

**Figure 1.2:**  $sp^2$  utilizes the 2s orbital and two of the 2p orbitals in order to form three hybrid orbitals and an unchanged  $p_z$  orbital. The new set of formed hybrid orbitals creates trigonal structures, leading to a molecular geometry of  $120^\circ$ . When bonded to other carbon atoms, the remaining  $p_z$  orbital give rise to a delocalized  $\pi$  bond, responsible of the electrical conduction.

$\sigma$  bonds (Figure 1.2). The last p orbital, when the carbon atoms are put close in contact, forms a delocalized  $\pi$  bond which is the responsible of the electron mobility through the graphene sheet.

The graphene honeycomb lattice for definition is not a Bravais lattice since it is not possible to find a translation vector which can reach all the nodes with an integer combination of two base vectors, however it can be viewed as the interpenetration of two triangular sublattices (A and B in figure 1.3). Therefore the construction of a Bravais lattice can be made taking into account only one triangular lattice with a primitive cell base formed by two atoms separated by a distance  $a_{C-C} = 0.142$  nm. The right part of Figure 1.3 show an illustration of the firs Brillouin zone (BZ) based on the construction of the reciprocal lattice; it represents a set of nonequivalent points in the reciprocal space, i.e. points which may not be connected to one another by a reciprocal lattice vector. In the BZ it is possible to distinguish some high symmetry points: the K and K' points are placed at the six corners of the BZ, whereas the  $\Gamma$  and the M points are situated respectively at the center of the BZ and in the middle of the edges [26] [27].

It is proved that charged particles in graphene are well described by the Dirac relativistic equation in which the particles approach a speed lower than that of light called Fermi velocity. The band structure o monolayer

**Figure 1.3:** Left: the lattice structure of graphene is composed by two interpenetrating triangular lattices A and B with lattice unit vectors  $a_1$  and  $a_2$ .

Right: hexagonal Brillouin zone representation in which  $\mathbf{b_1}$  and  $\mathbf{b_2}$  are the reciprocal lattice vectors; in the K and K' points, also called Dirac points, the conduction and the valence bands touch each other [2].

**Figure 1.4:** Electron band structure in the honeycomb lattice of graphene. In the right side the conical shape is shown, therefore near K and K' the dispersion relation is relativistic with an effective mass being zero. Picture taken from [3]

graphene is accurately extracted using a tight-binding approach considering only nearest-neighbor hooping and a single  $\pi$  electron per carbon atom [3] [28] [29]. As shown by the previously cited articles the resultant dispersion relation can be written as

$$E^{\pm}(k_x, k_y) = \pm \gamma_0 \sqrt{1 + 4\cos\frac{\sqrt{3k_x a}}{2}\cos\frac{k_y a}{2} + 4\cos^2\frac{k_y a}{2}}$$

(1.1)

where  $a = \sqrt{3}a_{C-C}$  is the lattice constant whereas  $\gamma_0$  is the nearest-neighbor overlap integral which, accordingly with Reich et al. [29], takes a value between 2.5 and 3 eV. Figure 1.4 represent the band structure of graphene calculated using the equation 1.1. The conduction ad the valence band meet at the high symmetry K and K' points also known as the *Dirac* or charge

**Figure 1.5:** Graphene band structure zoomed in the proximity of the Dirac point. It is clearly visible its conical shape, which is responsible of the massless Dirac fermions behavior of the electrons. Picture adapted from [4].

neutrality points. This two points in reciprocal space can be directly related to real space graphene sublattices: K originate from electrons on sublattice A whereas K' from electrons on sublattice B. Graphene, defined as both a semi-metal and a zero-gap semiconductor, has the Fermi level ( $E_F$ ), in its pristine (undoped) state, situated precisely at the energy where the conduction and valence bands meet, living the valence band completely filled and the conduction band empty. The expansion of the equation 1.1 close to the Dirac point (K or K')<sup>2</sup> result in the well known linear dispersion relation between energy and momentum:

$$E^{\pm}(\kappa) = \pm \hbar v_F |\kappa| \tag{1.2}$$

where  $\kappa = k - K(K')$  is the wave vector measured from K(K') and  $v_F$  is the Fermi velocity for the electron in graphene defined as:

$$v_F = \sqrt{3}\gamma_0 a/2\hbar \approx 1 \times 10^6 \,\mathrm{m\,s^{-1}}$$

Equation 1.2 is a good approximation as long as the momentum does not deviate so far from the K(K') point. As shown in figure 1.5 the effect is the creation of two conic shape bands touching at the Dirac point. Furthermore graphene possesses an additional quantum number called *pseudospin*, which originates from the two equivalent A and B sublattices. Carriers with opposite momentum have also opposite pseudo-spin and their wave functions are orthogonal without overlap. As a consequence the  $180^{\circ}$  backscattering is forbidden in graphene.

<sup>&</sup>lt;sup>2</sup>Due to the equivalence between the three K and K' points it is possible to restrict the consideration on the dispersion relation to just two of them.

Considering the definition of effective mass

$$m^* = \frac{\hbar^2}{\frac{\partial^2 E(k)}{\partial k^2}}$$

it easy to see that this expression for the carriers in graphene takes no sense, in fact a linear dispersion relation is characteristic of massless particle like photons. It is therefore convenient the use of the relativistic expression

$$E = \sqrt{(m_0 c^2)^2 + p^2 c^2}$$

as a way for relating mass with energy. Substituting it in the equation 1.2, with crystal momentum defined as  $p = \hbar k$ , a unique solution is found setting the rest mass  $m_0$  equal to zero and considering that the Fermi velocity  $v_F$  plays the role of the speed of light in graphene.

Summarizing, close to the Dirac point, the graphene dispersion relation is well described by the relativistic Dirac equation. In this description electron and holes are considered as massless Dirac Fermions traveling with a group velocity defined by the Fermi velocity  $v_F$ . This makes graphene a bridge between condensed matter physics and quantum electrodynamics (QED) [30], providing an easy way to investigate many QED phenomena.

To conclude the review about the graphene electronic properties a consideration on the density of the states (DOS) (Figure 1.6) is noteworthy as it influence the performance of the graphene based devices. Limiting the discussion around the Dirac point the density of the states can be written as:

$$D(E) = \frac{4|E|}{\pi\hbar^2 v_F^2} = \frac{4\sqrt{\pi n}}{\pi\hbar v_F}$$

(1.3)

Thus it increase linearly with energy and is proportional to the square root of the carrier density (*n*) vanishing at the Dirac point. This DOS lead to a carrier concentration in graphene of about  $10^{11} \text{ cm}^{-2}/10^{13} \text{ cm}^{-2}$  with respect to that of a metal that is around  $10^{22} \text{ cm}^{-3}$ . This difference will be important in the analysis of the metal-graphene contacts since it influences the contact resistance in graphene devices. Despite zero carrier density near the Dirac point, a *quantum conductance* at integer multiples of  $2e^2/h$  is observed [31] [5], which is strictly related to the later explained *quantum hall effect* shown by graphene under the application of a magnetic field.

### **1.3** "Exotic" behaviours of graphene

It is proved that the carrier mobility in graphene could reach the highest value already known. From the technological point of view this is mainly the

**Figure 1.6:** Graphene Density of the States (DOS) calculated starting from the linear dispersion relation in the proximity of the Dirac point. At the energy where the conduction and the valence bands meet, the DOS have a vanishing point. Picture adapted from [4].

**Figure 1.7:** Hall conductivity  $\sigma_{xy}$  and longitudinal resistivity  $\rho_{xx}$  of graphene as a function of their concentration at B = 14 T and T = 4 K. The value of  $\sigma_{xy} = (4e^2/h)$  is calculated from the measured dependences of  $\rho_{xy}(V_G)$  and  $\rho_{xx}(V_G)$ . The inset show  $\sigma_{xy}$  in "two-layer graphene" where the quantization sequence is normal and occurs at integer values. Picture taken from [5].

reason for the great interest in the design and fabrication of graphene-based devices. Although a value of  $1\,000\,000\,\mathrm{cm^2V^{-1}s^{-1}}$  is reached in graphene at liquid Helium temperature [32], at room temperature the acoustic phonon interaction limits the mobility value at  $200\,000\,\text{cm}^2\text{V}^{-1}\text{s}^{-1}$  [33]. In conventional semiconductor materials such as silicon and gallium arsenide, optical phonon scattering dominates at room temperature, causing a sharp decrease of the electron mobility with increasing temperature. The very high energy of optical phonons in graphene prevents their interaction with the electrons, causing a negligible loss in mobility [34] [35]. Although in some semiconductors like InSb a mobility of  $78000 \,\mathrm{cm^2 V^{-1} s^{-1}}$  is observed [36]. these values are quoted for undoped bulk semiconductors. Conversely in graphene mobility has a weak dependence on *n*, remaining high even at high carrier concentration. Moreover, the symmetrical behavior of the conduction and valence band around the Dirac point, indicates that electrons and holes should have equal *mobility* unlike the typical semiconductors where two different values are observed, with holes mobility begin particularly low. Since the transport properties in graphene are governed by impurity and defect scattering, ballistic transport should be easy reachable at the submicrometer scale. Room temperature ballistic transport on micrometer scale, predicted by Bolotin et al. [37] and Du et al. [38], has been confirmed in 2011 by Mayorov et al. [39].

#### 1.3.1 Quantum Hall Effect

In the presence of a strong perpendicular magnetic field B, charges confined in two dimensions are constrained to move in close cyclotron orbits with a characteristic cyclotron frequency  $\omega_C$ . Treating this orbitals quantum mechanically they result quantized leading to the formation of discrete Landau levels (LLs) in the energy spectrum. In other words electrons occupy discrete Landau energy level as a result of their quantized orbits. This is known as *Quantum Hall Effect* (QHE) and in graphene, unlike the conventional 2D systems, it reveals also at room temperature [40]. Roughly speaking the quantum hall effect is a quantization of resistance that is defines by the electron fundamental charge q and the Plank constant h. This quantum behavior shows up as a plateau in the conductance measured transverse to the current flow ( $\sigma_{xy}$  in Figure 1.7). As one LL fills up, the conductance is flat, showing no increase with carrier density until the next LL is nearly filled. Due to the massless Dirac like nature of carriers in graphene, the eigenenergies of the LLs are given by [41] [42]:

$$E_n = \sqrt{2eB\hbar v_F^2}|l| \qquad l = 0, \pm 1, \pm 2, \dots$$

instead of that of the conventional 2D systems:

$$E_n = \hbar\omega_C \left( l + \frac{1}{2} \right)$$

This implies the existence of an anomalous LL at zero energy (indicated by the peak at n = 0 of  $\rho_{xx}$  in Figure 1.7) [5] [43]. Furthermore in graphene the rule for quantization of  $\sigma_{xy}$  takes the form

$$\sigma_{xy} = g\left(l + \frac{1}{2}\right)\frac{e^2}{h}$$

where g is the total degeneracy spin and valley degeneracy. This expression, compared to that of conventional 2D systems

$$\sigma_{xy} = gl\frac{e^2}{h}$$

shows an additional 1/2 that is an hallmark of the chiral nature of the Dirac fermions in graphene.

#### 1.3.2 Klein tunneling

In classical mechanics, a potential barrier whose height is greater than the energy of a particle will confine that particle. In quantum mechanics, the notion of quantum tunneling describes the process whereby the wawefuncion

**Figure 1.8:** Ambipolar electric field effect in single-layer graphene. The insets show its conical low-energy spectrum E(k), indicating changes in the position of the Fermi energy  $E_F$  with changing gate voltage  $V_G$ . Picture taken from [1].

of a non-relativistic particle can leak out into the classically forbidden region. However, the transmission through such a potential barrier decreases exponentially with both barrier height and width. In the case of Dirac relativistic particles, the situation is quite different as demonstrated years ago by the noble prize winner Oskar Klein [44]. When a Dirac electron is incident on a potential barrier it will traverse it as a hole, emerging on the other side as an electron once again. The transmission probability of such a particle increase with increasing barrier height, approaching unity for an infinite wall. This kind of effect, known as Klein tunneling, has been successfully demonstrated for the first time in graphene by Katsnelson et al. [45]. On one hand, the difficulty in confining electrons, represent a real barrier in the develop of short channel graphene-based transistors, but, on the other hand, new ways for take advantage from the Klein tunneling effect are currently being exploring.

Nowadays what makes graphene so interesting for next-future applications is the so called *ambipolar electric field effect* [19]. Despite the classical semiconductors the electrical conduction in graphene can be dominated by either positive (holes) or negative (electrons) charges depending on the sign of the applied electric field modulated by an external bias. This result in a "V-shape" of the drain current - gate voltage (Id/Vg) characteristic for a graphene field effect transistor (GFET). Figure 1.8 represent a resistivity gate voltage curve of a GFET; at negative gate voltage the conduction is supported by holes whereas at positive gate voltage electrons conduction takes place. As presented in Section 2.3 this kind of behavior makes graphene a perfect candidate for CMOS applications, since the construction of p-type and n-type transistors could be done on the same piece of material instead of the complex operations required for classical semiconductors.

## **1.4 Production methods**

As already said 2D crystals like graphene were expected not to exist in a stable form. This is principally due to the thermal fluctuations (phonons) taking place at the growth temperature, which force the material into a 3D stable structure. To overcome this obstacle many tricks have been found such as growth graphene on top of a 3D crystal removing the bulk at sufficiently low temperatures to avoid undesirable thermal flacutations. Once Geim and Novoselov found the easiest way to obtain graphene [5], as known as "scotch tape method", many production processes have been exploited. The compromise between reaching a large-scale production and keeping the acceptable quality for applications which graphene is intended for, are the two major criterion for the choice of the fabrication technique.

#### **1.4.1** Micromechanical exfoliation

Scotch tape method consist in the mechanical exfoliation of *Highly Oriented Pyrolytic Graphite* (HOPG) using adhesive tape to extract thin layers of graphene and then transferring them to a silicon substrate. For this reason the technique is referred as "micromechanical exfoliation", which so far provides the best quality graphene in terms of structural integrity and carriers mobility. Even though Blake et al. [23] found an easily way to see graphene with a standard optical microscope, the difficulty in location and the small size of the obtained flakes, limit the use of graphene obtained in such a way for fundamental studies.

The need of large scale manufacturing methods leaded to three principal production techniques named *chemical exfoliation*, *epitaxial growth* and *chemical vapor deposition growth*.

### 1.4.2 Liquid Phase Exfoliation

Liquid phase exfoliation is obtained starting from a dispersion of graphite in a solvent using ultrasounds to separate the layers. As final step the solution has to be centrifuged in order to separate the mono layer graphene to the thicker flakes [46]. In 2014 a method of producing industrial quantities of high-quality graphene, starting from liquid phase, has been developed by Trinity College (Dublin) researchers [47]. The quality of the obtained graphene

**Figure 1.9:** Micromechanical exfoliation of 2D crystals. (a) Adhesive tape is pressed against a 2D crystal so that the top few layers are attached to the tape (b). (c) The tape with crystals of layered material is pressed against a surface of choice. (d) Upon peeling off, the bottom layer is left on the substrate. Picture taken from [6].

flakes in addition to the low complexity of production, makes such graphene a good candidate for bulk application such as composite materials [48] as well as coating [49]. However, its use in electronic applications is still not possible due to the very small size of the flakes and the low control of the process.

#### 1.4.3 Epitaxial growth

Structurally perfect, macroscopically large graphene sheet with uniform thickness, should be the starting point for an active device fabrication. In that way the preparation of single-layer graphene by the thermal decomposition of silicon carbide (SiC) has been proposed as a viable route for the synthesis of uniform, large-size graphene layers [50]. Heating a SiC(0001) crystal above 1600 °C in an inert gas atmosphere [51] lead to Si sublimation leaving on the surface single layers and multi-layers carbon domains. As Si evaporates, even though there is a very large lattice mismatch between SiC (3.073Å) and graphene (2.46Å), the carbon atoms rearrange itself in a hexagonal structure. This kind of process, known as *"epitaxial growth"*, is limited at present by the lack of continuity and uniformity of the grown film, that makes its quality not as good as that of exfoliated graphene, except if graphene would be grown on a perfect single crystal. A considerable advantage of this method is that insulating SiC substrates can be directly used for device fabrication thus transfer to another substrate is not required.

**Figure 1.10:** (a) SiC starting surface with a staircase of flat terraces and atomic steps. (b) Unit cell of 6H-SiC. (c) Schematic morphology of vacuum-graphitized SiC. (d) Morphology obtained in high-pressure argon here the surface termination is predominantly monolayer graphene (G1), with narrow stripes of bilayer (G2) and trilayer (G3) graphene near the upper edge of the substrate steps. Picture taken from [7].

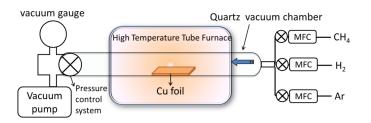

**Figure 1.11:** Schematic of a common setup for chemical vapor deposition of graphene. Picture reproduced from [8].

### 1.4.4 Chemical Vapor Deposition (CVD)

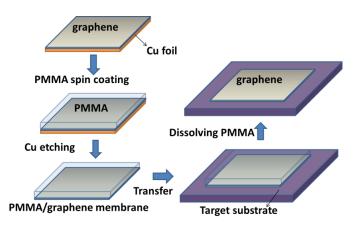

Chemical vapor deposition is a well known process involving the decomposition of a precursor on a substrate, forming a thin crystalline film. It has been known for some time that graphene growth from carbon containing gases like methane, can be catalyzed by various transition metal substrates. Since the amount of carbon that can be dissolved in most metals is up to a few atomic percents, for eliminate the competition between forming a carbide and the graphene growth, the use of non-carbide forming metals, e.g. Cu, Ni, Pt, is preferred [52]. Although nickel substrates are cheap, it was found that thermal catalytic decomposition of methane on a copper foil, of a well defined thickness, result in a self limited process, showing the 95% of the substrate surface covered by single layer graphene [53]. Bae et al. [54] achieved a CVD grown poly-crystalline graphene of about 30 inch in the diagonal direction with grain size ranging from  $20\,\mu\text{m}$  to  $500\,\mu\text{m}$ . As depicted in Figure 1.12 depositing a polymer on the surface of CVD graphene and dissolving the metal layer in acidic solution, it is possible to easily transfer the grown graphene to a new substrate like the standard  $SiO_2$ . For this reason, as well as for the simplicity of the growth process, this technique arises as the most promising for electronic applications. However neither CVD growth, produce graphene with quality comparable to that obtained by micromechanical cleavage, reaching so far mobility values of about  $25,000 \,\mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1}$  at room temperature [55].

**Figure 1.12:** Schematic representation of a standard transfer process of graphene grown on Cu foil onto a target substrate. Picture reproduced from [8].

# **2 High Frequency Electronics**

This chapter makes a review on the high frequency electronics panorama which graphene base technologies are promising for. In section 2.1 is explained the fundamental physics of Metal Oxide Semiconductor Field Effect Transistors (MOSFETs). Section 2.2 describes the principal figures of merit used to classify high frequency devices. An introduction on Graphene-based Field Effect Transistors (GFETs) and the state of the art of their performances is done in section 2.3; finally section 2.4 gives an overview on the limiting factors for high frequency operation of graphene based devices fabricated on silicon-compatible substrates.

The evolution in communications and digital applications have been led to a continuous decrease in size and elaboration time of the electronic devices. As predicted by Gordon Moore after the commercialization of the first microprocessor produced by Intel Corporation in 1971, processor speeds, or overall processing power for chip have been doubling every two years [56]<sup>1</sup>. The transistor is the fundamental building block of modern analog or digital devices, so far principally produced using silicon as a semiconductor material. Is not a coincidence that United States semiconductor industry sales for 2013 reached a record of 305.6 billion of dollars<sup>2</sup>. A transistor is a three ports electrical component which can be used both as an amplifier or a switch. This makes it a perfect candidate for the treatment of analog signal, since they need amplification in order to reduce distortions and losses, as well as the elaboration of digital information which are treated as binary data. Many kind of transistors are currently placed on market but only Field Effect Transistors will be described in this review since nowadays they are the most diffuse type of transistors.

## 2.1 Metal Oxide Semiconductor FETs

A Metal Oxide Semiconductor Field Effect Transistor (MOSFET) consist in a three ports device which is able to modulate the current density flowing through two of this terminals namely, *source* and *drain*, by the application of a voltage ( $V_G$ ) on the remaining *gate* port [57]. Through the years silicon has establish as the best semiconductor for such a kind of device. The structure of a classical silicon nMOSFET is shown in Figure 2.1(a); the two highly doped regions of source and drain are separated by a zone placed under the oxide layer known as channel region. Applying a gate potential

<sup>&</sup>lt;sup>1</sup>This is known as "Moore's Law" since he predict this trend in 1965.

<sup>&</sup>lt;sup>2</sup>Data taken by www.semiconductors.org

(a)

**Figure 2.1:** (a): Sketch of an n-type MOSFET device, based on a p-type substrate. The gate stack is formed by an insulator sandwiched between the substrate and the gate metal electrode. Two highly n-doped regions are implanted at the edges of the channel corresponding to the source and drain electrodes. (b): In the off-state of the MOSFET a negative  $V_G$  induces in the channel an high concentration of holes; the n-p-n double junction prevents the onset of a current. (c): When  $V_G > V_{th}$  in the channel, previously depleted by holes, negative carriers are attracted thus conduction is allowed.

the Metal Oxide Semiconductor structure behave like a capacitor attracting carriers from the silicon bulk toward the channel, here electrons and holes are placed in an electric field, generated through the application of a voltage between source and drain  $(V_{DS})$ , which force them moving in a direction parallel the the channel. The key point for the control of the device is that the bulk and the source/drain regions are doped in an opposite manner: thus for a p-type doped substrate two n-type doped zones are implanted. Hence, whenever a  $V_G$  less then a well defined threshold voltage  $(V_{th})$  is applied, the formed n-p-n double junction don't allow the current flow, thus the MOSFET is in an "off" state (Figure 2.1(b)). When  $V_G$  approaches  $V_{th}$  a depletion zone under the gate stack is created, forcing the holes to go away from this region. Once  $V_{th}$  is reached, an high concentration of electrons are attracted in the channel allowing carriers flow, therefore the MOSFET switch into its "on" state (Figure 2.1(c)). The heavily doped source/drain regions,

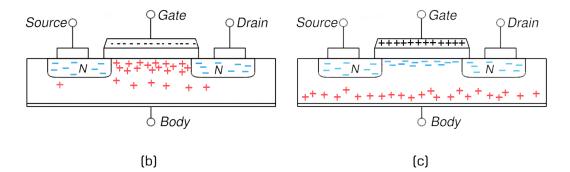

**Figure 2.2:** (a): Typical  $I_D/V_{DS}$  characteristic for n-channel metal oxide semiconductor field effect transistor at constant gate voltages. Two region are distinguishable, for low  $V_{DS}$  the current growth is linear, therefore the MOSFET is said to be in the "ohmic" zone. When  $V_{DS}$  goes beyond the threshold value, the channel pinch-off takes place and the current starts saturate.

(b):  $I_D/V_G$  transcharacteristic for a n-channel MOSFET. If  $V_G < V_{th}$  no current can flow through the channel, but once  $V_G$  approaches  $V_{th}$  the drain current starts growing following a shape that depends on  $V_{DS}$ .

shown in Figure 2.1, are used to make "ohmic" contact to the conductive channel, so that a voltage difference between the source and the drain will result in current flow from the positive voltage at the drain terminal to the negative voltage at the source( $I_D$ ). In the "on" state the drain current is a function of both  $V_G$  and  $V_{DS}$ . The larger the gate voltage, the larger will be the density of electrons in the conduction channel and the larger will be the device drain current. However  $I_D$  can not grow infinitely therefore, as soon as  $V_{DS}$  reaches a specific value, it tends to saturate (Figure 2.2(a)). This is a very important feature for a transistor since, as later explained, the maximum frequency at which it can operate is strictly related to the saturation current. The ability to pilot a current in a MOSFET is a function of some physical parameters. Dimensions, like the channel length (L) as well as the oxide thickness  $(t_{ox})$ , and the carriers mobility  $\mu$ , influence in a direct way  $I_D$ . In a very rough description the drain current is proportional to  $\mu$ and 1/L. Moreover the gate capacitance per unit area of the MOS structure defined as:<sup>3</sup>

$$C_g = \frac{\varepsilon_{ox}}{t_{ox}}$$

determines the ability of the gate to modulate the charges in the channel therefore, the grater the  $C_{ox}$  the less the  $V_G$  required to reach an high current density thus a reduced on-off switching time. Smaller MOSFETs are

$<sup>{}^{3}\</sup>varepsilon_{ox}$  is defined as the *dielectric constant* of the oxide. It is an intrinsic characteristic of any insulator material.

then desirable for several reasons. First of all making smaller transistors allow to pack more and more devices in a given chip area. This results in a chip with the same functionality in a smaller area, or chips with more functionality in the same area. Moreover the frequency at which a MOSFET can operate, as explained in section 2.2, is strongly dependent on the time constant RC. When dimensions are scaled down by an equal factor, the transistor channel resistance does not change, while gate capacitance is cut by that factor. Despite the outcomes, the continuous MOSFETs dimensions reduction have been led to many relevant problems concerning parasitic effects such as *gate-current leakage*, due to the tunneling effect through the oxide layer, carriers velocity saturation, generated by the very high electric field in the channel, and many others. Trying to attenuate this effects the attempt to increase  $C_{ox}$  through the use of insulators with high dielectric constant has been done, but the integration of such materials is not easy with the currently silicon technology [58].

### 2.2 FETs RF performance parameters

The requirement of different characteristic for analog and digital electronics have been led to the develop of two different kind of semiconductor devices: those applied for logic circuits and those used in the radiofrequency (RF) field. Digital electronics is based on highly integrated silicon CMOS technology. The incredible resources invested on it in the last five decades, result in a big barrier for the develop of any other competitive technology. Analog electronic circuits, on the other hand, are not as highly integrated, and thus are more open to newest materials and devices. In analog high-speed applications, FETs should respond quickly to a variation in the gate voltage; this require short gates and fast carriers in the channel. In high frequency applications, transistors are operating in the "on" state and the RF signals to be amplified are superimposed onto the DC gate bias. To discuss the frequency performance of a FET its equivalent circuit, represented in Figure 2.3(a), is analyzed under the assumption imposed by the small signal model. This type of analysis allows the determination of two important metrics namely the cut-off frequency  $(f_T)$  and the maximum frequency of oscillation  $(f_{max})$ . In the equivalent circuit the intrinsic transconductance defined as

$$g_m = \frac{\Delta I_{out}}{\Delta V_{in}} = \left. \frac{\partial I_D}{\partial V_G} \right|_{V_{DS}=constant}$$

(2.1)

quantifies the strength of the gating effect on the channel, while the *output* conductance

$$g_0 = \frac{1}{r_0} = \left. \frac{\partial I_D}{\partial V_{DS}} \right|_{V_G = constant}$$

(2.2)

**Figure 2.3:** (a): Small-signal equivalent FET circuit. Here  $C_{GS}$  and  $C_{GD}$  are respectively the gate-source and the gate-drain capacitance. The intrinsic transconductance,  $g_m$ , is related to the internal small-signal gate-source and drain-source voltages, whereas the output transconductance,  $g_0$ , is related to the applied gate-source and drain-source voltages.

(b): The dependence of the cut-off frequency  $(f_T)$  on the controlling parameter shows a peak in the region where both the transconductance  $g_m$  and the output resistance  $(r_0)$  are high. Pictures taken from [9]

quantifies the drain current variation under a drain-source voltage changing.  $R_D$  and  $R_S$  are parasitic components and they will become important in the discussion of the impact of the contact resistance on the FET performances. The cut-off frequency,  $f_T$ , is the frequency at which the magnitude of the small-signal current gain becomes unity, and is indicative of the highest frequency at which the transistor can operate. Considering only the intrinsic FET equivalent circuit in Figure 2.3(a) it can be ideally calculated as:

$$f_T = \frac{g_m}{2\pi (C_{GS} + C_{GD})}$$

Introducing the parasitic effect, namely resistances and capacitance, the real dependence of  $f_T$  becomes:

$$f_T = \frac{g_m}{2\pi} \frac{1}{(C_{GS} + C_{GD})[g_0(R_S + R_D)] + C_{GD}g_m(R_S + R_D)}$$

(2.3)

As shown in Figure 2.3(b),  $f_T$  peaks deep in the saturation region where the transconductance reaches it maximum whereas the output conductance is at its minimum. The maximum oscillation frequency,  $f_{\rm max}$ , is the frequency at which the maximum power gain equals unity under optimum matching conditions for the input and output impedance.

$$f_{\rm max} \approx \sqrt{\frac{f_T}{2\pi R_G C_{GD}}}$$

(2.4)

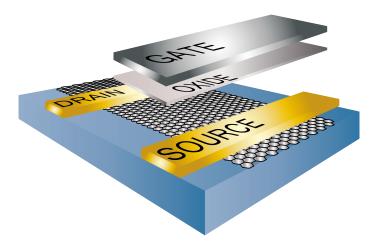

**Figure 2.4:** Structure of a classical GFET. Graphene is first transferred on a substrate chosen for the application which the device is intended for. A thin layer of insulating material is deposited over the channel, then the evaporation of the metal electrodes is performed.

where  $R_G$  is the input (gate) resistance. Since  $f_T$  and  $f_{\rm max}$  are calculated from the ideal conditions of zero load impedance and best impedance matching networks, another parameter need to be introduced in order to better define the high frequency behavior of a device. The open-circuit voltage gain  $A_{vo}$  is directly proportional to the intrinsic gain  $G_{int} = g_m/g_0$ . This became an important figure of merit for that transistors which don't show a saturation current. Roughly a high frequency performances increment could be obtained through the scaling of the transistors dimensions but, the continued miniaturization of the silicon MOSFETs, have been led to adverse "short channel effects" [59] [60]. Some of these can be partially mitigated by using high mobility constituents, such as III-V semiconductors, that would also result in improved device transconductance. For this reason many new materials, including graphene, are currently being studied in order to overcome some problems reaching higher frequency of operation.

### 2.3 Graphene FETs

With silicon-based electronics tending towards its scaling limits, the semiconductor industry is looking for new materials which can replace the silicon FETs. Graphene with its very high mobility and Fermi velocities of electrons offers many advantages as a channel material. Since the observation of a 2D field effect in graphene made by Novoselov et al. [19], the challenge in making powerful graphene based transistors (GFETs) have been opening. Due to the lack of a band-gap in the graphene electronic structure and hence the impossibility to completely switch-off the device, the efforts move towards high frequency devices production. Because of its 2D geometry, is less

**Figure 2.5:** Typical transfer characteristic for two GFETs with large area graphene channels. It is clearly visible the ambipolar conduction: when  $V_G$  is less then the Dirac point,  $E_F$  goes in the valence band and the conduction is performed by holes. Once  $V_G$  goes beyond the Dirac point,  $E_F$  falls in the conduction band and electrons transport is promoted. Picture taken from [9]

likely to suffer from performances degradation due to scaling with respect to devices made using III-V semiconductors. The fabrication of a standard GFET, such as the one depicted in Figure 2.4, involves several generic steps including:

- Preparation of the substrate with graphene on top;

- Deposition of a dielectric material;

- Deposition of the metal electrodes (Gate, Source and Drain);

Graphene electronic properties are really sensitive to interfaces quality both of the substrate and the electrodes; therefore many tricks have been proposed for the execution of all the previous cited steps. Although the realization of back-gated transistors is allowed, this kind of configuration is good for fundamental investigation but not useful for real application. Top-gated graphene FETs, first demonstrated in 2007 [61], represent the preferred option for practical applications.

As pointed out in section 2.1 applying a voltage  $V_{DS}$  between source and drain, the potential varies along the channel, generating an electric field that is responsible of the carriers motion.4 As in classical FETs a

$\xi = -\nabla \Phi$

<sup>4</sup>The electric field  $\xi$  can be expressed as

**Figure 2.6:** (a): GFET characteristic with a sort of saturation like behavior placed between two regions in which current increase linearly with respect to drain voltage.

(b): Schematic representation of the carrier concentration under the topgated region. In point I the channel is entirely p-type and the GFET operate in the linear region. In zone II the drain side of the channel changes carrier type, promoting the recombination between electrons and holes and therefore saturating the current. In zone III the Dirac point, moving toward the source side, promotes the conduction of electron and the current starts growing again. Pictures taken from [10]

variation in the gate voltage  $V_G$ , lead to a modulation of the Fermi level ( $E_F$ ) through the channel under the gate stack. By contrast, unlike the other semiconductors, graphene present an ambipolar field effect, therefore the type of carriers responsible for the conduction depends on the gate voltage. Under the ideally condition of undoped graphene at  $V_G = 0$ , the Fermi level is pinned at the Dirac point, hence there are a few of either carrier type and the conductivity of graphene is minimized. For positive  $V_G$ ,  $E_F$  falls in the conduction band generating a large quantity of electrons that are accelerated by the electric field (Figure 2.5). When a negative  $V_G$  is applied,  $E_F$  shifts to the valence band allowing the conduction of holes. Despite conduction and valence bands are symmetric in graphene, an asymmetry in the transfer characteristic is clearly visible. As will be explain later this effect is attributed to the formation of p-n junctions between the channel and the source/drain regions due to the metal contacts.

where  $\Phi$  is the electric potential that is define as a scalar field.

For high frequency operation a very high  $r_0$  is required. It is not simple to obtain this kind of behavior in graphene FETs because, unlike silicon transistors, they don't reach a pinch-off point and therefore current should be limited only by the velocity saturation of the carriers, obtained only for very high voltages. Despite this some graphene FETs, as depicted in Figure 2.6(a), present an unusual saturation like behavior interposed between two linear regions [10] [62]. For small values of  $|V_{DS}|$  the channel is entirely p-type and the transistor operate in the first linear region. Increasing  $|V_{DS}|$  around a critical point the potential condition at the drain side correspond to the Dirac point promoting the recombination of the carriers and leading to a sort of saturation behavior (zone II).5 Further increasing the potential the Dirac point shift toward the source, switching the conduction type in the channel from p to n (region III). Although reaching a saturation current in graphene transistors is difficult, the very high mobility lead to an high transconductance  $g_m$ . As seen before this is a very important figure of merit for high frequency devices. Due to the V-shape of the transfer curve (Figure 2.5),  $g_m$  peaks near the Dirac point where the slope of the curve is bigger then elsewhere.

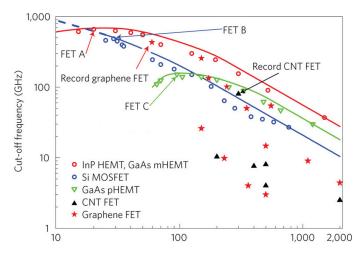

The first experimental demonstration of RF GFET was a 500 nm channel length top-gated FET fabricated using exfoliated graphene and showing a cut-off frequency of about 14.7 GHz [63]. Progress have been achieved in a short period leading actually to GFET with  $f_T$  comparable with the best other RF technologies. Remarkable is the work done by IBM researchers that pushes device performance forward from a cut-off frequency of 26 GHz in 2009 [64], 100 GHz in 2010 [65], 155 GHz in 2011 [66] and finally reaching 300 GHz in 2012 [67]. The actual record of 427 GHz have been reported by Cheng et al. [68] in 2012. So far, despite this very promising results regarding the cut-off frequency, graphene RF transistors have been suffered of a low maximum oscillation frequency that limited the performances of high frequency GFETs-based devices. Recently a 100 nm gate length transistor with an extraordinary high value of  $f_{max}$  (105 GHz) have been published by Feng et al. [69].

As reported by Sordan and Ferrari [70], beside single graphene transistors, different kinds of integrated circuits have already been realized using GFET. From the less complex 6 mixers [71], passing through more complicated voltage amplifiers [72] going to ring oscillators [11] with 12 GFETs inside. Recently IBM researchers demonstrate the powerful of graphene, fabricating a radio frequency receiver performing signal amplification, filter-

<sup>5</sup>Remember that since graphene is a gapeless material recombination can occurs without the emission of any photons, i.e. no energy is involved in this operation.

<sup>6</sup>For an integrated circuit the complexity is defined, as a first order approximation, by the number of transistors from which it is composed.

**Figure 2.7:** *Cut-off frequency versus gate length for graphene FETs, nanotube FETs and three types of radiofrequency FET; the symbols are experimental data points and the lines are a guide to the eye for type A (InP HEMT and GaAs mHEMT), B (Si MOSFET) and C (GaAs pHEMT) devices. The FET A with the highest cut-off frequency of* 660 GHz *is a GaAs metamorphic HEMT (mHEMT) with a* 20 nm *gate. The FET B with the highest cut-off frequency of* 485 GHz *is a Si MOSFET with a* 29 nm *gate. The FET C with the highest cut-off frequency of* 152 GHz *is a GaAs pseudomorphic HEMT (pHEMT) with a* 100 nm *gate. The fastest nanotube device (CNT FET) has*  $f_T = 80$  GHz *and* L = 300 nm, *and the fastest reported graphene MOSFET has*  $f_T = 426$  GHz *and* L = 64 nm. *Picture taken from* [9]

**Figure 2.8:** (a): Ring oscillator produced by Guerriero et al. [11] at the L-NESS laboratories. It is composed by 8 integrated graphene transistors and the maximum frequency of operation goes beyond the GHz barrier. (b) and (c): Images taken from [12] representing the new graphene based integrated circuit (by IBM) working with on a wireless network band of 4.3 GHz; the device was able to receive and restoring a text message without distortions.

ing and downconversion mixing [12]. They were able to receiving and restoring digital text transmitted on a 4.3 GHz carrier signal.

# 2.4 Graphene high frequency limiting factors

There exist some factors that crucial influence the high frequency performance of any FET based device. Commonly they are defined as "parasitic elements", namely capacitance and resistances, resulting from both the physical properties of the materials composing the transistor ("intrinsic" elements), and the interaction between different materials ("extrinsic" elements). As already said the two major figure of merits for evaluate the RF performances of a transistor are the cut off frequency and the maximum oscillation frequency. Many intrinsic and extrinsic elements impact on this two parameters. Since the high interest in integrate graphene base devices in silicon technology, here a discussion on factors that influence high frequency operation for GFETs on silicon-compatible substrates is performed. Particularly this points will be outlined:

- Graphene-substrate interface effects limiting carrier mobility;

- Gate stack planning and fabrication;

- Metal contacts deposition;

## 2.4.1 Mobility

For radio frequency operations an high value of transconductance is desirable.  $g_m$  strongly depends of two factors: one, described by the  $C_g$  parameter, is the capability of the gate to modulate the charges in the channel, whereas the other one, namely the mobility  $\mu$ , specifies the ability of carriers to freely move in graphene. Graphene is famous for reaching the highest mobility values already known, in the order of  $1\,000\,000\,\mathrm{cm^2V^{-1}s^{-1}}$  on "suspended" samples, however when used in real application it result in mobility two orders of magnitude lower. This difference could be explained in principal with two reasons: one is related to the production and transfer of graphene, whereas the other one comes from the physical interaction between the substrate and the graphene itself.