SCUOLA DI INGEGNERIA INDUSTRIALE E DELL'INFORMAZIONE

# Power Optimization Strategies for the Electronic Control of Photonic Integrated Circuits

TESI DI LAUREA MAGISTRALE IN Electronics Engineering - Ingegneria Elettronica

Author: Samuele De Gaetano

Student ID: 964216 Advisor: Prof. Marco Sampietro Co-advisor: Francesco Zanetto Academic Year: 2021-22

## Abstract

In the last years, integrated photonics has emerged as a promising solution for the transmission and processing of optical signals. In particular, Silicon Photonics technological platform represents a significant option in this direction, since it exploits the traditional microfabrication processes of the CMOS technology to implement photonic integrated circuits with low cost and area occupation. However, the main drawback of Silicon as optical material is its high sensitivity to geometrical fabrication mismatches and temperature variations, that hinder the possibility of open-loop photonic operations. Indeed, the working point of each photonic device needs to be precisely controlled and stabilized to ensure that the overall optical functionality matches the design specifications. To this end, a real-time electronic closed-loop control has to be implemented, by reading on-chip sensors and driving integrated actuators with a suitable feedback law.

The maturity reached by Silicon Photonics has boosted its adoption in the telecommunication commercial field, leading to the realization of increasingly complex photonics systems. The electronic control thus has to address an increasing number of photonic devices on the same chip. A multichannel FPGA-based electronic system, called Helios 3, has been specifically designed in order to handle up to 144 photodetectors and actuators, allowing to control complex photonic structures. The new electronic platform has been designed with a flexible modular architecture, made of a motherboard that is completed by plugin modules that can be reconfigured to change the number and type of sensors and actuators operated on the photonic chip.

Considering the abundant number of channels that need to be driven/acquired, power efficiency becomes a critical aspect. The power supply of the system has thus been realized with an optimized module. The employment of DC/DC converters, with respect to less efficient linear regulators, permitted to avoid the use of bulky benchtop power supplies and efficiently deliver to the system up to 90W from a PC charger. The supply module is connected to the Helios 3 motherboard with vertical connectors, protecting the whole electronic system by EMI generated by the switching regulators. The circuit has been thoroughly tested and validated, verifying its correct design and operation.

Furthermore, a new version of the actuation module has been designed and verified. This pluggable board features 16 actuation channels that can be connected to two types of actuators, i.e. thermal phase shifters specifically targeting the Silicon Nitride platform and the innovative MEMS actuators, that promise to solve the power consumption bottleneck afflicting thermal actuators. The two kind of devices share the need of high operating voltages, therefore a circuit able to correctly drive them has been designed by employing a local high-voltage DC/DC converter. The module has been completely validated, including the VHDL firmare required to operate it with the FPGA.

The complete Helios 3 instrument is now ready to be employed in actual experiments and control cutting-edge photonic structures of relevant complexity, performing advanced optical functionalities.

**Keywords:** electronic system, integrated photonics, MEMS, Silicon Nitride, modular architecture, FPGA, power electronics.

## Abstract in lingua italiana

Negli ultimi anni, la fotonica integrata è emersa come una soluzione promettente per la trasmissione e l'elaborazione di segnali ottici. In particolare, la piattaforma tecnologica Silicon Photonics rappresenta un'opzione significativa in questa direzione, poiché sfrutta i tradizionali processi di microfabbricazione della tecnologia CMOS per implementare circuiti integrati fotonici a basso costo e a bassa occupazione di area. Tuttavia, il principale svantaggio del silicio come materiale ottico è la sua elevata sensibilità agli errori di fabbricazione geometrica e alle variazioni di temperatura, che ostacolano la possibilità di operazioni fotoniche ad anello aperto. Infatti, il punto di lavoro di ogni dispositivo fotonico deve essere controllato e stabilizzato con precisione per garantire che la funzionalità ottica complessiva corrisponda alle specifiche di progetto. A tal fine, è necessario implementare un controllo elettronico ad anello chiuso in tempo reale, leggendo i sensori on-chip e pilotando gli attuatori integrati con un'adeguata legge di retroazione.

La maturità raggiunta dalla fotonica del silicio ne ha favorito l'adozione nel settore commerciale delle telecomunicazioni, portando alla realizzazione di sistemi fotonici sempre più complessi. Il controllo elettronico deve quindi gestire un numero crescente di dispositivi fotonici sullo stesso chip. Un sistema elettronico multicanale basato su FPGA, chiamato Helios 3, è stato appositamente progettato per gestire fino a 144 fotorivelatori e attuatori, consentendo di controllare strutture fotoniche complesse. La nuova piattaforma elettronica è stata progettata con un'architettura modulare flessibile, costituita da una scheda madre che è completata da moduli plug-in che possono essere riconfigurati per cambiare il numero e il tipo di sensori e attuatori operanti sul chip fotonico.

Considerando l'elevato numero di canali da pilotare/acquisire, l'efficienza energetica diventa un aspetto critico. L'alimentazione del sistema è stata quindi realizzata con un modulo ottimizzato. L'impiego di convertitori DC/DC, rispetto ai regolatori lineari meno efficienti, ha permesso di evitare l'uso di ingombranti alimentatori da banco e di fornire al sistema in modo efficiente fino a 90W da un caricatore per PC. Il modulo di alimentazione è collegato alla scheda madre Helios 3 con connettori verticali, proteggendo l'intero sistema elettronico dalle EMI generate dai regolatori switching. Il circuito è stato accuratamente testato e validato, verificandone la corretta progettazione e il funzionamento. Inoltre, è stata progettata e verificata una nuova versione del modulo di attuazione. Questa scheda collegabile dispone di 16 canali di attuazione che possono essere collegati a due tipi di attuatori, ovvero gli sfasatori termici specificamente destinati alla piattaforma di nitruro di silicio e gli innovativi attuatori MEMS, che promettono di risolvere il collo di bottiglia del consumo di energia che affligge gli attuatori termici. I due tipi di dispositivi condividono la necessità di alte tensioni operative, pertanto è stato progettato un circuito in grado di pilotarli correttamente impiegando un convertitore DC/DC locale ad alta tensione. Il modulo è stato completamente validato, compreso il firmare VHDL necessario per farlo funzionare con l'FPGA.

Lo strumento Helios 3 completo è ora pronto per essere impiegato in esperimenti reali e controllare strutture fotoniche all'avanguardia di notevole complessità, eseguendo funzionalità ottiche avanzate.

**Parole chiave:** sistema elettronico, fotonica integrata, MEMS, Nitruro di Silicio, architettura modulare, FPGA, elettronica di potenza.

## Contents

| Abstract                    | i   |

|-----------------------------|-----|

| Abstract in lingua italiana | iii |

| Contents                    | v   |

| 1                     | Introduction 1 |         |                                        |    |

|-----------------------|----------------|---------|----------------------------------------|----|

| 1.1 Silicon Photonics |                |         |                                        | 2  |

|                       |                | 1.1.1   | Waveguides                             | 2  |

|                       |                | 1.1.2   | Directional Coupler                    | 3  |

|                       |                | 1.1.3   | Mach-Zehnder Interferometer            | 4  |

|                       |                | 1.1.4   | Ring Resonator                         | 5  |

|                       | 1.2            | Electro | onic control of PICs                   | 6  |

|                       |                | 1.2.1   | Sensors                                | 7  |

|                       |                | 1.2.2   | Thermal actuators                      | 8  |

|                       |                | 1.2.3   | MEMS actuators                         | 9  |

|                       |                | 1.2.4   | Dithering Technique                    | 10 |

|                       | 1.3            | Other   | photonic technologies: Silicon Nitride | 12 |

| <b>2</b>              | Har            | dware   | control system                         | 15 |

|                       | 2.1            | Helios  | 3 architecture                         | 16 |

|                       |                | 2.1.1   |                                        | 16 |

|                       |                | 2.1.2   | Motherboard                            | 17 |

|                       |                | 2.1.3   | FPGA                                   | 19 |

|                       | 2.2            | Plugga  |                                        | 20 |

|                       |                | 2.2.1   | Photodiodes acquisition module         | 20 |

|                       |                | 2.2.2   | -                                      | 21 |

|                       |                |         |                                        |    |

v

$\mathbf{v}$

| 3.1 | Introd                               | uction $\ldots \ldots 2$ | 5 |

|-----|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---|

| 3.2 | 2 Design guidelines and power budget |                                                                                                                                   | 6 |

| 3.3 | Power                                | supply description                                                                                                                | 7 |

|     | 3.3.1                                | Step-down converter                                                                                                               | 8 |

|     | 3.3.2                                | Step-down converter for Inverting Outputs                                                                                         | 0 |

|     | 3.3.3                                | EMI Input filtering and Output filtering                                                                                          | 2 |

|     | 3.3.4                                | Protection measures                                                                                                               | 3 |

|     | 3.3.5                                | PCB layout                                                                                                                        | 4 |

| 3.4 | Power                                | module validation                                                                                                                 | 7 |

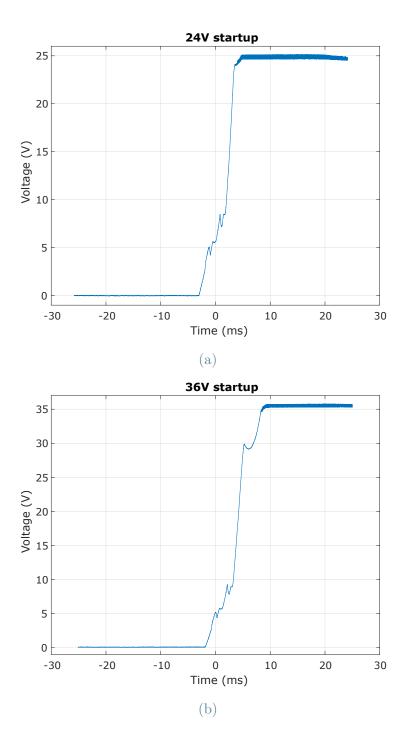

|     | 3.4.1                                | Start-up transient                                                                                                                | 7 |

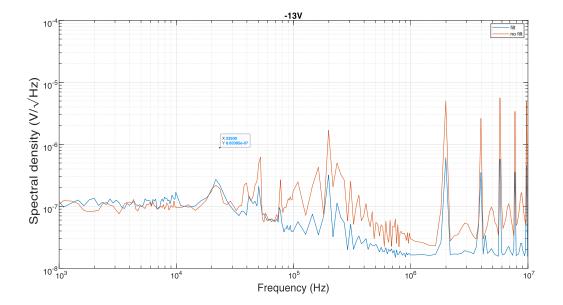

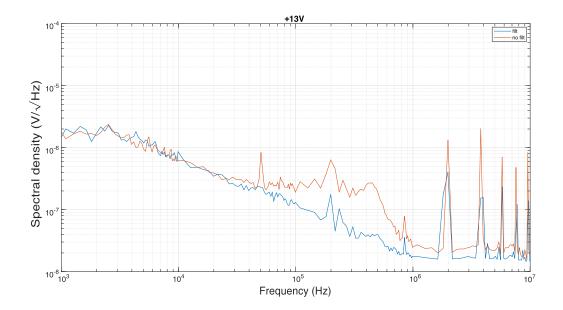

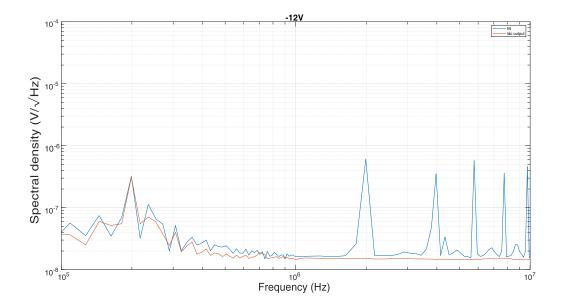

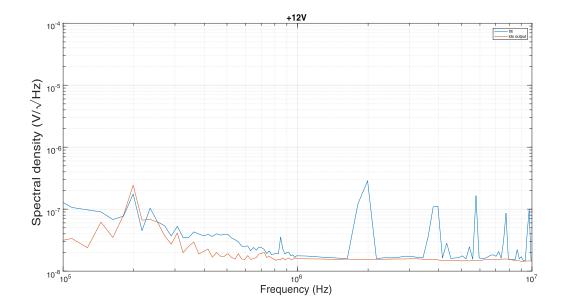

|     | 3.4.2                                | Output ripple and spectral response                                                                                               | 9 |

|     | 3.4.3                                | Filtering measurement                                                                                                             | 2 |

| н   | rh Pow                               | er - High Voltage actuation module 4'                                                                                             | 7 |

| 4.1 |                                      | uction                                                                                                                            |   |

| 1.1 | 4.1.1                                | Module description and requirements                                                                                               |   |

| 4.2 |                                      | supply                                                                                                                            |   |

|     | 4.2.1                                | Boost converter                                                                                                                   |   |

|     | 4.2.2                                | Linear regulators                                                                                                                 |   |

| 4.3 | Actua                                | tion Chain $\ldots \ldots 5$           | 1 |

|     | 4.3.1                                | Digital-to-Analog Converter                                                                                                       | 1 |

|     | 4.3.2                                | Driver                                                                                                                            | 2 |

|     | 4.3.3                                | Monitoring circuit                                                                                                                | 3 |

|     | 4.3.4                                | Protection switches                                                                                                               | 6 |

|     | 4.3.5                                | Digital pins distribution                                                                                                         | 6 |

|     | 4.3.6                                | Power dissipation                                                                                                                 | 7 |

|     | 4.3.7                                | PCB Layout                                                                                                                        | 8 |

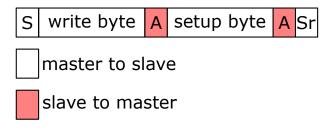

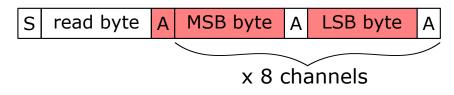

| 4.4 | Firmw                                | vare                                                                                                                              | 1 |

|     | 4.4.1                                | DAC                                                                                                                               | 1 |

|     | 4.4.2                                | ADC                                                                                                                               | 3 |

| 4.5 | Actua                                | tion module validation                                                                                                            | 4 |

|     | 4.5.1                                | Power supply measurement                                                                                                          | 4 |

|     | 4.5.2                                | Driver transfer function                                                                                                          | 8 |

|     | 4.5.3                                | Noise                                                                                                                             | 8 |

|     | 4.5.4                                | Startup output protection circuit                                                                                                 | 0 |

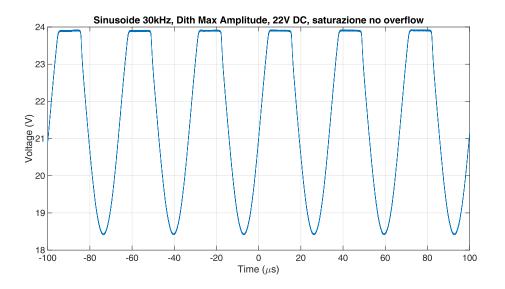

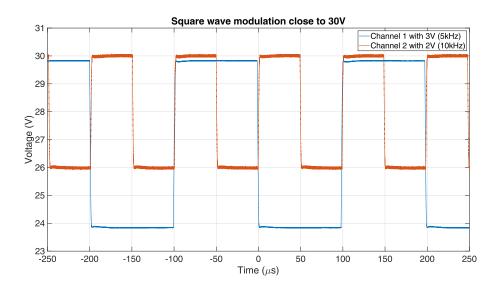

|     | 4.5.5                                | Generation of actuation signals                                                                                                   | 2 |

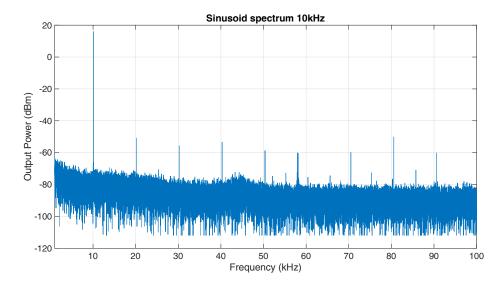

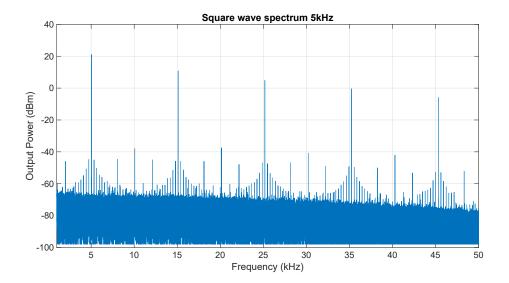

|     | 4.5.6                                | Frequency spectrum of the generated signals                                                                                       | 3 |

|     |                                      | Generation of actuation signals                                                                                                   | 7 |

|                | 4.5.7          | Current monitoring circuit  | 75 |

|----------------|----------------|-----------------------------|----|

| <b>5</b>       | Conclusi       | ons and future developments | 79 |

|                | 5.0.1          | Future developments         | 81 |

|                |                |                             |    |

| Bibliography 8 |                |                             | 83 |

|                |                |                             |    |

| Lis            | st of Figu     | res                         | 87 |

| Lis            | List of Tables |                             |    |

| Ri             | ngraziam       | enti                        | 93 |

Over the last 70 years, the fabrication process of electronic circuits has been constantly improved, resulting in ever increasing complexity, density, and speed of integrated circuits (IC). As more devices are squeezed into the same silicon area, a problem with metal connections arise: while the transistors on a chip become quicker as the technical dimension reduces, the wires cannot keep the same pace, since their intrinsic resistance and capacitance limit the signal bandwidth. Indeed, aspect ratio of metal lines limits the maximum communication speed, since it can be demonstrated that bit-rate capacitance of a metallic line of cross section A and length L is proportional to  $A/L^2$  [1]. Furthermore, because the operating frequency rises with scaling, total chip power dissipation is almost entirely accounted for by the power required to drive the metallic interconnections.

Using optical links and all-optical signal processors is a good way to bypass these restrictions [2]. In fact, they can operate at greater data rate while using less power than traditional electronics. In addition, photonic devices are less vulnerable to electromagnetic field interference, which may be a concern in electronic communication systems. While photonics has already been employed for long range telecommunications, where fiber optics have completely superseded coaxial cables, the adoption of this technology for short distance interconnections requires the integration of optical devices in compact chips, possibly exploiting currently existing manufacturing process, to reduce cost and size and become attractive over the more traditional electronic components.

Because optical qualities are as important as electrical ones, many integrated solutions, each with advantages and disadvantages, have been proposed, including Silicon Nitride, Indium Phosphide, Lithium Niobate, and, of course, Silicon. Over the last decade, Silicon Photonics (SiP) has become one of the most important technological platforms for photonic integrated circuits (PICs) [3]. Primarily, it owes its success to competitive optical properties obtained with a CMOS-compatible fabrication process. However, these features come at the price of a high sensitivity of silicon photonic devices to temperature variations and fabrication geometrical mismatches, that can impair stand-alone PIC functioning. In the last years, the realization of closed-loop electronic systems, able to compensate the structural defects and stabilize each device in different thermal conditions, has enabled the operation and control of complex Silicon Photonics structures. As a result, the scale of photonic circuits has increased, requiring improved control mechanisms to fully leverage the capabilities of Silicon Photonics.

## **1.1.** Silicon Photonics

In addition to CMOS compatibility, Silicon presents significant optical properties: Silicon transparency window extends in the Infrared spectrum region, from 1000 nm to 7000 nm, including typical optical telecommunication bands, i.e. O-band ( $\lambda = 1300nm$ ) and C-band ( $\lambda = 1550nm$ ). Today, Silicon Photonics products are built on Silicon-on-Insulator (SOI) wafers: because of the high refractive index contrast ( $\Delta = \frac{n_{Si} - n_{SiO_2}}{n_{Si}} \simeq 0.6$ ) produced by the combination of Silicon ( $n_{Si}=3.45$ ) and Silicon Dioxide ( $n_{SiO_2}=1.45$ ), it is possible to design waveguides with a very tiny footprint and a short bending radius.

## 1.1.1. Waveguides

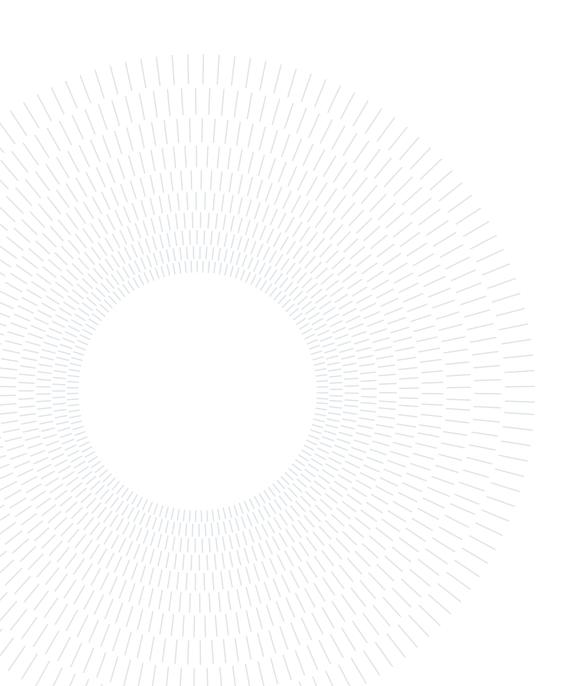

Waveguides are the fundamental structures that transmit light around a photonic chip. SOI waveguides are typically built with a slightly p-doped Silicon core surrounded by  $SiO_2$  cladding, allowing to exploit total reflection and entrap the light inside them with low loss (around  $2 \sim 3db/cm$ ). Different waveguide designs are employed depending on their applications: the buried format (Fig. 1.1aa) is utilized for optical routing, while the rib shape (Fig. 1.1ab) with lateral Si slabs allows for the deposition of metal electrodes, employed in electro-optic devices. Inside this optical structure, travelling modes could be attenuated by scattering losses associated with sidewall roughness and local defects. Indeed, it is possible to describe the propagated electric field inside a waveguide of length L with the following expression:

$$E = E_0 \cdot e^{-j \cdot \Delta \phi} = E_0 \cdot e^{-j \frac{2\pi \cdot L_{opt}}{\lambda}} \cdot e^{-\alpha \cdot L}$$

(1.1)

where  $\Delta \phi$  represents the phase accumulated by the light after an optical path  $L_{opt}$  defined as:

$$L_{opt} = L \cdot n_{si} \tag{1.2}$$

and  $\lambda$  is the wavelength,  $\alpha$  the absorption coefficient of the waveguide,  $n_{si}$  the refraction coefficient of silicon.

Figure 1.1: 3D view and cross-section of buried (a) and rib (b) waveguides with typical geometrical specs

## 1.1.2. Directional Coupler

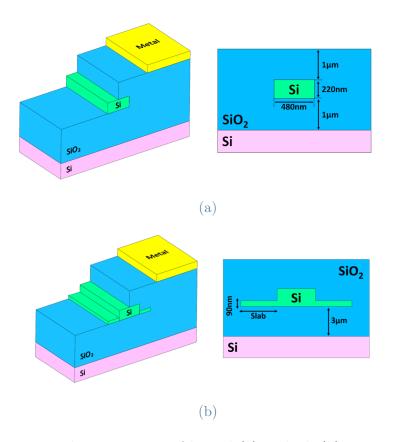

The ability to split or combine two or more guided optical fields is a necessary prerequisite for creating components with more sophisticated functionalities than waveguides. In integrated optics, the directional coupler is the basic component to perform this operation. As indicated in Fig. 1.2, the directional coupler has four ports and it is constituted by two waveguides, completely decoupled in proximity of the inputs and the outputs, that are coupled in the central region of length  $L_c$ . Power coupling between the two waveguides is possible thanks to the interaction with the evanescent field of the propagating signals, so that light pulses can be transferred from one waveguide to the other.

Figure 1.2: Schematic view of a directional coupler.

If the two waveguides are perfectly identical, i.e. they support the same fundamental mode, the directional coupler is *synchronous* and the relation between  $P_{bar}$  (power that comes out of the same waveguide of the input) and  $P_{cross}$  (power exiting from the coupled waveguide) can be described as:

$$P_{bar} = \sin^2(k \cdot L_c) \tag{1.3}$$

$$P_{cross} = \cos^2(k \cdot L_c) \tag{1.4}$$

where k is the coupling coefficient of the device. This parameter depends on component design choices, i.e. the gap between the waveguides or their shape. As equations (1.3) and (1.4) highlight, the transfers function are periodic and the complete power transfer is possible for  $kL_c = \frac{\pi}{2} + N\pi$ . The most common directional coupler used in integrated optics is the -3db coupler which allows to equally split the input light power to the output waveguides  $(kL_c = \frac{\pi}{4})$ .

## **1.1.3.** Mach-Zehnder Interferometer

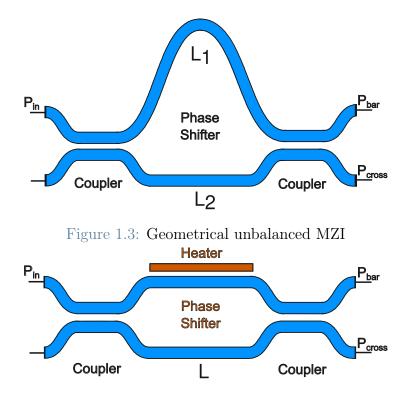

The Mach-Zehnder interferometer (MZI) is the most basic filter that can be constructed in integrated optics [4]. It features a sinusoidal transfer function, which is not ideal for filtering WDM (*Wavelength Division Multiplexing*) channels, but it provides the basis for creating amplitude and phase filters with good spectral properties. This filter is implemented by two -3db directional couplers, linked by two waveguides with different optical path  $L_{opt}$ : the phase shift  $\Delta \phi$  introduced in this region determines the interference at the output directional coupler and therefore the power ratio at the two outputs. As depicted by Fig. 1.3 and 1.4, the phase shift  $\Delta \phi_{MZ} = \phi_1 - \phi_2 = \frac{2\pi}{\lambda} \cdot \Delta L_{opt}$  can be obtained by waveguides of different length ( $\Delta L_{opt} = n \cdot \Delta L$ ) or waveguides of same length and different refractive index ( $\Delta L_{opt} = \Delta n \cdot L$ ).

Employing the same terminology of the directional coupler, the two output powers can be described by:

$$P_{bar} = \sin^2 \left(\frac{\Delta \phi_{MZ}}{2}\right) \tag{1.5}$$

$$P_{cross} = \cos^2\left(\frac{\Delta\phi_{MZ}}{2}\right) \tag{1.6}$$

As made evident by the two equations, the transfer function of a MZI is really similar to that of a directional coupler, however, while for the latter the periodicity is proportional to the  $kL_c$ , for a MZI it is proportional to  $\Delta L_{opt}$ . This relation makes MZI more robust and controllable than a directional coupler: indeed, MZI can be considered a photonic tunable device since it's possible to modify the optical path unbalance, thus changing the

Figure 1.4: Tunable MZI with thermo-optic actuation mechanism

filter transfer function, by acting with some type of actuation mechanism.

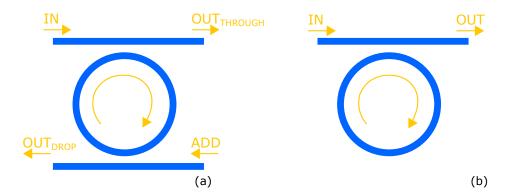

## 1.1.4. Ring Resonator

Ring Resonator (RR) is another typology of integrated photonic device that implements a Infinite Impulse Response (*IIR*) filter. As shown in Fig. 1.5a, the ring is built with a circular waveguide and two directional couplers, that allow the coupling with the input and output waveguides. The four ports of the device are *In*, *Add*, *Through* and *Drop*. The functioning principle is pretty straightforward: if the input signal wavelength is an integer sub-multiple of the ring circumference (resonance condition), the light couples to the ring and exits from the *Drop* port, otherwise it propagates towards the *Through* port. The *Add* port can be used to add another signal to the *Through* port, always respecting the condition of resonance: with this configuration, the ring resonator acts as *Optical Add Drop Multiplexer (OADM)* [5]. If the Drop waveguide is not present (Fig. 1.5b), the ring resonator performs a notch filtering: in this case, the resonating signal is entrapped inside the ring and dissipated by its losses, due to the tight bending radius of the ring.

The optical response of the device is periodic since the resonating condition occurs when the input wavelength is an integer sub-multiple of the ring optical path. Therefore, figures of merit to describe the performance of this filter are the *Free Spectral Range* (FSR), i.e. the distance between two consecutive resonating frequencies, and the *Finesse* (F), i.e. the ratio between FSR and bandwidth of the filter, which gives measure of the filter selectivity.

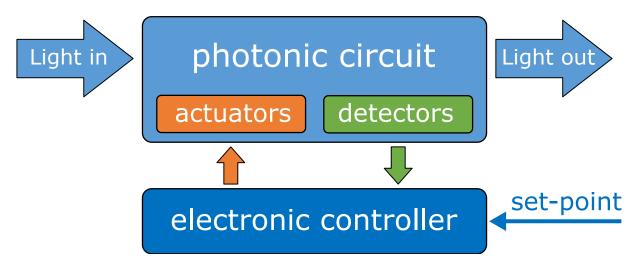

As with the MZI, actuation mechanisms can make the ring resonant frequency tunable and enable advanced operations, such as tunable delay lines [6] (Fig. 1.6): signals can be delayed by a chain of ring resonator since they have to complete multiple roundtrips before reaching the output waveguide. The more the rings are locked on one resonating frequencies, the more the delay adds up.

Figure 1.5: Ring resonator as a) OADM and b) Notch filter

Figure 1.6: Tunable delay lines with 4 locked rings.

## **1.2.** Electronic control of PICs

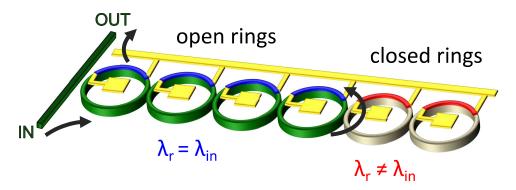

As pointed out before, Silicon Photonics devices have to be tuned in order to accomplish their theoretical purpose or to modify their functionality at run-time [7]. Fabrication imperfections and thermal instabilities can cause shifts of spectral response, if centered around  $\lambda = 1550 nm$ , in the order of 1 nm for 1 nm geometrical mismatch or 10 K temperature change [8]. In order to assess the behaviour of a certain PIC during its operation,

sensors need to be placed in the most suitable parts of the chip. The information acquired in this way can then be used to perform a closed-loop control action, by properly driving on-chip actuators so that the chip behaviour matches a certain set-point [9]. The simplified scheme of the control loop is illustrated in Fig. 1.7.

Figure 1.7: Schematic view of the closed-loop control

The electronic control layer can be exploited to:

- Stabilize the photonic components in temperature-varying working environments.

- Tune the device in order to compensate fabrication geometrical defects.

- Completely reconfigure the interferometric devices (*MZI*, *RR*), to dynamically change the functionality of a photonic chip.

The most common sensors, actuators and control techniques are described in the following sections.

## 1.2.1. Sensors

Because of their simple integration with SOI technology process, Germanium photodiodes are the most common on-chip sensors, capable of extracting the information of the working state of photonic devices with good sensitivity [10]. Germanium is a really good candidate for implementing sensors in Silicon Photonics since it's a good absorber along the C-band: the small energy gap of this material translates in fact into a responsivity around 1A/Wat 1550 nm, that leads to the generation of large electrical signals easy to be detected.

Obviously, the number and placement of photodiodes in a PIC have to be tailored to the specific application, since each detector absorbs part of the travelling optical power. In this

sense, the sensors are conveniently positioned on the unused branch of the interferometric components, in order to not extract too much light from the photonic circuit. Similarly, the amount of employed photodiodes has to be limited to the minimum needed to correctly monitor the state of the PIC.

## **1.2.2.** Thermal actuators

As mentioned before, the main photonic devices are interferometric, therefore the desired optical response is obtained by controlling the relative phase difference accumulated by two light beams that are travelling on different branches. In Silicon, this phase difference  $\Delta \phi$  is directly dependent on the temperature at which the device is operating, since the Silicon refractive index is highly temperature sensitive [11], as shown by the expression of the thermo-optic coefficient (TOC):

$$TOC = \frac{\partial n}{\partial T} = 1.86 \cdot 10^{-4} \quad [1/K] \tag{1.7}$$

This could be considered a drawback because an external control mechanism is required to steady the device. At the same time, this property is exploited to actively manage the operating point of MZIs or RRs, using a closed-loop electrical system, opening the possibility to realize tunable and reconfigurable PICs.

Thermal actuators, typically called *heaters*, are therefore integrated close to the waveguides to define the behaviour of photonic devices. They are usually titanium resistors, with a typical resistance of hundreds of Ohm ( $200 \simeq 400\Omega$ ), deposited at a distance of around 700 nm from the core, to minimize the interaction between the metal and the evanescent field of light. Due to the Joule effect, these actuators heat up when driven by a voltage, locally altering the refractive index and thus regulating the phase shift of the travelling modes. To thermally isolate a piece of the circuit and increase heater efficiency while reducing thermal cross-talk, several foundries currently provide the option of excavating deep trenches in the  $SiO_2$  cladding.

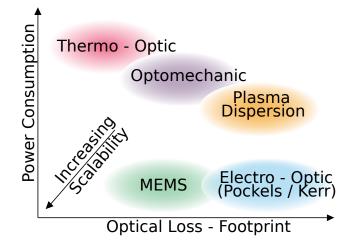

This approach, although being straightforward, has some of problems. The most obvious one is that a single heater uses a significant amount of power (a few mW to tens of mW) to run. Hence, the promised power-efficient solution for short link communications cannot be achieved with photonic circuits that rely on heaters. A lot of research is being put into the investigation of new actuation mechanism to get around the criticalities mentioned. Fig. 1.8 depicts a visual comparison of available tuning methods in terms of feasibility for use in large-scale PICs, showing that optical efficiency of power-hungry heaters could be also mimicked by other type of actuators, such as MEMS actuators.

Figure 1.8: Tuning mechanism comparison from a scalability perspective

## **1.2.3.** MEMS actuators

Optical micro electro-mechanical systems (MEMS) are a potential category of devices that could solve the aforementioned problem of power dissipation of thermal actuators. MEMS rely on electromechanical actuation to cause a change in the optical characteristics of a waveguide, with low power dissipation [12]. Recalling equation 1.1, the propagation of a guided mode can be modified by acting on the refractive index of the waveguide or on the absorption of the optical material. In this sense, MEMS actuators perform a modification of these two parameters with the following mechanisms:

- Because compressive and tensile strain affect both parameters, a tunable phase shifter may be realized using a single waveguide subject to mechanical forces [13].

- Displacement or approach of a piece of waveguide to the one where light is travelling can also induce a modification of refractive index, and it is therefore the most common way to realize tunable directional couplers [14].

Generally, the displacements induced by MEMS actuators are in the order of tens of nanometers to tens of micrometers, obtained with *electrostatic* or *piezoelectric* mechanisms [15]. Both the actuator types are driven by an electric field applied to two electrodes, without consuming of any static power.

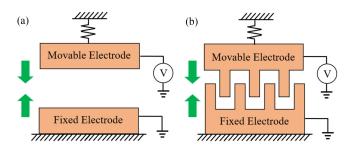

The most popular MEMS actuators are electrostatic actuators. They exploit the attractive force between charged plates of a capacitor, where at least one plate is free to move to achieve displacement. This attractive force is counterbalanced by a mechanical spring force, so that in equilibrium conditions a fixed displacement dependent on the potential difference is obtained. As depicted in Fig.1.9, the two most prevalent capacitor shapes

Figure 1.9: Electrostatic actuators schematic view: a) Parallel plate and b) Comb drive electrodes

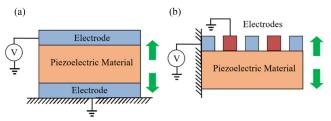

Figure 1.10: Piezoeletric actuators schematic view: a) Sandwiched electrodes and b) Coplanar electrodes

are *parallel plate* and *comb drive* configurations.

Piezoelectric actuators rely instead on the piezoelectric effect, which occurs when a voltage is applied across a piezoelectric material causing strain: in both the electrodes geometries shown in Fig. 1.10, the strain is generated in the horizontal direction, but, since the materials are laterally confined, they stretch vertically.

The adoption of these two types of actuation requires to face some challenges. Regarding the electrostatic actuators, the fabrication of high-aspect ratio structures in SOI is difficult to obtain, making it hard to use comb-drive electrodes without employing complex manufacturing processes. On the other hand, the integration of piezoelectric material in the SOI stack is difficult since complex fabrication steps are required. Furthermore, both architectures require high voltages to obtain relevant phase shifting properties: couplers and switches have a wide range of actuation voltages, from 5 V for devices based on cavities to the more popular range of 30 to 50 V for large waveguide structures. Such high voltages need specialized electronics to be handled. Luckily, the very low current needed to drive the actuators simplifies the electronic design.

## 1.2.4. Dithering Technique

The sensors and actuators described in the previous paragraph are the interface between electronic and photonic domain. To close the control loop, the information acquired with

the sensors needs to be translated into an operating voltage for the actuators. There are several approaches that can be used for this purpose, one of the most commonly used being the dithering technique.

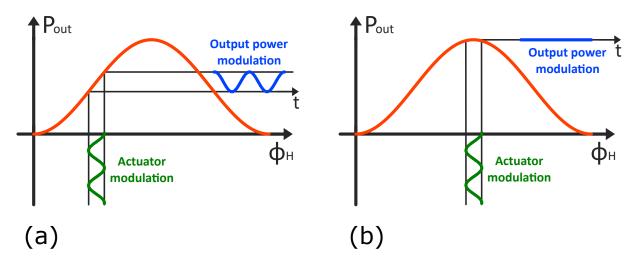

The dithering technique is a control algorithm that permits to simultaneously tune and stabilize complex photonic systems [16]. It exploits a small modulation of the actuators voltage to retrieve the information of first derivative of a photonic device transfer function. This quantity can be advantageously used to lock an optical component in the stationary points (maximum or minimum) of its transfer function without the need of prior calibration procedures, a relevant advantage when the optical complexity scales up. Indeed, the power at the output of any device can be maximized or minimized by driving to zero the dithering information, regardless of the absolute amount of light in the system.

Figure 1.11: Theory of operation of the dithering approach. A modulation of the actuator signal causes an oscillation in the output power whose amplitude depends on the derivative of the transfer function of the device under investigation. The output power modulation depth is maximum on the device slope (a) and zero in stationary points (b).

## Principle of operation

The dithering technique is accomplished by adding a small and slow sinusoidal signal (usually in the kHz range) to the actuation voltage delivered to the actuators. As shown by Figure 1.11, a modulation of the phase shift applied to a photonic interferometric device translates into a modulated output optical power. The modulation depth depends on both the amplitude of the sinusoidal signal and on the slope of the transfer function around its bias point. Indeed, the output power can be written as:

$$P_{OUT} = P_{OUT}(\Phi_{H,BIAS}) + P_{dith}sin(2\pi f_{dith}t)$$

(1.8)

where

$$P_{dith} = \Phi_{dith} \cdot \left. \frac{\partial P_{OUT}}{\partial \Phi_H} \right|_{\Phi_H = \Phi_{H,BIAS}}$$

(1.9)

and  $\Phi_H$  is the phase shift induced by the actuator,  $\Phi_{H,BIAS}$  is the initial bias phase shift,  $\Phi_{dith}$  and  $f_{dith}$  are the amplitude and frequency of the dithering signal, respectively.

The output power is then sensed with a photodetector and the modulated information is extracted with the lock-in technique, by demodulating the acquired signal with a reference at  $f_{dith}$ . This information is then used to modify the actuator bias point until  $P_{dith}$  is zeroed, thus reaching the desired stationary point. Maxima and minima can be both targeted simply by inverting the sign of the acquired dithering signal, since the lock-in readout maintains the sign of the derivative information.

## 1.3. Other photonic technologies: Silicon Nitride

While Silicon Photonics has become the main technology platform for PICs, potential alternative compounds that meet the same essential requirements as the SOI stack, i.e., high index contrast and CMOS integration, are being investigated with growing interest [17]. There are a number of reasons why SOI may not always be the ideal choice for device functioning and performance, one of the main being the need to operate in spectral regions where silicon or silicon oxide are absorbers.

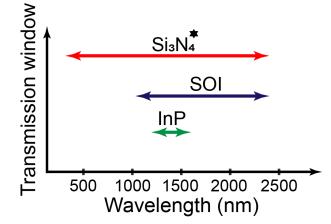

Silicon Nitride  $(Si_3N_4, SiN)$  is a significant option in this regard since it features a moderate index contrast ( $\Delta \simeq 2$ ) and it can be manufactured with CMOS-compatible processes [18]. In addition, as depicted in Fig. 1.12, this material is transparent throughout the majority of the visible spectrum up to the mid infrared (2.3  $\mu m$ ), thus extending the range of wavelengths that can be employed as compared to Silicon Photonics. Moreover, SiN can be grown on silicon wafers that are cheaper than the SOI ones, making the material more cost-effective for some photonic applications.

The medium-high refractive index contrast is also an excellent compromise between PIC design compactness and power loss due to scattering effects and absorption. Indeed, the medium refractive index contrast of SiN reflects into waveguides with larger bend radius (~  $75\mu m$ ) and width (~  $1.2\mu m$ ) as compared to SOI waveguides, that usually

Figure 1.12: Transparency window for typical photonics technologies

feature ~  $5\mu m$  radius and ~ 450nm width. On the other hand, power losses are directly proportional to  $\Delta n^2 = \Delta n_{core}^2 - \Delta n_{cladding}^2$ , making SiN an excellent low-loss material  $(\alpha_{dB} \simeq 1 db/cm)$  [19].

Silicon Nitride waveguides also feature a TOC roughly one order of magnitude smaller than Silicon Photonics. This property is exploited to manufacture photonic chips that are less sensitive to thermal variations and therefore require simpler electronic control. However, when the chip functionality needs to be tuned by means of thermal actuators, a larger current budget is needed to effectively change the refractive index. Indeed, the same refractive index change is obtained with a  $\sqrt{10}$  times larger current than in Silicon Photonics, thus requiring to carefully design the driving electronics. In the next chapters, an actuation module for SiN heaters and MEMS actuators is proposed, taking into account the current requirements of SiN and the high driving voltages of MEMS devices.

As previously stated, photonic chips don't operate as stand-alone devices: an electronic system has to be used to implement a closed-loop control and to stabilize the functioning of each photonic component. Indeed, shifts in the frequency response, caused by temperature variations and fabrication defects, have to be monitored and compensated in real-time.

In this chapter, the overall electronic system, which main goal is to monitor the optical circuitry and tune it into the specific operating regime, is described. It is possible to summarize the complete architecture with the following scheme:

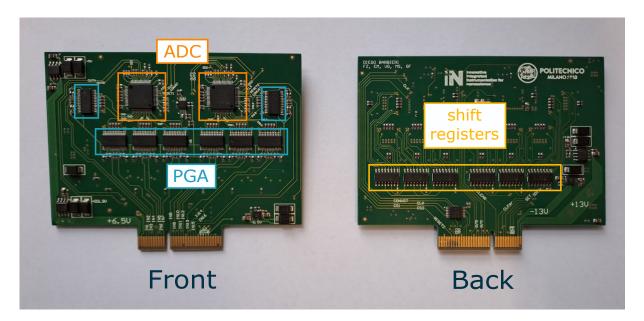

- Electronic front-end: it is implemented on a interface board in order to ease the connection between photonic chips and electronic system. It provides a first amplification of the photodetector signals and the electrical connections to the chip.

- **Read-out chain**: the signals coming from the analog front-end are further amplified by Programmable Gain Amplifiers, filtered and digitally acquired by ADCs.

- **Digital signal processing**: an FPGA is the digital core responsible for implementing the closed-loop control law. It realizes the filtering and processing of the acquired information and generates the control signals to minimize the functionality errors of the photonic components. Furthermore, it handles the communication between user (personal computer) and electronic system.

- Actuation chain: it handles the driving of the different actuators, principally *heaters* and MEMS structures. This chain translates the digital command given from the FPGA into driving voltage waveforms (DC or modulated signals) through the use of DACs, while the driving voltage dynamics is adjusted by fixed-gain amplification stage.

- **Power supply**: a part of the system is dedicated to supplying the platform and the FPGA. It has both to manage the powering of all the system components and to provide enough current to correctly drive the thermal actuators.

In the next section, the third version of the electronic system, called Helios 3, is presented

(Sec. 2.1). Helios 3 enhances the functionalities and corrects faults of the previous versions, coping in particular with the increasing number of photonic devices that need to be controlled. In order to make the system more flexible to different applications and measurements, a modular structure has been conceived and the different module architectures are introduced in the last section (Sec 2.2) of the chapter.

## 2.1. Helios 3 architecture

As already mentioned before, a modular structure has been designed in order to guarantee easy electrical and optical accessibility to the photonic chip. Indeed, placing the photonic chips directly onto the main electronic control board is unpractical. First, the coupling of light with optical fibers and the wire-bonding needed to provide electrical access to the chip are hard to implement if the size of the electronics increases. In addition, gluing the photonic chip directly on the main electronic board makes it hard to test different chips designed for different experiments. The proposed solution is the adoption of an interface board, which permits the optical fiber coupling and guarantees the connection between electronic system and photonic chips.

## 2.1.1. Host PCB

*Mantis*, as colloquially called, is the dedicated host board, employed to interface the electronic circuitry with the optical setup. The module hosts the photonic chip and an analog front-end which reads and pre-amplies the signals coming from the photodetectors. The analog front-end is positioned as close as possible to photonic chips in order to minimize the impact of stray capacitances and retrieve an accurate measurement of the incoming signals. Furthermore, the tiny dimensions of the board ease the coupling with the optical fibers that interacts with the optical circuitry.

The host PCB allows also to add a Peltier cell beneath the chip to manage the overall temperature of the system. In order to analyze temperature of the chips as precisely as possible, a commercial thermistor is put immediately next to it. The board is then mounted atop a metal holder, which serves as both a mechanical support and a heat sink. The other electronic components are housed on a separate and bigger motherboard that is linked to the host board through shielded connections.

Figure 2.1: Photograph of the interface board Mantis

## Photodiodes Front-end

Commercial TransImpedance Amplifiers (TIA) usually accomplish the pre-amplification of signals from photodiodes. As mentioned in the previous chapter, Germanium detectors feature an high sensitivity to the telecommunication wavelengths, hence an high current signal is produced. A resistive-feedback TIA is normally employed in order to translate the photodiode generated current, which it can be a DC value or modulated at few kHz, into a voltage.

## 2.1.2. Motherboard

In previous versions of the Helios system, all the electronic sections explained in the introduction have been implemented into the same board. An intrinsic limitation to the number of acquisition and actuation channels was posed due to the PCB area required by these different sections. Hence, the increasing complexity of the photonic chips, requiring an increase amount of acquired and driven signals, has brought to reinterpretation of the whole electronic system: a modular architecture has been adopted in order to fit a larger number of channels, with the possibility of reconfiguring the electronic control to address several applications.

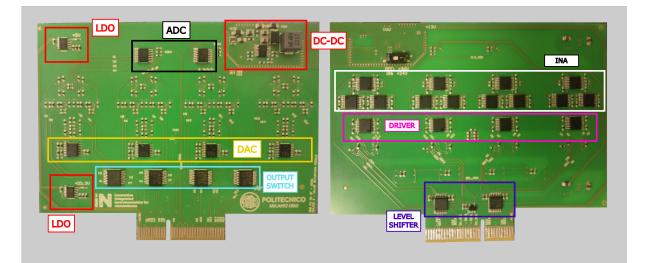

The new Helios 3 motherboard is represented in Fig. 2.2 and it accommodates:

• the FPGA, on the right, mounted on a commercial module; it programs the components of the system and is in charge of the Digital Signal Processing (DSP) required to control photonic devices.

- six PCI Express connectors for the plug-in expansion modules.

- the connectors which interface with the optical setup; in particular, on the left, the connectors towards the host board and, on the upper and lower sides, auxiliary SMAs.

- some specific acquisition circuitry for the read-out of bench-top photodiodes.

The specific read-out circuitry present onto the motherboard requires 24 out of 144 digital pins available on the FPGA to be handled. The remaining amount of digital pins is dedicated to the control of the external modules. The central part of the top layer is thus dedicated to the routing of the digital links from the FPGA to the expansion connectors: impedance-matching techniques have been adopted in the layout of these tracks, since high frequency clock signals need to be routed correctly without reflections and interference.

Figure 2.2: Photograph of the Helios 3 motherboard

The left side of the board features a set of six 64-position PCI Express connectors into

which the various functional modules of the system are plugged vertically. Each slots provides 24 analog pins, 16 digital pins, 4 power supplies and several ground pins to prevent crosstalk between the signal lines. Furthermore, analog lines and digital lines are well isolated since they are located on opposite layers. A total amount of 144 analog channels interface with the host board, while 96 digital pins exploit the full capability of FPGA.

The expansion modules have been designed in order to satisfy different requirements of the whole electronic system. So far, two pluggable module have already been realized:

- an acquisition module for the read-out of the signals coming from the host-board front-end circuitry. The incoming signals are further amplified and filtered on the module in order to match the voltage dynamics of the ADCs, which then digitize the sensor information.

- an actuation module able to drive SiP thermo-optic actuators.

To further expand the capability of the platform, Chapter 4 describes the design of an additional actuation module, able to drive SiN thermo-optic actuators and MEMS actuators which require different current and voltage dynamics with respect to the standard SiP heaters.

Power supply circuitry is not included onto the motherboard. Instead, an external module has been implemented in order to power up the whole electronic system. A deep analysis of this module is carried out in Chapter 3, describing the generation of the different supply voltages required by the motherboard and external modules circuitry. This reference voltages are  $\pm 6.5$  V and  $\pm 13$  V, which are delivered to the components on the motherboard and the pluggable modules via power planes present on two different motherboard layers. The power planes have two replicas, which feed the upper/lower parts of the motherboard and the three upper/lower external modules. A few Low DropOut (LDO) regulators are also used filter and provide stable power supplies to the dedicated circuitry implemented directly on the motherboard.

## 2.1.3. FPGA

A *Field Programmable Gate Array* (FPGA) is the digital core of the electronic system. This component has been chosen in order to efficiently control the large amount of mixedsignal devices on both the motherboard and the expansion modules and to provide reconfigurability to the whole system. Indeed, an FPGA provides the required versatility to handle different configurations/sets of pluggable modules employed to address various

applications, measurements and experiments.

The FPGA was not directly embedded into the motherboard in order to ease the layout phase and to facilitate the connection with a computer. The commercial platform Opal Kelly XEM7310 was selected. It presents the following features:

- Xilinx Artix-7 FPGA.

- Bootable serial flash memories (2 x 16MB) to store device firmware and configuration settings.

- USB 3.0 interface that permits the communication with a computer.

Figure 2.3: Opal Kelly XEM7310

## 2.2. Pluggable modules

As already mentioned in the previous section, specific expansion modules can be plugged into the motherboard to expand its functionalities and adapt the system to several photonic circuit configurations. In the following sections, the two modules already developed are introduced, while the power supply and another pluggable module are deeply explained in the last two chapters of this thesis.

## 2.2.1. Photodiodes acquisition module

The acquisition module has been designed for the read-out of Germanium photodiodes. The module receives from the host board 16 signals in parallel, that need to be further amplified, filtered and digitized. If the motherboard slots are occupied by only these

modules, Helios 3 can be used to acquire up to 96 incoming signals, even though without the possibility of driving any actuator.

As already mentioned before, a front-end transimpedance amplifier is placed on the interface board, to collect the current generated by the sensors, which is proportional to the light intensity, and convert it into voltage. This operation could be done directly on the acquisition module, however placing the front-end as close as possible to the sensors allows to maximise the measurement resolution by reducing the effect of parasitics caused by connections between photonic chip and electronics. The acquisition module thus has to process the voltage signal generated by the TIAs.

Three main considerations were taken into account during the design of this module:

- The module needs to have a programmable gain, in order to adapt the dynamics of the voltage signals coming from the host board to the dynamics of the analog-to-digital converters responsible for the digitization.

- The signals to be acquired are in a frequency range from DC to 50 kHz, therefore the ADC sampling frequency should be high enough and the antialias filter should not affect the readout.

- Despite 24 analog channels can be routed to the PCIe connector, the number of read-out chains is limited to 16 by the available digital pins, since they have to be employed for the selection of the programmable gain and for the communication between FPGA and ADCs.

The module is thus made of eight 2-channel PGAs and two 8-channel data-acquisition systems (DAS), including both the antialias filter and the ADC. The 3 bits of each PGAs are programmed with six 8-bit shift registers, connected in daisy chain configuration to reduce the number of digital signals required to operate them. The 16 ADCs instead communicate with the FPGA with two data lines, by time-multiplexing the communication among 8 channels each.

## 2.2.2. SiP actuation module

In order to drive the thermo-optic actuators integrated in Silicon Photonics technologies, a 24-channel actuation module was designed. The purpose of this module is to deliver the correct voltage bias to the heather, with the possibility of superimposing some dithering signals at frequencies of few tens of kHz. If the motherboard was set up with only this kind of module, up to 144 actuation actuators could be driven with Helios 3, with the possibility of acquiring only the signals from the bench-top instruments. In the design

Figure 2.4: Structure of the photodiodes acquisition module.

phase of the power supply module, this particular configuration has been considered as the most power consuming one and the power budget of all the system has been computed taking into account these large current requirements.

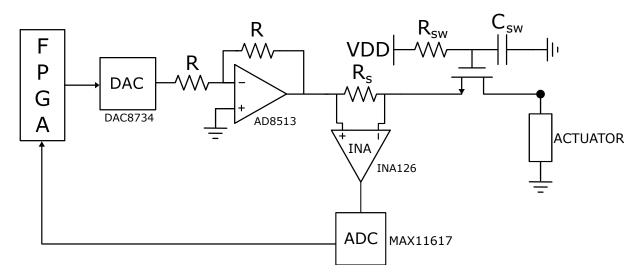

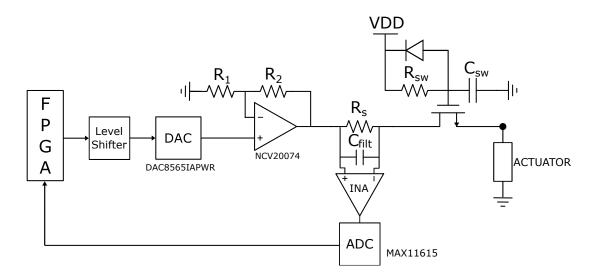

Figure 2.5: Schematic view of the actuation chain for SiP heaters

The module architecture is shown in fig. 2.5. Each chain features a 16-bit DAC able to generate voltage signals with a  $\pm 10V$  bipolar output range, when powered with a  $\pm 12V$  bipolar power supply. A current driver is used in buffer configuration in order to deliver to the heaters the correct amount of current (up to 30 mA), that cannot be provided directly by the DACs. 6 DACs and 6 drivers, both in a 4-channel configuration, are employed to drive 24 channels in total.

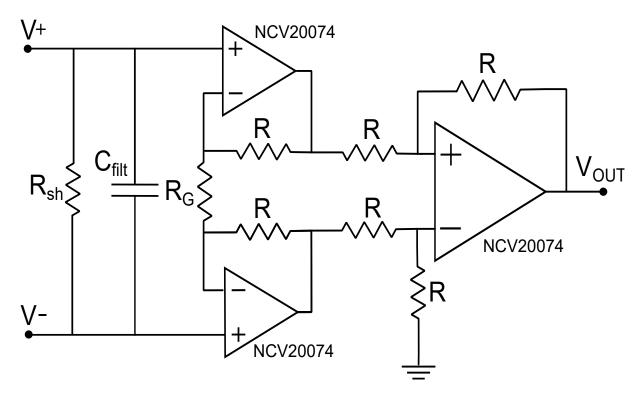

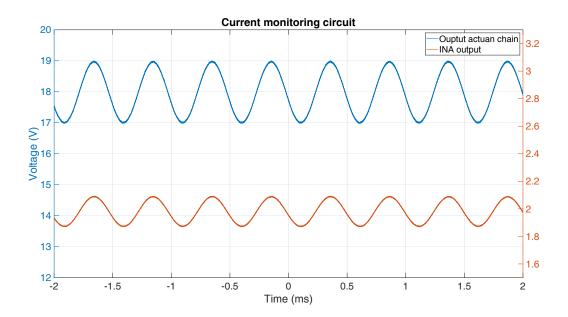

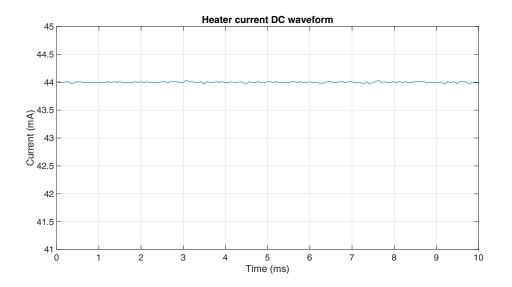

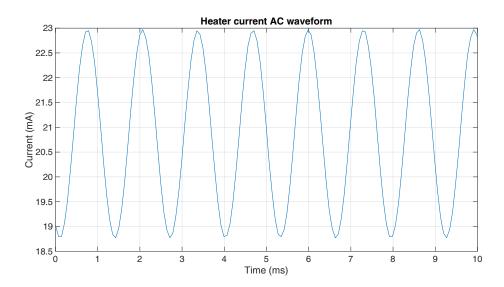

A monitoring circuit is placed before the output node in order to sense the current that is flowing towards the SiP heaters. To this aim, the voltage drop across a small shunt resistor in series to the actuators is amplified by an Instrumentation Amplifier (INA) stage and digitized with an ADC. The use of 2 12-channel ADCs allows to monitor the current of all the module channels in parallel.

Finally, a protection switch connects the circuit to the actuator only when the power supply of the module is stable. The transient is handled by an RC network that turns on the switch a few hundreds of ms after the switch-on of the whole instrument.

Taking a cue from the actuation chain of this module, a new version dedicated to generate actuation signals also for SiN heaters and MEMS actuators is proposed in Chapter 4.

# 3 Power supply module

## 3.1. Introduction

This is chapter is dedicated to the hardware description of the power supply module, designed to generate all the voltages required by the motherboard and the several pluggable modules. As already mentioned before, the amount of power needed by the complete instrument has risen in proportion to total number of components and channels. For this reason, the requested power cannot be handled by linear regulators (LDOs) because of their high inefficiency.

It becomes clear that the power supply system has to be managed by DC-DC regulators. The dedicated circuitry has been arranged on a specific module, not directly integrated on the Helios 3 motherboard. Since the switching noise of the regulators could affect the signals controlling the external modules and thus the quality of the control action, it was decided to connect the power supply board right over the Opal Kelly development platform, away from the most sensitive analog signals.

The power supply board is designed to accept a DC input voltage of 19V from an external power supply. This external voltage is generated by an AC adapter without the use of any top bench power supply, making the operation of Helios 3 simple. Finally, DC-DC regulators operate a down conversion in order to generate the voltages required by the system. LDOs are properly placed on the motherboard and modules in order to filter out the switching noise and provide a clean power supply. The simplified supply scheme is depicted in fig. 3.1.

In the following sections, the power requirements of the overall system are assessed and the adoption of switching regulators is explained (Sec 3.2), the power supply board is described (Sec 3.3), and finally the module is validated (Sec 3.4).

## 3 Power supply module

| Vin | Power module  | Motherboard                    |

|-----|---------------|--------------------------------|

| 19V | → LT3681 5V   | FPGA                           |

|     | 173681 6.5V   | ADP7104 • 2.5V                 |

|     | → LT3681 6.5V | ADP7104 • 3.3V<br>ADP7104 • 5V |

|     | LT3681 13V    | ADP7104 •12V                   |

|     | LTC7149-6.5V  | →ADP7182 -5V                   |

|     | LTC7149 -13V  | →ADP718212V                    |

Figure 3.1: Tree diagram of the distributed power supply adopted in Helios 3 platform, from the input voltage of 19V coming from an external power supply (e.g. laptop charger) to the motherboard power supply.

## 3.2. Design guidelines and power budget

As already stated in Chapter 2, the electronic platform Helios 3 has enhanced the capability of FPGA with the possibility of acquiring and actuating numerous channels. These increment of channels corresponds to an increase of requested power.

The voltage levels that must be created are unavoidably dependent on the different used components, which are unpredictable before the modules development. It was thus decided to generate four fixed voltages on the power supply board, then used by each module to locally create any other necessary level. In particular  $\pm 13$ V and  $\pm 6.5$ V were chosen, since the actual voltages required in the majority of applications are near to these levels. This allows for the operation of both power-hungry components as well as the efficient generation of smaller values, such as those required by digital interfaces or analog voltage references. In addition, the power module also independently generates  $\pm 5$ V, that has to be supplied to the Opal Kelly platform.

In order to properly size and design the supply board, the power required to operate the whole system was estimated, obviously considering the worst case scenario in order to guarantee the operation in all possible applications. Considering all the modules, the worst case arrangement is listed as follows:

• Actuation module: the actuation module presented in Chapter 2 is able to deliver up to 20mA to the *heaters* implemented in the photonic chip. Since the drivers

employed are working with  $\pm$  12V power supply and the number of channels present on the module is 24, if 6 actuation modules are plugged to the motherboard, an estimate of 3A current can be computed, down-scaled to 2A when referred to the 19V input.

- Opal Kelly platform: the powering voltage of the FPGA hosting platform is 5V, while the power consumption estimated for the device with a 80% utilization is 3W. Referred to the input, a correct esteem of 0.3A was assessed.

- Motherboard and acquisition module: neither the motherboard nor the acquisition module represents the power bottleneck of the overall system.

Considering the previous budget, it was decided to supply the power module with an AC/DC adapter able to deliver up to 5A current, that translates into a maximum available power of 90W.

| Component      | Supply voltage   | Current          | Number of<br>devices | Total power<br>dissipation |

|----------------|------------------|------------------|----------------------|----------------------------|

| DAC9734        | $\pm 12V$        | 12mA             | 6                    | 1.73W                      |

| DAC9734        | $+3.3\mathrm{V}$ | $25 \mathrm{uA}$ | 0                    | $500 \mathrm{uW}$          |

| AD8513         | $\pm 12V$        | 2mA              | 6                    | 300mW                      |

| INA2126        | $\pm 12V$        | $200\mu A$       | 12                   | 60mW                       |

| MAX11617       | $+3.3\mathrm{V}$ | $900\mu A$       | 2                    | 59.4mW                     |

| TMUX6212       | $\pm 12V$        | $35\mu A$        | 6                    | $84\mu W$                  |

| SN74HC125      | $+3.3\mathrm{V}$ | $160\mu A$       | 1                    | $528\mu W$                 |

| Heaters (Load) | $\pm 6V$         | 20mA             | 24                   | 2.88W                      |

Table 3.1: Summary of power dissipation of the actuation module

# 3.3. Power supply description

Taking into account all the previous considerations, the power supply board generates five voltages, starting from a  $V_{in} = 19V$  input which is properly filtered, as follows:

- **Positive voltages**: +5V dedicated to power the FPGA, +6.5V and +13V delivered to the motherboard or to the external modules. These three voltages are generated using three LT3681 Step-Down Switching Regulator, made by Linear Technology, that can deliver up to 2A current with almost 90% efficiency. They operate at 2MHz;

- Negative voltages: -6.5V and -13V negative power supply voltages. These two voltages are produced by two LTC7149 Synchronous Step-Down Regulator for In-

verting Outputs, designed by Linear Technology, able to deliver up to 4A current with 92% efficiency. They operate at 2MHz;

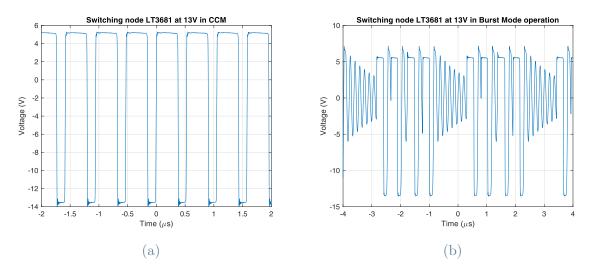

All the five ICs are set to operate at 2MHz: it was decided to center the switching frequency of the DC-DC converters around MHz region in order not to stay too close to the frequencies of the signals used to control the optical circuitry. Furthermore, high switching frequencies decrease the size of components like as inductors, transformers, resistors and capacitors, as well as the board and case space requirements. However, since the efficiency of these devices is degraded at too high switching frequencies, the value of 2MHz has been selected as a good compromise.

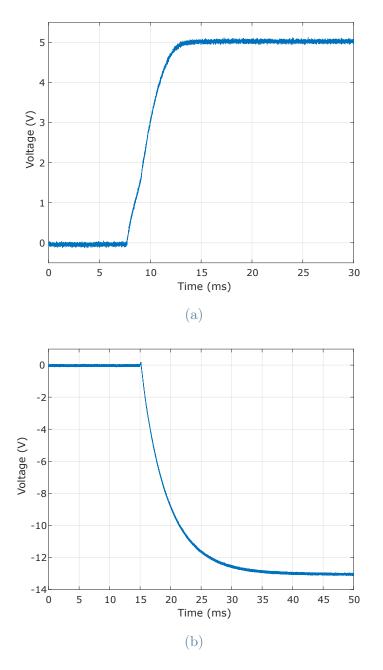

The two type of ICs (step-down and inverting converter) can work both in Continuous Current Mode (CCM) and in Burst Mode operation, in order to minimize their power dissipation in light load condition. Indeed, when the outputs do not require high amounts of current, the converters charge the output capacitor with single cycle bursts of current, remaining in sleep mode for almost all the switching period. The light load current is in fact delivered by the already charged output capacitance. To increase the module efficiency, the converters have been set to automatically switch from CCM to Burst Mode when light load is detected.

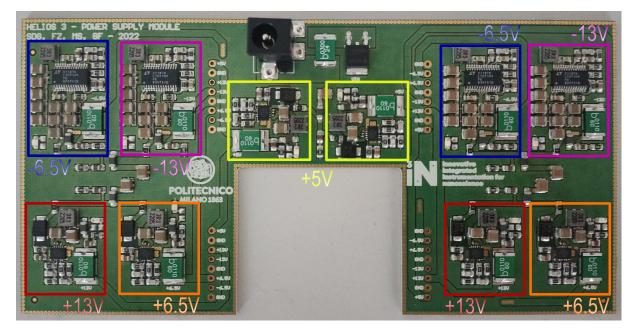

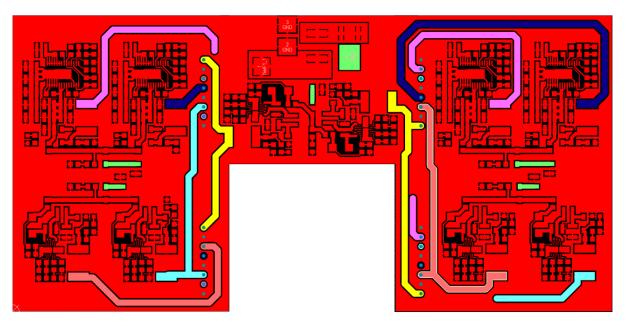

To take into account future developments of the systems and increase robustness and reliability of the module, a replica of the five voltages is generated by a second set of DC-DC converters, leading to the employment of ten devices on the power supply module.

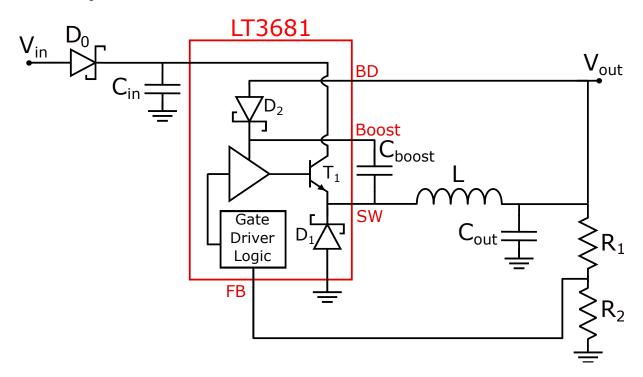

## **3.3.1.** Step-down converter

LT3681 Step-Down Switching Regulator is the DC-DC converter employed for the generation of the positive power supplies. This type of regulator is a selectable frequency (300kHz to 2.8MHz) monolithic buck switching regulator that accepts an input up to 34V and generates an output voltage from 1.265V to 20V. As depicted by fig. 3.2, a high efficiency 0.18  $\Omega$  NPN transitor ( $T_1$ ) and a power Schottky diode ( $D_1$ ) are integrated into this ICs to minimize the occupied area on the PCB board. A resistor divider between the output and the FB pin is used to program the output voltage, according to the relation:

$$R_1 = R_2 \cdot \left(\frac{V_{out}}{1.265V} - 1\right) \tag{3.1}$$

In particular, while  $R_1 = 590k \Omega$  has been selected for all the three ICs,  $R_2 = 63.4 k\Omega$ , 143  $k\Omega$  and 200  $k\Omega$  are placed to generate 5V, 6.5V and 13V respectively. The resistor divider voltage is measured by an internal error amplifier to define the output current:

when the error signal grows, more current is given to the output; when it lowers, less current is provided.

Figure 3.2: LT3681 Step-down converter

The IC is supplied by an embedded regulator, which is generally powered by the regulated output voltage. In order to drive the internal NPN switch, a *bootstrap* circuitry is used, as represented in fig. 3.2. An external capacitor  $C_{boost} = 0.47 \mu F$  is utilized to create a voltage greater than the input supply of the regulator, i.e. the generated output voltage, at the BOOST pin: in this way, the driver can fully turn on the built-in bipolar power switch.

As already mentioned, the switching frequency of all DC-DC converters was set to 2MHz. This value should be compliant with the maximum operating frequency of the IC, defined as:

$$f_{sw(MAX)} = \frac{V_D + V_{OUT}}{t_{ON(MIN)} \cdot (V_D + V_{IN} - V_{SW})}$$

(3.2)

where  $V_{OUT}$  is the output voltage,  $V_{IN}$  is the input voltage,  $V_D$  is the voltage drop across the internal Schottky diode  $D_1$  (~ 0.55 V),  $V_{SW}$  is internal transistor power drop (less than 0.5 V) and  $t_{ON(MIN)}$  is the minimum switch on time. A 2MHz switching frequency safely accommodates the highest  $V_{IN}/V_{OUT} = 19V/5V$ .

The sizing of the passive components was started by the selection of the power inductor: indeed, the ripple current is determined by the inductor value and switching frequency

for a particular input and output voltage. Considering a reasonable maximum output current  $I_{OUT(MAX)} = 1 A$  and setting the ripple current at least  $\Delta I_L = 0.6 \cdot I_{OUT(MAX)}$  for all three conditions, the main inductor parameters can be assessed:

$$I_{L(RMS)} > I_{OUT(MAX)} \tag{3.3}$$

$$I_{L(SAT)} > 1, 3 \cdot I_{OUT(MAX)} \tag{3.4}$$

$$L = \left(\frac{V_{OUT} + V_D}{f_{sw} \cdot \Delta I_L}\right) \left(1 - \frac{V_{OUT} + V_D}{V_{IN}}\right)$$

(3.5)

where  $I_{L(RMS)}$  is the inductor RMS current and  $I_{L(SAT)}$  is the inductor saturation current, with the other parameters previously introduced.

For all the three step-down circuits, the inductor selected is Bourns SRP4020FA-3R3M shielded power inductor with  $L = 3.3 \,\mu H$ ,  $I_{L(SAT)} = 2.7 \,A$ ,  $I_{L(RMS)} = 4.4 \,A$  and low series resistance  $DCR = 4.4 \,m\Omega$  in order to minimize conductive loss.

The selection of passive components continues with the input capacitor  $C_{in}$  and the output capacitor  $C_{out}$ . To correctly handle the ripple current and force it into a small loop, the input power supply was bypassed by a X5R ceramic capacitor of  $10 \,\mu F$ . The output ripple is filtered by the same capacitor used for the input bypass, since ceramic capacitors have very low equivalent series resistance (ESR). However, a correct esteem of the ripple is not possible since the output current is not constant and it depends on the different Helios 3 configurations.

Lastly, diode  $D_0$  is placed in series to the input power supply: the main purpose of this component is to protect against a shorted or reversed input.

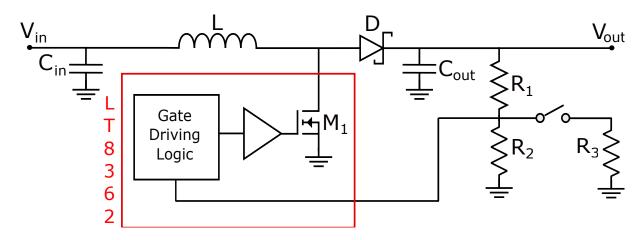

## 3.3.2. Step-down converter for Inverting Outputs

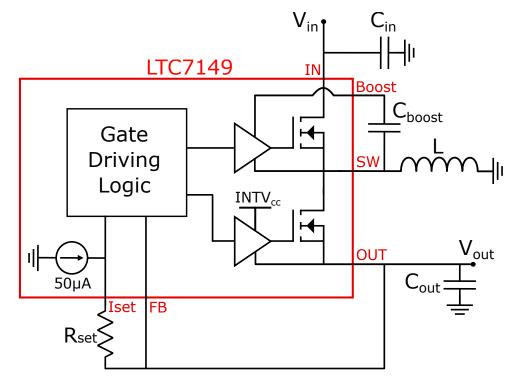

LTC7149 Synchronous monolithic regulator is the DC-DC converter employed for the generation of the negative power supplies. This inverting converter can work within a wide input range (3.4V to 60V), generate negative output voltages till -28V and deliver up to 4A. Also in this case, the switching frequency can be externally adjusted in the range from 300kHz to 3MHz, that contains the required 2MHz.

As represented in fig. 3.3, the monolithic regulator integrates both the high-side switch  $(110m \Omega \text{ NMOS})$  and the low-side switch  $(50m\Omega \text{ NMOS})$ . The setting of the output voltage is done by the selection of the external resistor  $R_{set}$ , connected between  $I_{SET}$  pin

and the output node, according to:

$$Vout = -50\mu A \cdot R_{set} \tag{3.6}$$

where  $50\mu A$  is the precise value of the internal current generator on the  $I_{SET}$  pin. Hence, to create -6.5V and -13V,  $R_{set} = 130 k\Omega$  and 261  $k\Omega$  are respectively employed.

Figure 3.3: LTC7149 Inverting converter

The internal high-side switch is turned on at the start of a clock pulse in normal operation, letting the inductor current ramp up to a certain maximum level. When the level is reached, the top power MOS is deactivated and the low-side MOS is activated until the next clock cycle. The current mode loop is handled by a gate driving controller that, by comparing the voltage values between  $I_{SET}$  and  $F_B$  pins, adjusts the driving of the switch and matches the current capability requested by the output. As seen with the positive step-down regulator, the presence of the *bootstrap* circuitry ( $C_{boost} = 0.1 \, \mu F$ ) permits the efficient driving of the high-side switch.

The design phase followed the same steps of the previous regulator, with only an increase of the output current requirements as allowed by the device. By choosing  $I_{OUT(MAX)} = 2A$ and by setting the inductor current ripple to 60% of decided maximum current, the same inductor of the previous DC-DC converter has been chosen, since it respects the following

conditions:

$$I_{L(SAT)} > I_{OUT(MAX)} \tag{3.7}$$

$$L = \left(\frac{V_{IN}}{f_{sw} \cdot \Delta I_{L(MAX)}}\right) \left(\frac{|V_{OUT}|}{V_{IN} + |V_{OUT}|}\right)$$

(3.8)

where the worst case is the one with  $V_{OUT} = -13 V$ , leading to an inductance value  $L = 3.3 \,\mu F$ . Lastly, the input capacitor  $C_{in}$  provides the filtering of the square wave current at the drain of high-side switch: several input capacitance were paralleled, reaching a value of  $22 \,\mu F$ , in order to correctly handle the maximum RMS current  $I_{RMS}$ . On the other hand,  $C_{out} = 50 \,\mu F$  was placed at the output node in order to filter the output ripple and provide good stability to the feedback loop.

## 3.3.3. EMI Input filtering and Output filtering

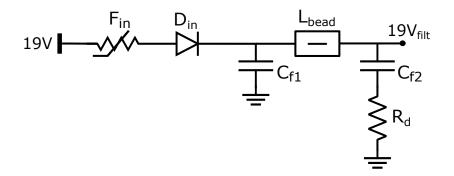

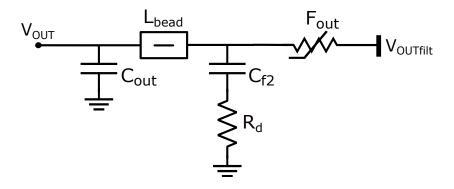

An input filter is required to decrease conducted emissions created by a DC/DC converter. As depicted in fig. 3.4, the primary function of the filter is to suppress noise and current surges from the external power supply that may affect the downstream circuits. The filter mitigates interference signals at the input switching frequency and its harmonics, preventing them from injecting noise in the system and interfering with any device [20]. A  $\pi$  network is generally employed: the capacitor  $C_{f1}$  provides an rough filtering of the residual AC components of the input power supply, while the following LC network provides of a low-pass action of second order.

Figure 3.4: Input stage with protection measures and EMI filtering

In the same way, as represented in fig. 3.5, the output of each DC-DC converters is filtered by the same LC network, with the purpose of reducing the output ripple. In the design of the power supply board, each IC presents these filters, with *ferrite beads* instead of a standard inductors in order to reduce the Q factor gain at the filter cutoff frequency, defined as:

Figure 3.5: Output stage with protection fuse and filtering

$$f_{cut} = \frac{1}{2\pi\sqrt{L_{bead}C_{f2}}}\tag{3.9}$$

A ferrite bead is a passive component that absorbs noise energy by turning it into heat. It can be modeled as an inductor in parallel to a resistor, that accounts for the device dissipation. The inductive behaviour is exploited to filter noise on a wide frequency range, while the resistive part of the impedance damps the device resonance without causing any DC voltage drop. Ferrite beads are thus well suited to implement LC filters, however they suffer from saturation due to high load current, that cause the value of inductance to reduce, thus shifting the cutoff toward higher frequencies [21].

The filter cutoff was chosen in order to suppress the 2MHz switching frequencies and its harmonics with an attenuation of at least 40db, hence the filter cutoff was centeread around the 100kHz. This frequency was chosen taking into account that Continuous Current Mode (CCM) is expected to be the normal operating mode of the DC/DC converters of the supply module. A filter able to perform an effective action also for Burst Mode Operations would have required very large inductors and capacitors, not compliant with the available module area. In order to meet the frequency requirements, a ferrite bead with an inductance  $L_{bead} = 280 nH$  and a capacitor  $C_{f2} = 10\mu F$  are chosen to build the second order low-pass filter. To increase the smoothing of the transfer function, a damping resistor  $R_d = 2\Omega$  is added in series to  $C_{f2}$ .

# 3.3.4. Protection measures

Some protection measures were also applied to the power module in order to safeguard its reliability and functionality even in case of malfunctions and unpredicted operating conditions. In particular, the following situations were considered:

• Input reverse polarity: to correctly handle the input power supply, a diode  $D_{in}$

is placed in series to the  $\pi$  filter with the purpose of protecting the circuit from reverse polarity. Indeed, if the input voltage has the wrong polarity, the diode turns off and shuts the module down, preventing any damage.

• Overcurrent protection: Positive resettable coefficient (PTC) fuses are placed in series to the input and to all the generated output voltages. These components behave as short circuits as long as a small current flows through them, thus not affecting the circuit behaviour. However, when the operating temperature rises due to a large current flow, their resistance increases dramatically, shutting down the downstream circuits. In order to select the correct fuse, the two important parameters to be set are the trip current  $I_{trip}$ , i.e. the minimum current required to activate the device transition, and the hold current  $I_{hold}$ , i.e. the maximum current that a PTC fuse can handle for extended periods of time without tripping.

The diode RURD620CCS9A (STMicroelectronics) has been chosen as input reverse polarity protection, since it is able to handle currents up to 5A with a negligible voltage drop and has a maximum reverse voltage of 200V, thus perfectly satisfying the requirements of the application. The chosen overcurrent protection fuses are instead 0ZCF0300BF2C (Bel Fuse, 5.2A trip current, 3A hold current) for the overall circuit input and 0ZCF0110AF2A (Bel Fuse, 2.2 A trip current, 1.1 A hold current) at each DC/DC output.

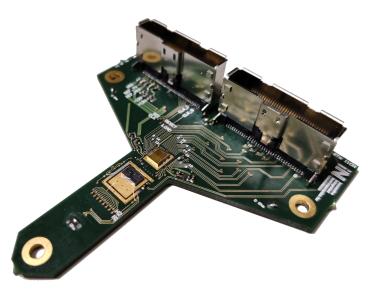

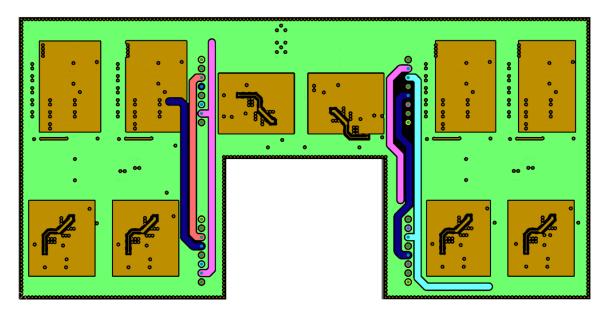

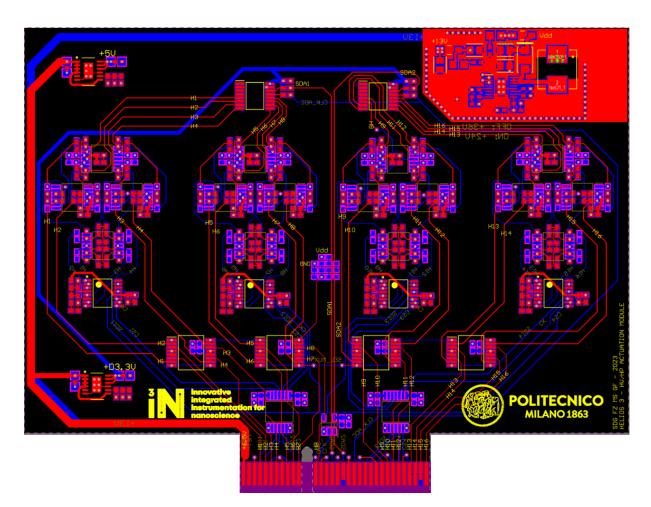

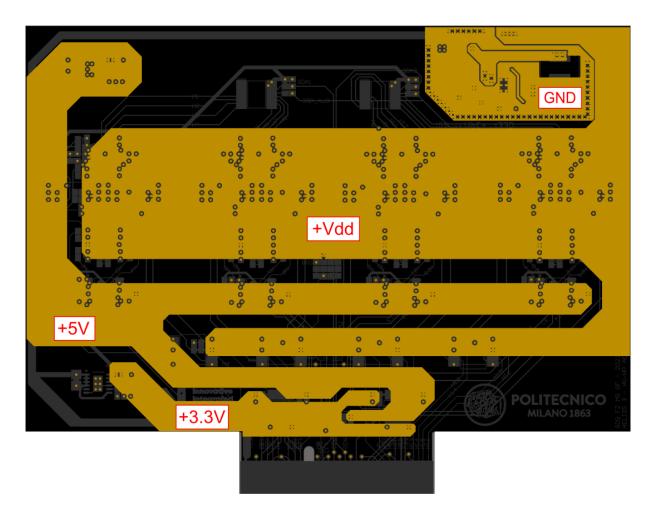

# 3.3.5. PCB layout

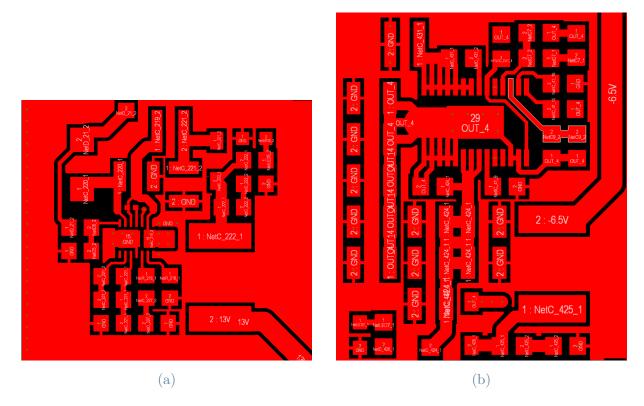

The shape of the power module was conceived similar to an horseshoe (as shown in fig. 3.6), in order to give room to FPGA for dissipating the heat generated during its operation. Indeed, as already mentioned in the introduction, the power board is connected to the motherboard through four vertical headers, right above the Opal Kelly platform. Only two headers are actually used to provide the supply voltages to the motherboard, that distributes them to all the components thanks to several power planes. The other two dummy connectors only ensure mechanical stability and balance when plugging the module. Since the power board can be detached from the motherboard, the disposition and connections of the headers guarantee a correct operation even if the module is inserted with a 180° rotation.

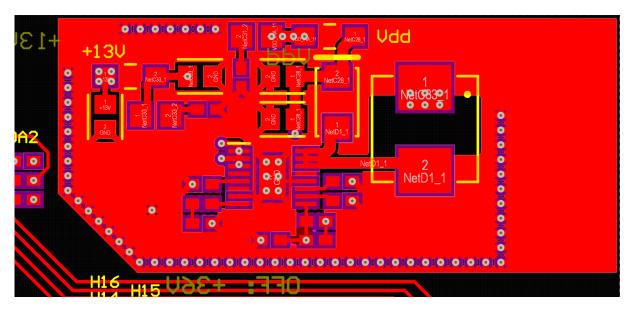

Fig. 3.7 shows the layout of all the DC/DC converters on the top layer, with a simple partitioning of the PCB area. Since the motherboard is much larger than the power module, the layout has been done with no particular requirements in terms of area occupation, allowing to place all the components on the top layer and design a board with only four layers. In this way, no converters have been disposed on the bottom part of the board,

in order to not radiate significant electromagnetic interferences towards the Opal Kelly platform. As already explained in the introduction, the converters are positioned almost symmetrically and connected to the headers on the same side.

Figure 3.6: Power supply board layout with 10 ICs employed

Figure 3.7: Top layer of the power supply board

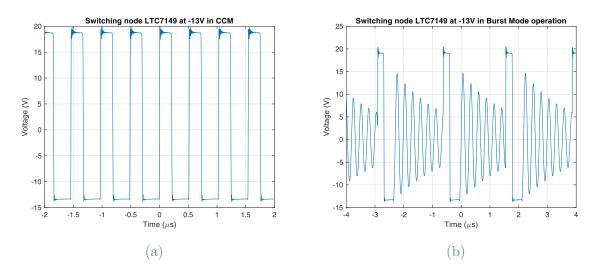

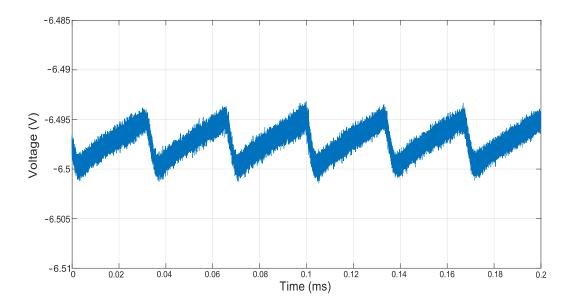

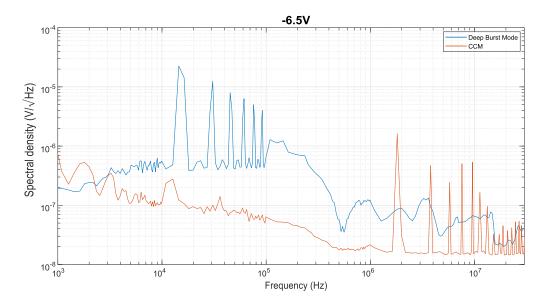

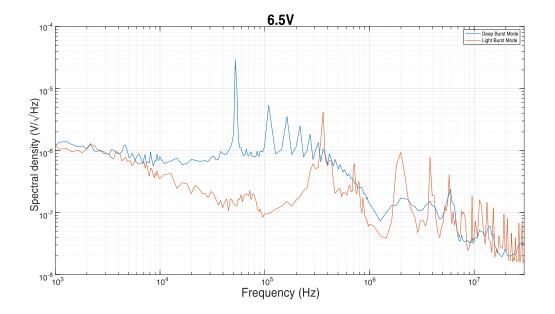

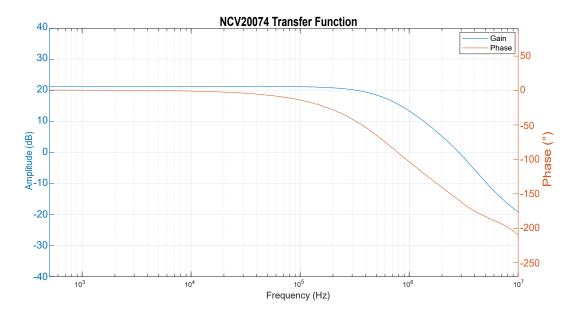

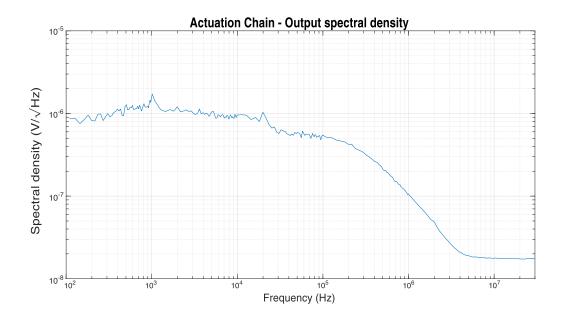

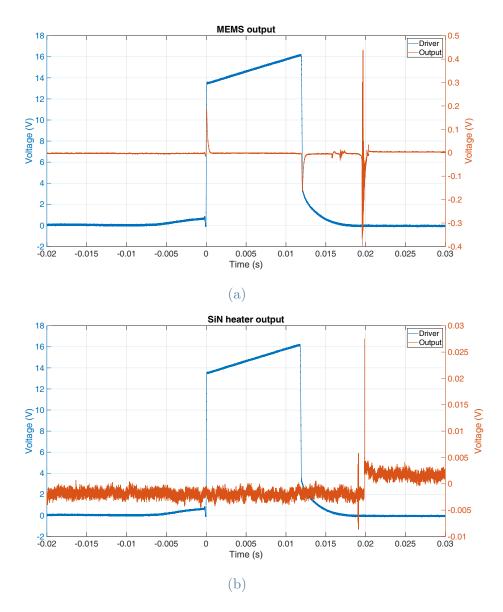

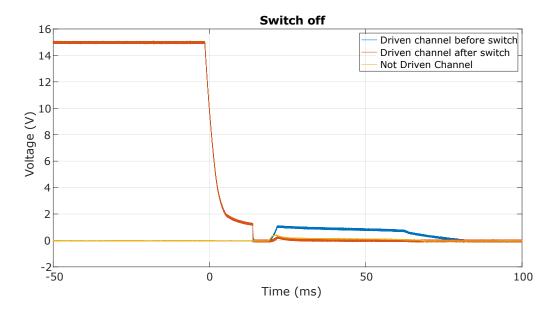

Figure 3.8: Step-down converter layout (a) and Inverting converter layout (b)