SCUOLA DI INGEGNERIA INDUSTRIALE E DELL'INFORMAZIONE

# Toward portable HPC applications with SYCL: a molecular docking case study

TESI DI LAUREA MAGISTRALE IN Computer Engineering - Ingegneria Informatica

Author: Nicolò Scipione

Student ID: 920281 Advisor: Prof. Gianluca Palermo Co-advisor: Emanuele Vitali PhD Academic Year: 2021-22

# Abstract

My thesis aims to verify and assess the portability across hardware vendors and performance achievable on GPGPUs computing using the new C++ framework SYCL. To do it, I ported a complete high-throughput molecular docking application from CUDA code to SYCL, converting every kernel of the application to it and being sure that the new code produces the same results as the original one. Moreover, SYCL code has to be as similar to the native one as possible. During the conversion, I make analyses of the possibility available and the limitation that a non-proprietary framework has against native code. The performances were tested on NVIDIA and AMD hardware, comparing results to the original CUDA ones. In addition to it, I analyze code differences from a performance perspective. The code is compiled with DPC++ and hipSYCL because both compilers work with the available GPUs, and it allows analyzing better the current situation of SYCL as a standard. The results of the studies show how it is possible to convert all the existing code from CUDA to SYCL and only in a few cases use some workaround to convey the current limitation of the standard. It also demonstrates that thanks to its rapid evolution SYCL is catching up quickly with proprietary code and it enables researchers to bring their applications to new hardware. The outcome obtained by SYCL code performance-wise is very encouraging for the future because, as I demonstrate, are already comparable with CUDA ones. Concluding that thanks to the current performance level reached SYCL, as a standard, is ready to be considered usable in a performance-oriented environment. Moreover, the great flexibility and portability of the code across vendors, without the necessity to learn a new language, make it a very intriguing framework for the supercomputers of the near future.

**Keywords:** SYCL, Heterogeneous Systems, GPGPUs, DPC++, HPC, CUDA, hipSYCL, molecular docking

# Abstract in lingua italiana

L'obiettivo della mia tesi è verificare e convalidare la portabilità e le performance che si possono ottenere in ambito GPGPU computing utilizzando SYCL, un nuovo standard in C++ per programmare Heterogeneous Processors. Per raggiungere il mio obbiettivo, sono partito da un'applicazione di docking molecolare, scritta in CUDA e sviluppata al Politecnico di Milano. Ho convertito tutto il codice in SYCL, assicurandomi che il nuovo codice producesse gli stessi risultati dell'originale e che fosse il più simile possibile a quest'ultimo. Durante il porting ho analizzato le diverse possibilità e limitazione che un framework non proprietario, SYCL, ha in confronto a del codice nativo per un hardware specifico come CUDA. Le performance sono state testate su GPU NVIDIA e AMD, comparando i risultati con quelli ottenuti da CUDA, in quanto è lo standard per l'applicazione. Inoltre ho analizzato le differenze nelle performance ottenute, andando a ricercare cosa nel codice potrebbe causarle. Il codice SYCL è compilato utilizzando entrambi i compilatori disponibili che permettono di eseguire il codice sull'hardware prescelto, ovvero DPC++e hipSYCL. In questo modo, ho la possibilità di capire meglio la situazione attuale e le possibilità di SYCL senza che sia vincolato dallo sviluppo di un singolo compilatore. I risultati dello studio mostrano come sia possibile convertire tutto il codice preesistente da CUDA a SYCL, in modo che solo in pochi casi sia necessario trovare altre strategie per ovviare le limitazioni correnti del nuovo standard. Anche che grazie alla sia rapida evoluzione SYCL sta recuperando velocemente la distanza dagli standard proprietari ed inoltre permette di eseguire il codice su nuovo hardware dove prima non era possibile. I risultati delle performance ottenuti con SYCL sono molto incoraggianti per il futuro, perchè, come ho dimostrato, sono già comparabili a quelli di CUDA. Concludo che grazie alle performance attuali raggiunte SYCL come standard, è pronto per essere considerato utilizzabile in ambienti dove la performance è fondamentale. Inoltre la grande flessibilità e portabilità del codice su hardware di diversi provider, lo rendono un framework molto interessante per i supercomputer del prossimo futuro.

**Parole chiave:** SYCL, Heterogenous Systems, GPGPU, DPC++, HPC, CUDA, hip-SYLC, docking molecolare

# Contents

| Abstract                    | i   |

|-----------------------------|-----|

| Abstract in lingua italiana | iii |

| Contents                    | v   |

# Introduction

| 1        | Stat                          | State Of The Art                                                                                                                                     |    |  |  |  |  |  |

|----------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

|          | 1.1                           | History of Heterogeneous System                                                                                                                      | 5  |  |  |  |  |  |

|          | The CUDA Programming Language | 6                                                                                                                                                    |    |  |  |  |  |  |

|          |                               | 1.2.1 History                                                                                                                                        | 6  |  |  |  |  |  |

|          |                               | 1.2.2 Functionality and Integration                                                                                                                  | 7  |  |  |  |  |  |

|          |                               | 1.2.3 Advantages and Limits                                                                                                                          | 9  |  |  |  |  |  |

|          | 1.3                           | openACC $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                                                                                             | 0  |  |  |  |  |  |

|          |                               | 1.3.1 Advantages and Limits                                                                                                                          | 0  |  |  |  |  |  |

|          | 1.4                           | OpenCL                                                                                                                                               | 2  |  |  |  |  |  |

|          |                               | 1.4.1 How it works $\ldots \ldots 1$ | 3  |  |  |  |  |  |

|          |                               | 1.4.2 Advantages and Limits                                                                                                                          | 4  |  |  |  |  |  |

|          | 1.5                           | SYCL                                                                                                                                                 | 5  |  |  |  |  |  |

|          |                               | 1.5.1 Advantages and Limits                                                                                                                          | 7  |  |  |  |  |  |

|          | 1.6                           | State of The Art Language Comparison                                                                                                                 | 8  |  |  |  |  |  |

|          |                               | 1.6.1 Programmability $\ldots \ldots 1$            | 8  |  |  |  |  |  |

|          |                               | 1.6.2 Portability $\ldots \ldots 2$                       | 27 |  |  |  |  |  |

|          |                               | 1.6.3 Performance                                                                                                                                    | 29 |  |  |  |  |  |

|          | 1.7                           | Ligen: the case study molecular docking application                                                                                                  | 88 |  |  |  |  |  |

| <b>2</b> | Con                           | Contribution 3                                                                                                                                       |    |  |  |  |  |  |

|          | 2.1                           | Design choices porting the code                                                                                                                      | 0  |  |  |  |  |  |

1

|                                       |     | 2.1.1                 | Choose a compiler                                                                | 40 |

|---------------------------------------|-----|-----------------------|----------------------------------------------------------------------------------|----|

|                                       |     | 2.1.2                 | How to perform the porting from CUDA                                             | 41 |

|                                       |     | 2.1.3                 | Unified Shared Memory vs Buffers and Accessors                                   | 42 |

|                                       |     | 2.1.4                 | Portability or extreme Performance oriented                                      | 43 |

|                                       | 2.2 | Kerne                 | l Porting                                                                        | 44 |

|                                       |     | 2.2.1                 | Initialize memory                                                                | 44 |

|                                       |     | 2.2.2                 | Transfering data with USM                                                        | 45 |

|                                       |     | 2.2.3                 | Simple and small kernels                                                         | 47 |

|                                       |     | 2.2.4                 | The Alignment Phase: a Compute Intensive kernel                                  | 49 |

|                                       |     | 2.2.5                 | Optimization and Final score. Divergent kernels                                  | 56 |

|                                       |     | 2.2.6                 | Non portable kernels and their work-around                                       | 60 |

|                                       | 2.3 | Overv                 | iew on portability                                                               | 63 |

|                                       |     | 2.3.1                 | Portability and code differences between $\mathrm{DPC}{++}$ and hip<br>SYCL $$ . | 63 |

|                                       |     | 2.3.2                 | Across Hardware Vendors                                                          | 65 |

| 3                                     | Exr | nt and Results        | 67                                                                               |    |

| 0                                     | 3.1 |                       | iment Setup                                                                      |    |

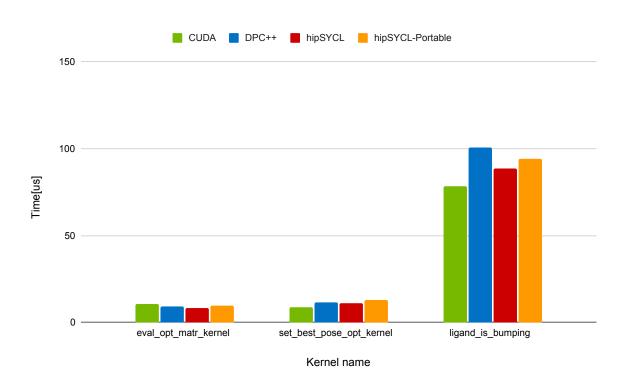

|                                       | 3.2 | kernels: SYCL vs CUDA |                                                                                  |    |

|                                       | 3.3 |                       |                                                                                  |    |

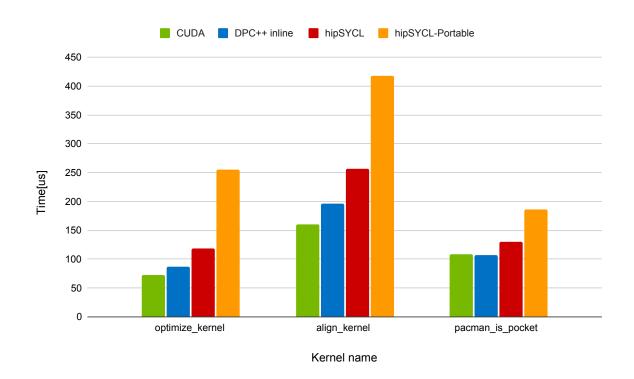

|                                       | 0.0 | 3.3.1                 | SYCL vs CUDA on NVIDIA GPUs                                                      |    |

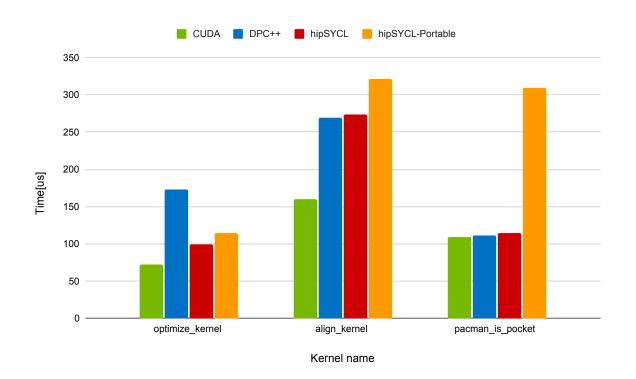

|                                       |     | 3.3.2                 | SYCL on AMD GPUs                                                                 |    |

|                                       |     | pility vs Performance |                                                                                  |    |

|                                       |     | 3.4.1                 | Portable SYCL on AMD GPUs                                                        |    |

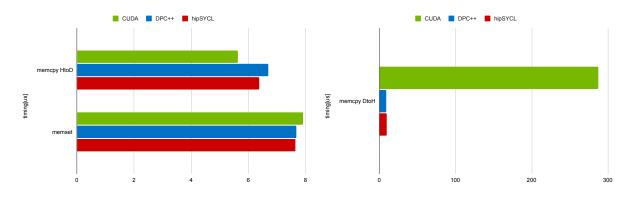

|                                       | 3.5 |                       | ry Bandwidth comparison                                                          |    |

|                                       |     |                       | · -                                                                              |    |

| 4 Conclusions and future developments |     |                       |                                                                                  | 87 |

|                                       | 4.1 | Obser                 | vations                                                                          | 87 |

|                                       |     | 4.1.1                 | Portability                                                                      | 87 |

|                                       |     | 4.1.2                 | Performance                                                                      | 88 |

|                                       | 4.2 | Future                | e Work                                                                           | 89 |

|                                       |     |                       |                                                                                  |    |

# Bibliography

| $\operatorname{List}$ | of | Figures |

|-----------------------|----|---------|

|-----------------------|----|---------|

### List of Tables

95

91

97

# Introduction

For almost four decades in computer science, there was the belief that about every two years the number of transistors in an Integrated Circuit(IC) would have doubled. This idea is known as Moore's law. This idea led computer engineering development, but in the last twenty years it has been proved to be wrong. Better, the technology reached its maturity, and the physical improvement is not that high anymore. The physical reasons for this outcome are multiple. First of all, the size of the transistors is still shrinking but not that fast, and every year it's closer to the physical limit for the current needed for its function. It is impossible to power all the area and the transistors available in the IC, which leads to having some parts of the chip turned on and parts turned off. The necessity of keeping some part of the chip turned off is driven by the power consumption and by thermal design, which implies that the temperature reached by the IC must be below a given threshold. This phenomenon is called *dark silicon*.

In these same decades, as a society, our needs for more powerful PCs and CPUs have been kept increasing, so engineers came up with different ideas to cope with it. The first idea to mitigate the *dark silicon* effect is to add multiple cores of the same design in the same chip. The different cores communicate through shared memory, but are capable of handling different loads, distributing temperature and powers, so it's not needed to have all the silicon powered all the time altogether. Giving birth to physical parallelism.

The other way is provided by Heterogeneous Systems that are combinations of different type of components in the same system. The different parts can be on the same die, as in the case of *System On a Chip*(SoC) or can communicate through different buses on a bigger system. Examples of the most famous Heterogeneous Systems are the SoC present in every phone and recently computers, thanks to ARM, and the most common combo of CPU and GPU in personal computers.

The implementation of Heterogeneous Systems does not only solve the problem of increasing the performance for simple tasks but allows scientists to use very powerful systems to perform the computation for their research, as it was done in the origin of the computer era. The necessity to perform more difficult research and forecast always require more powerful technology.

#### Introduction

Nowadays, the ability to build and exploit big and complex computing systems has a fundamental role for every country to push their research, these kinds of machines are called *supercomputers*. To have a better understanding of the current situation about it, from 1993, a project called **TOP500** ranks them in order of computational power. Reading these ranking it's important to notice that now all the most powerful systems in the world implement some form of Heterogeneous System, from the ARM architecture of the first one to other seven systems, out of the first ten, that use a lot of GPUs.[1]

The development of the architectures and hardware for *supercomputers* leads the development of hardware, and there's a huge competition between companies to provide the best possible solution. Shortly, there will be many different supercomputers that utilize GPUs from different vendors, besides all those that are equipped with NVIDIA hardware that can be viewed in the top500 list. By the end of the year, there will be new supercomputers like LUMI[2], a machine located in Finland that use AMD MI250X, and in the U.S.A. there will be *Frontier*, that also has AMD MI250X GPUs and *El Capitan* that will have the next AMD GPUs [3]. Moreover, also *Intel* will start to produce its discrete graphics card, and there is a supercomputer ready to exploit their hardware named *Aurora*[4] still based in the U.S. So in the future, there will be a wide diversification in hardware that lead to new languages and newer necessities.

The importance and the influence of GPUs come from their architecture differences from CPUs. It is way easier than the former and allows to put more cores on a small dice. This possibility does not come for free, in fact, many complex operations are way slower on them than on CPU, but the presence of more cores enables different algorithms and massive parallelization speed up some classes of computation, especially in those fields of research that need to analyze or to use a large amount of data. The implementation of these algorithms, the discovery of new fields where it is possible to apply this knowledge and hardware, are grouped in the field of *High-Performance Computing*(HPC). Examples of areas of science that benefits a lot from supercomputer and GPUs computations are many. The most known nowadays is for sure Machine Learning and Artificial intelligence, where the ability to process a lot of data in a very short time is essential. Other examples are more niche and close to the research environment. For example, Computational Fluid Dynamics a branch of fluid mechanics that merges numerical calculus and data structure to analyze how fluid flows, where the need to process complex problems exploits very well the ability to split the problem into many parts and analyze them. The last example is the field of drug discovery and molecular simulation because supercomputers and parallelization enable the possibility to test many different combinations of chemical elements.

#### Introduction

The arrival of new competitors in the GPU field brings another problem to the industry, in fact, now every company that produces hardware releases also the toolkit/language to exploit it at its best. The standard for all the supercomputers is *CUDA toolkit* by NVIDIA because it was the only hardware manufacturer. Anyway, today there are different alternative programming languages to exploit all the GPUs available. OpenCL wanted to be the portable version of CUDA, following almost the same philosophy, and other standards chose to create directive-based languages such as OpenACC. The newest and most promising language emerging is SYCL, which is a C++ framework that allows bringing modern standard C++ code to hardware accelerators independently from the hardware on which it will run on, enabling the same application to exploit all the future available GPUs.

In this work, I want to analyze the current state of SYCL in all possible forms and verify its usability in the HPC environment. I want to test the portability of the code on GPUs from different vendors, taking into account not only this aspect but also the performance that this new standard can achieve compared to **NVIDIA** proprietary language. In particular, I ported a *molecular docking* application, [5] developed here at Polytechnic of Milan, from CUDA to SYCL. I analyzed the code differences in the conversion and the current state of portability to different hardware. The performance analysis compares what distinct SYCL compilers are capable of doing on the same codebase, but also they behave on different hardware and if it matches up with CUDA.

The structure of the work is composed as follows: chapter 1 is an explanation of the current state of programming language for Heterogeneous Systems, in particular in the HPC environment, so focused on GPUs implementation. The pros and cons of every model, and the state of the art of performance analysis on GPUs, which is a core aspect. Chapter 2 shows how I tackled the porting of the CUDA algorithm to **SYCL**, all the design choices, the problems encountered, and the various performance obtained with different compilers on **NVIDIA** and **AMD**. The last chapter is an overview of future work, improvement, and tests possible on the new implementation presented and within the **SYCL** framework in general.

This chapter introduces the current state of heterogeneous programming in the HPC field with particular care of the languages available for this task. The chapter can be split into three parts, the first one introduces languages and standards that are the most commonly used or the most promising ones in the field: *CUDA*, *OpenACC*, *OpenCL* and *SYCL*. For each of them, it tells a few of their stories, how they work, advantages and limits of their approach and implementation. The second part makes a more in-depth comparison of the languages, giving a detailed analysis of three aspects that are the core differences and focal point of decision in favor of one of these languages. The three categories on which I focus are: programmability, how easy it is to write code in it, portability, on which hardware can the code be run and performance, which standard/language give the best performance or if the performance obtained are comparable in different tasks. To conclude it provides a brief overview of the molecular docking application used as case study, to better understand the structure and reference of the description of the work.

# 1.1. History of Heterogeneous System

The idea of exploiting Heterogeneous Systems to solve some intensive computing problems was born with the realization that the *Moore's Law* was slowly showing its limits. So researchers started looking for a method to bring particular computation-intensive tasks on different types of processors. Before these researches, GPUs were used only to process the graphics of the software and video games, functionality from which they take the name *Graphics Processor Unit*. At the beginning of this evolution, in the late '90s, there was no ad-hoc language to separate code compilation and execution on different types of processors, so writing this kind of code was extremely hard, but researchers noticed immediately the performance advantages of it. The first great turn in this environment is the invention of the **Brook** language by *Ian Buck* during his Ph.D. at Stanford. *Brook* is the first programming model that provides a simpler way to exploit GPUs shaders to make other types of computations[6].

After completing his Ph.D., Buck went to **NVIDIA** to continue his research and He

created **CUDA** the *NVIDIA*'s **proprietary** language, that now is the standard for HPC computation on their GPUs. It has been having the best performances and the top computers in the top500 rank have NVIDIA's GPUs. The limits in portability do not have any effect yet and the limits of the language are overcame by developers.

This hegemony will probably change soon, since also **AMD** and **Intel**, the two NVIDIA's competitors on consumer electronics, are entering the HPC domain with their machines, powered by their CPUs and, more important, with their own GPUs. AMD already has three big contracts: *LUMI* [2], a European machine, *Frontier* and *El Capitain* in the USA [3]. Intel has already one contract to provide GPUs for *Aurora* [4] still in the USA. For these reasons, there is the need for new languages and paradigms that allows close or equal performance to CUDA, but with other characteristics.

# **1.2.** The CUDA Programming Language

#### 1.2.1. History

CUDA was born in 2007 starting from the idea that **Brook** introduces. With it, NVIDIA wanted to expand the possibility of programming GPUs not only for graphics and shaders but to general computing. They wanted to enable all developers to program GPUs as they did on CPUs, without caring about all the extra work of synchronizations and memory issues that were present before. NVIDIA developers' idea and goal were to have control of hardware in a specific and precise way, that **Brook**, since it was just an academic project, could not achieve [7].

To ease the spread of GPUs programming, they had many options. They could invent a new parallel language or add some extension to **OpenGL**. Since it is a company they followed customers' desire, and customers do not want to learn a new programming language or an API. Since C is the fastest language on CPUs, they decided to make the same on GPUs. Right now, CUDA supports many C++ features to make the language far more usable in a modern environment. It supports also FORTRAN, which is another language used in HPC, especially by mathematicians.

Now **CUDA** is not only a language but a complete toolkit provided by **NVIDIA**, that everyone can download from their site [8].

#### **1.2.2.** Functionality and Integration

CUDA has been thought from the ground up to be the perfect integration of software on NVIDIA's hardware. This special integration is a fundamental advantage, allowing to create software constructs ad-hoc for the hardware providing better programmability and performance. The design of CUDA and GPUs architectures lead all the other language to be as they are today. A deeper look into how it works is useful to understand further explanations.

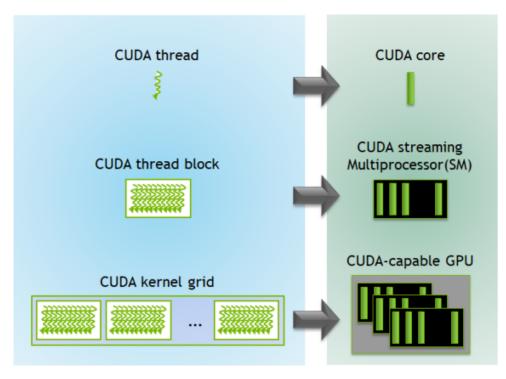

#### CUDA and GPUs parallelism

The integration of the two is so tight that CUDA is an abstraction of the actual GPUs. It divide the code into host, which is the CPU, and device, which is any GPUs available selected. There is no better words to express how CUDA behaves other than those on NVIDIA's blog[9]: Code running on GPUs [...] is executed K times in parallel by K different CUDA threads, as opposed to only one time like regular C/C++ functions. [...] A group of threads is called a CUDA block. CUDA blocks are grouped into a grid. A kernel is executed as a grid of blocks of threads. Each CUDA block is executed by one streaming multiprocessor (SM) and cannot be migrated to other SMs in GPU (except during preemption, debugging, or CUDA dynamic parallelism). One SM can run several concurrent CUDA blocks depending on the resources needed by CUDA blocks. Each kernel is executed on one device and CUDA supports running multiple kernels on a device at one time. Following figure 1.1 is taken from the same article and shows the correlation between hardware and software.

Figure 1.1: Kernel execution on GPU

# Hardware

NVIDIA started from the necessity that emerged by trying to port general computation on GPUs and introduced many technologies [10]. Before 2006, GPUs have only a texture memory and each operation could read and write only one address in memory. There was no memory available to share data among works and the structure of the computation was different. NVIDIA introduced the idea of **Thread Programming**, where the developer can explicitly call a function to run on GPU and allocate several threads to make the work, so now it can run millions of instructions at the same time on different cores. With these new features, came the support to other data types and more difficult hardware implementation that allowed complex constructs such as loop and branching and the relative optimization at compile time. One of the first new technology introduced was the possibility to have a *global memory* where the program can write without being restricted to a given type or position in memory and that all the process of writing is handled with pointers. Related to memory, NVIDIA introduced also the *shared memory*, which is a particular type of memory that all the threads in the same block can use to store computation results and shared data among them.

The above hardware introductions are just a few examples of how much work NVIDIA put in the research in this field and all of them represent the first idea developed. Nowadays,

NVIDIA's GPUs architecture is far more complex and every hardware news was followed by some software command to exploit it for general computation, a couple of examples are cooperative groups and thread warp.

#### Software

In the original plan of NVIDIA, *CUDA* should have been the natural evolution of C for GPUs. It shares many constructs of the C language to speed up the adoption of the language as a standard for GPU computing. To a C programmer, it is very easy to understand since it shares the same memory model used for C on CPUs. For example, allocations are done through malloc, copies between different memory addresses follow the same logic as C, using pointers to memory, and it does not provide a garbage collector. The difference between the two is that with CUDA, the developer must also take care of the memory on the accelerator and not only on the host CPU.

To keep the language simple and as close as possible to the thread model of C, the developer assigns which part of the code should run on the accelerator by declaring it in a particular function that will be called using triangular brackets after the function call. In those brackets, the developer writes code's properties, such as how to parallelize it and the local memory necessary. These functions above are called kernels, developers have in their hands how to design the code and use it. Compilers only take care of compiling the code for the correct machine, using some particular *declaration specifier* added by NVIDIA. It possible to select and address the very particular thread or block or grid that is currently executing using some constructs, e.g, threadId.x, threadId.y or blockId.x and different aspect of the execution with similar keywords. Nowadays, CUDA is much more similar to C++ than to C, even if the way memory is handled is still the same.

#### **1.2.3.** Advantages and Limits

This proprietary approach to heterogeneous programming has some advantages and some limits. The most important feature is that everything is designed, tuned, and optimized by the same company. This choice can guarantee a great integration between hardware and software, which leads to better performance and control over what users can implement and how everything interacts. Another good point is that there is only one source of the *CUDA Toolkit* and everything it provides will work as intended and eventual bugs are fixed by the single-source provider.

Limits of a closed source technology and language are many and are related more to the

philosophy of development and what it implies. It cannot guarantee code portability to another platform, which can be a limit in the future if NVIDIA GPUs will not be top-level hardware. Integrating new functionalities in the language is harder since not anyone has access to the implementation. Another barrier is more related to the language itself. The idea of developing a *C language for GPUs* brings with it all the flaws that the original C language has, e.g. memory control and all the low-level feature that make it a little bit outdated nowadays.

# 1.3. openACC

OpenACC[11] is a standard designed for port code execution on different kinds of accelerators, in particular, it is used for GPGPU computation. It was designed by Cray, CAPS, NVIDIA, and PGI et al. as a solution for one of the shortcomings of CUDA. They wanted to lower the difficulty of coding for those systems to expand the possibility of porting code on heterogeneous systems. It was released as an open standard capable of being implemented by different companies, foundations, and universities. Besides NVIDIA, now different organizations are working on making OpenACC works e.g., Cray, a subsidiary of Hewlett Packard Enterprise, and the Oak Ridge National Laboratory.

The structure and the implementation of **OpenACC** are completely different from CUDA ones. It uses *compiler directives* to let the programmer point out which part of the code should run on the *accelerators*, but the let the compiler decides how to do it. OpenACC is similar to OpenMP but targetting GPUs because it came out OpenMP was only targeting multi-threading on CPUs so there was the need for something similar for GPUs.

#### **1.3.1.** Advantages and Limits

OpenACC has some technical and practical characteristics that make it unique and differentiate it from CUDA, as always there are advantages and limits.

#### Advantages

- Single source code The compiler directives are added where needed, but the total structure of the code is not changed. There is no need to write a new file as in CUDA. This aspect simplifies a lot the introduction of parallelism.

- High level programming language. The fact that it's a compiler directives language, abstracts a lot of technicalities and lets programmers focus only on the parallelization and data locality. It supports C++ as well as FORTRAN, which is a

very well-known language by researchers in HPC, lowering the barrier to accelerate specific applications.

- Low learning curve. Since it's a compiler directive approach, it doesn't require the same knowledge as CUDA does. It lowers the barrier from *common* programmers to access accelerators because it takes away many design features since it is high level. For example, differently from CUDA, using OpenACC programmers don't take care about memory allocation and where resources must be before being used by the accelerators or the CPU, compilers take care of it. It's possible to suggest where data should be to help the compiler, and it's possible to avoid useless memory copying, but it's not necessary at all. This particular aspect lowers the knowledge barrier needed to exploit GPGPUs computing.

- **Rapid Development**. All the characteristics above lead to a fast development even by an inexperienced developer.

- Interoperability. The code written using OpenACC can be used along with CUDA code, OpenMP, and MPI.

- **Portability**. This is the main advantage over CUDA. If exists a compiler for any given hardware the OpenACC program can run on it. This enables the possibility to exploit also GPUs from other manufacturers than NVIDIA, such as AMD. This is possible since OpenACC is an open standard, not owned by a company that decides directions and implementations, everyone can contribute to it.

#### Limits

The characteristics expressed above try to overcome some **CUDA** shortcomings, but it is not perfect. Every aspect described in the previous section introduces some problems that stop OpenACC from being the standard of heterogeneous high-performance computing instead of CUDA.

The portability factor, which is the most appealing, suffers from fragmentation. There are many compilers under development that support it on paper, but each of them has different features implemented. This brings difficulty to developers that need to adapt the code to the compiler. Moreover, since many companies and institutions are working on it, some of them may fail, be acquired, or stop working on it. Any of these events cause problems to the implementation and reliability of porting some code to OpenACC. The only available and well-implemented compiler, that supports OpenACC, is provided by NVIDIA, so it is useful only on their GPUs. The situation highlights another problem,

OpenACC was born with the idea of being used on many different platforms, but this is not true yet since NVIDIA acquired PGI that had the leading OpenACC compiler [12]. The best hope to spread OpenACC is given by GCC, that it's implementing it, but it is coming slowly added to the stack. Right now GCC supports OpenACC, but the user must recompile it with all the necessary flags, and it uses LLVM to enable the code generation on AMD GPUs. It will take some time before seeing it available to everyone.

The ease of use for which it is designed contributes make it usable by anyone with little explanation, but the same feature that make it also less customizable and less flexible and less performance oriented. This is not a problem for simple application or to show the power of GPGPUs computing, but in order to exploit all the computer power from extremely powerful and expensive machines is not enough. In high performance environment where a lot of specific work is required and where many expert researchers are available CUDA is still preferred but in other cases OpenACC is very useful, e.g., on SUMMIT [13], an important US supercomputer, most of the code is written in OpenACC. Moreover the idea of using **pragmas** as language feature implementation seems easy at first, if the instruction to give is simple, but more complex directives that could lead to speed up in the code are not so trivial and learn them is completely different than learn a language specification of API as in CUDA or other languages.

# 1.4. OpenCL

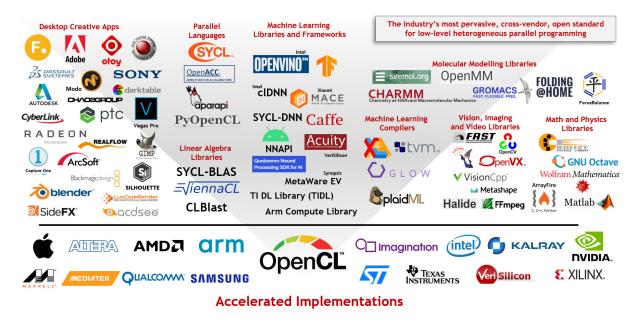

**OpenCL** [14] is an open standard for cross-platform parallel programming of different types of accelerators, from supercomputers to FPGA. It is managed by the *Khronos Group* that decides and publishes the standard of development for the technology and it guarantees that companies' implementations of OpenCL are conformed to the standard, giving its certification.

The *OpenCL* standard emerged, when the technologies that may need a particular code implementation started to rise. At first the development was led by *Apple* in 2008 and later the *Khronos group* takes the role of coordinate the forces of many companies that use and publish their support. As the image 1.2 shows, OpenCL is used by many companies in different fields and today is a valid alternative to CUDA in GPGPU programming, even if it presents a very different approach and more important it is not the effort of a single company that controls hardware and software.

OpenCL is not bounded to a single hardware, so how it exploits parallelism is different from *CUDA* and it does not influence the hardware evolution, but the language and the feature that it offers are similar to the NVIDIA's technology and based on common request

Figure 1.2: OpenCL users and major contributors

of the companies involved in the Khronos Group directive group.

#### 1.4.1. How it works

It is based on C language [15], in particular on C99, that is the latest standard for the C language, but it's also a very low level language, where developers need to take care of every details by them self, and it misses higher level abstraction that other languages provides, for this reason since *OpenCL 2.0* it allows to write code in C++. In order to understand which part of the code runs on the host CPU and which on GPUs, developers have to write the code for the accelerators in particular functions, named kernels, that will be compiled and send to it. This methodology is shared with CUDA and allows a fine grained division of the workload that it is entirely managed by programmers. To accomplish it, OpenCL offers two technical API, the first one is a *platform API layer* that runs on the host CPU and it is used first to enable a program to discover what parallel processors or compute devices are available in a system, select which one to use and adapt the code for the accelerator. The second API is the *Runtime API* that enables the compilation of the kernel for the correct accelerators and handle also the communication between host and accelerator, generally provided by the company that build the hardware on which will run the OpenCL code.

A characteristic point of OpenCL is the possibility of providing the binary with two different compilations method: *online* or *offline* compilation. The latter is the most common one and newest. It allows to compile all the code in to binary format and distribute it, but since the framework has portability in mind, in order to be portable to different machines, without recompile it, in this case it has to have compiled all the architecture that developers want to support. In reality, in order to provide portability and performance, the GPU code is not compiled to binary, but is left in a intermediate representation called **SPIR-V**, which is lately set up for the appropriate accelerator. The former allows the code to be entirely portable, because it lets the kernels written in high-level code and compile them at runtime, when necessary, on the target machines, using the Runtime API. This method leaves more room for portability, without using any particular trick, but affects performance and the kernels' code is left inside the binary.

#### **1.4.2.** Advantages and Limits

The decision of the standard leads to design choices that have various impacts, some are advantages and some are limits.

The advantage that stands out for OpenCL is **portability**. The core idea of OpenCL is to be extremely portable and to guarantee good performance on a large amount of different hardware. This goal is hard to achieve, but luckily many companies took part in the standard. So effectively OpenCL can give important speed up in the computation on different kind of devices, which make it a good option for many companies when they have to ship software.

The limitations of the standard and the approach, especially in the HPC environment, are much easier to spot. The first limit is related to having multiple standards available simultaneously, standards are always available as long as someone uses them. This is not a problem per se because the more choices the better, but different standards implement different features, and if companies don't support the same version the code that can run on some devices may not work on others. For example, for years in the GPGPUs environment, NVIDIA decided to freeze its support of OpenCL on *OpenCL 1.2*, if you want to use it on NVIDIA's GPUs, the code must be compliant with the runtime version they provide. This decision stopped the evolution of it even if AMD's GPU support *OpenCL 2.0+*, because the code may lose some specification and would not be portable anymore, losing in this way the best feature of the language. Recently NVIDIA announced the support for OpenCL 3.0, which brings them in front of AMD as OpenCL support.

A feature that turned out to be a limit is the choice to use C99 as standard for the kernel language. This idea was good at the beginning because it lets developers use a language that they already know but, since the times changed, it doesn't allow the evolution of the standard to a higher-level language, like C++, which gives more flexibility to the code. C++ has been implemented since the standard 2.2, but it is not the standard for everything yet, due to fragmentation problems.

The last limitation that has been addressed lately, but still not completely solved, is the online/offline compilation. Providing online compilation is better for portability but bad for performance and for critical applications, where you cannot distribute the code inside the binary. The offline compilation addresses it partially with the creation of SPIR-V but it is not fully compatible with everything, e.g. it is not compatible with NVIDIA's GPUs, and besides that, it exists two versions of it that are not compatible with each other.

The idea of OpenCL was very promising, a group that managed the standard, where many companies cooperate, is the future, but poorly designed choices and adoption stopped it from achieving great results on HPC while in embedded system is less a concern.

## 1.5. SYCL

The newest standard that is entering the scene is managed, sponsored, and spread by the *Khronos Group* as OpenCL. It was born as its substitute but takes the heredity of OpenCL for the concept as heterogeneous language capable of running everywhere and having the same performance as native developed languages.

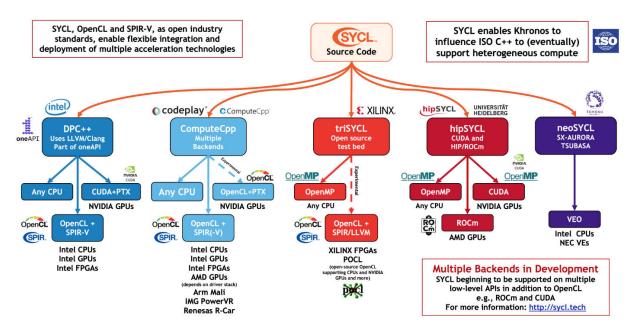

**SYCL** is a standard and is capable of producing code for every type of heterogeneous system, from the FPGA to GPGPUs computing, using the same syntax and the same compiler. As the new proposed standard is supported by different companies but, since it is only a standard, different companies developed their own compiler, while others decide to join forces and develop one compiler. Generally speaking, all compilers are based on LLVM Clang, so as host they support every feature that LLVM supports.

The current standard developed is the second iteration of it and it's called SYCL2020, that comes after SYCL 1.2. The main difference between the two and the greatest revolution is that the latter takes entirely the heredity of OpenCL and all the accelerators programming is based on it, so it needs OpenCL runtimes installed on the machine, while the newest one is entirely based on the code compiled, that is handled differently upon which is the target architecture and upon the implementation of the compiler. Since **SYCL** is just a standard it's difficult to explain how it works, due to the fact that each compiler and company decides how to implement it, the current situation (late 2021) is well represented by figure 1.3, of all those compilers in the image, only three are useful and related to the GPGPUs programming environment: DPC++, developed by Intel as open source project, hipSYCL, developed by the University of Hamburg, and ComputeCpp,

Figure 1.3: SYCL compilers available implementations

#### developed by Codeplay.

Referred to figure 1.3 there are some changes, *Codeplay* joined the force with *Intel*, trying to port SYCL performance on NVIDIA's GPU to the same level of CUDA, moreover DPC++ started to support AMD's GPUs using their **HIP** stack and exploiting SPIR-V as Intermidiate Representation. All those efforts are made in DPC++ by **Intel**, because it is the base language for their HPC platform based on their hardware and because they aim to merge their sycl compiler in the clang standard compiler.

Giving a unique description of how these compilers work is not possible, but the general approach and idea implemented by *SYCL* are the same. It wants to reduce the barriers, from a programming language perspective, of the effort needed to write code for heterogeneous platforms and increase the portability of the code, the same two areas for which *OpenCL* was born. The main difference from OpenCL is the total independence of SYCL from companies. It does not need any extra code provided by them but it can utilize the toolkit/compiler they already supply.

The actual implementation and differentiation of the code for the accelerators are handled and highlighted by the kernel as in *CUDA* and *OpenCL*. It can be done in two different simple ways: writing directly a lambda function or writing a class functor then implementing the function. The accelerators are selected at runtime, using any of those available on the machine. Compilation and execution are independent, and the framework will operate in the best way possible on the given hardware. In any case, which GPU is connected to the machine must be known at compile-time to create the correct assembly but it is not

necessary to know it when the code is written.

The code produced by a **SYCL** compiler is indistinguishable from code written and compiled by companies' products, thus proprietary performance analysis tools can be used without any effort. It is a great advantage because it gives developers a variety of tools to check the code, and it is not dependent on the standard, which would make the process of adoption slower.

#### 1.5.1. Advantages and Limits

As for OpenCL, the decisions taken by the standard committee have advantages and downsides. The general idea of improving OpenCL producing SYCL reduced a lot of the errors made in that standard, giving an edge to SYCL. First of all, the choice of C++ as the default language helps a lot the adoption, because it's one of the most used languages and it is a common point with **CUDA**, so developers do not need to learn a new language or paradigm of programming. Also, C++ developers from other fields can use it freely because it follows the C++17 standards.

In many of its implementation, SYCL uses different compilers to achieve its goals. The CPU part is based on clang, while the accelerators' part is implementation-dependent. So far, all the compilers developed exploit proprietary compilers for the NVIDIA hardware, while DPC++ and hipSYCL have distinct philosophies for other hardware. This combination is used to obtain a high level of performance and tool integration with the preexistence toolkit in any case. The possibility of utilizing proprietary toolkits lets developers profile the code. *Profiling* is the activity of looking at a very low level what the code is doing and how it performs in specific parts of the computation. It is crucial when trying to extract every performance possible. In this way, developers do not need to learn new tools but can use the ones they already know, reducing the learning curve and increasing the adoption.

One of the limits of *SYCL* emerged even in its early stages, is fragmentation. This idea of one standard implemented in various ways leads companies to create their product for their hardware. The risk is to have a world of *SYCL-like languages* that are similar to each other but not completely compatible. For this reason, the idea of *Intel* to upstream their implementation to LLVM should encourage other companies to collaborate to it. A limit that comes from the standard is that, as it is right now, some functionality may be in the standard but may not be implemented in the chosen compiler or for the chosen hardware. It limits choices for the developer, forcing the adoption of a more mature environment which is useless if the desired outcome is portability. Having one hardware mature and not the other would lean towards NVIDIA and consequently use CUDA as a toolkit/programming language.

# 1.6. State of The Art Language Comparison

This section gives a deeper look into the differences and peculiarities of the standards and language mentioned in Section 1.1. Some of the following comparisons were already done in the *Advantages and Limits* section 1.5.1 of each one of them, but now I dug further in three characteristics: *programmability, portability, and performance*

#### 1.6.1. Programmability

*Programmability* may have different meanings in different fields, in this specific case, we mean the characteristics of the language that make it easier for a developer to write efficient code, enter the HPC world, and exploit the power of the hardware. Many of the languages presented in the previous sections are similar in the idea but different in the implementation. To make it easier to understand, each of the following sections presents one language with a simple vector addition as an example. That is illustrated with comments on the language involved. The section finishes an overall comparison.

#### CUDA

The CUDA code must be split by developers deciding what runs on GPUs and CPUs. Kernels for the accelerator are highlighted by the special attribute global before the function definition. They are launched by giving it some (from two to four) parameters that tune the execution and resource allocation. To allocate or initiate variables and to call functions, CUDA implements the same strategy and structures of C/C++ but to differentiate it uses the prefix cuda to all its specific libraries. For example, the three vectors are initialized on the GPU with cudaMalloc as it does with a common malloc. cudaMemcpy is used to copy data from the host to GPU. As promised, CUDA looks very similar to C/C++ code to an expert developer. Moreover, the code is very flexible and lets developers implement whatever they want and exploit hardware in any way possible.

```

1 // CUDA kernel. Each thread takes care of one element of c

2 __global__ void vecAdd(double *a, double *b, double *c, int n) {

3 // Get our global thread ID

4 int id = blockIdx.x*blockDim.x+threadIdx.x;

5 // Make sure we do not go out of bounds

6 if (id < n)

7 c[id] = a[id] + b[id];</pre>

```

```

8 }

9

10 int main( int argc, char* argv[] ) {

// Size of vectors

11

int n = 100000;

// Host input vectors

13

double *h_a;

14

double *h_b;

15

//Host output vector

16

17

double *h_c;

// Device input vectors

18

double *d_a;

19

double *d_b;

20

//Device output vector

21

double *d_c;

22

// Size, in bytes, of each vector

23

size_t bytes = n*sizeof(double);

24

// Allocate memory for each vector on host

25

h_a = (double*)malloc(bytes);

26

h_b = (double*)malloc(bytes);

27

h_c = (double*)malloc(bytes);

28

// Allocate memory for each vector on GPU

29

cudaMalloc(&d_a, bytes);

30

cudaMalloc(&d_b, bytes);

31

cudaMalloc(&d_c, bytes);

32

int i;

33

// Initialize vectors on host

34

for( i = 0; i < n; i++ ) {</pre>

35

h_a[i] = sin(i) * sin(i);

36

h_b[i] = cos(i) * cos(i);

37

}

38

// Copy host vectors to device

39

cudaMemcpy( d_a, h_a, bytes, cudaMemcpyHostToDevice);

40

cudaMemcpy( d_b, h_b, bytes, cudaMemcpyHostToDevice);

41

int blockSize, gridSize;

42

// Number of threads in each thread block

43

blockSize = 1024;

44

// Number of thread blocks in grid

45

gridSize = (int)ceil((float)n/blockSize);

46

// Execute the kernel

47

vecAdd<<<gridSize, blockSize>>>(d_a, d_b, d_c, n);

48

// Copy array back to host

49

cudaMemcpy( h_c, d_c, bytes, cudaMemcpyDeviceToHost );

50

```

```

// Sum up vector c and print result divided by n, this should equal

51

1 within error

double sum = 0;

52

for(i=0; i<n; i++)</pre>

53

sum += h_c[i];

54

printf("final result: %f\n", sum/n);

// Release device memory

56

cudaFree(d_a);

57

cudaFree(d_b);

58

cudaFree(d_c);

59

// Release host memory

60

free(h_a);

61

free(h_b);

62

free(h_c);

63

return 0;

64

65 }

```

Listing 1.1: example of vector add in CUDA

The idea of programmability is different from other areas of computer science, but the usage of C/C++ common function call and the ability to easy handling memory make CUDA a good programming language for HPC. Since posting all the code may be redundant, I removed from Listing 1.1 include statements that are useless in the example.

## **OpenACC**

OpenACC has a completely different approach to the problem. It is straightforward C++ code (in listing 1.2 is C) with the addition of compiler instruction that will be automatically identified and implemented. Those instructions are called with the **#pragma** syntax before the code that developers want to run on the accelerator. The rest of the code doesn't change in any way from C/C++.

```

int main( int argc, char* argv[] ) {

// Size of vectors

2

int n = 10000;

3

// Input vectors

4

double *restrict a;

5

double *restrict b;

6

7

// Output vector

double *restrict c;

8

// Size, in bytes, of each vector

9

size_t bytes = n*sizeof(double);

10

// Allocate memory for each vector

11

a = (double*)malloc(bytes);

12

```

20

```

b = (double*)malloc(bytes);

13

c = (double*)malloc(bytes);

14

// Initialize content of input vectors, vector a[i] = sin(i)^2

15

vector b[i] = cos(i)^2

int i;

for(i=0; i<n; i++) {</pre>

17

a[i] = sin(i) * sin(i);

18

b[i] = cos(i) * cos(i);

19

}

20

// sum component wise and save result into vector c

21

#pragma acc kernels copyin(a[0:n],b[0:n]), copyout(c[0:n])

22

for(i=0; i<n; i++) {</pre>

23

c[i] = a[i] + b[i];

24

}

25

// Sum up vector c and print result divided by n, this should equal

26

1 within error

double sum = 0.0;

27

for(i=0; i<n; i++) {</pre>

28

sum += c[i];

29

}

30

sum = sum/n;

31

printf("final result: %f\n", sum);

32

// Release memory

33

free(a);

34

free(b);

35

free(c);

36

return 0;

37

38 }

```

Listing 1.2: example of vector add in OpenACC

This approach seems magnificent but even this little snippet of code shows two major drawbacks. Firstly, developers need a special compiler to obtain the expected result. Utilizing different compilers may lead to different results. The second point is that the code written is not flexible to developers' needs because there is no way to express parallelism with finer control than what common C/C++ can offer. So adapting algorithms and invocations based on the hardware differences is not possible. A noticeable improvement and benefit of OpenACC are that areas of the code can be ported with almost no effort by any C/C++ programmers, without further studies or adaptation for simpler sections. Although, there may need a different approach than pragma syntax in those cases where the code to parallelize is too complicated.

## **OpenCL**

OpenCL has a third approach to the matter, as it can be noticed by the following code 1.3, it is more verbose than others. This characteristic is due to following the C99 guidelines and the flexibility necessary to target different architectures, not only GPUs. Another big difference is in the first lines of the example. The kernel code is not written as a function, but it is written as a long string. The kernel will not be called but read as a file and then enqueued. The choice of putting kernel code as a string in the same file as the main function is arbitrary, it can be written in a separate file as OpenCL code and then read from the function. The code still present common traits to figure 1.1 and figure 1.2 related to the initialization and management of the host part, in common to the C/C++ heredity.

```

1 // OpenCL kernel. Each work item takes care of one element of c

2 const char *kernelSource =

"\n" \

3 "#pragma OPENCL EXTENSION cl_khr_fp64 : enable

n'' \

\n" \

"__kernel void vecAdd( __global double *a,

\n" \

5

н

__global double *b,

n

\n" \

6

__global double *c,

7 "

\n" \

const unsigned int n)

8 "{

\n" \

n,

//Get our global thread ID

\n" \

9

int id = get_global_id(0);

\n" \

н

10

11

н

\n" \

//Make sure we do not go out of bounds

\n" \

n

12

\n" \

н

if (id < n)

13

н

c[id] = a[id] + b[id];

\n" \

14

\n" \

" }

15

"\n" ;

16

int main( int argc, char* argv[] ){

17

// Length of vectors

18

unsigned int n = 100000;

19

// Host input vectors

20

double *h_a;

21

double *h_b;

22

// Host output vector

23

double *h_c;

24

// Device input buffers

25

cl_mem d_a;

26

cl_mem d_b;

27

28

// Device output buffer

cl_mem d_c;

29

30

```

```

cl_platform_id cpPlatform;

// OpenCL platform

31

cl_device_id device_id;

// device ID

32

cl_context context;

// context

33

cl_command_queue queue;

// command queue

34

cl_program program;

// program

35

cl_kernel kernel;

// kernel

36

37

// Size, in bytes, of each vector

38

size_t bytes = n*sizeof(double);

39

// Allocate memory for each vector on host

40

h_a = (double*)malloc(bytes);

41

h_b = (double*)malloc(bytes);

42

h_c = (double*)malloc(bytes);

43

// Initialize vectors on host

44

int i;

45

for( i = 0; i < n; i++ ) {</pre>

46

h_a[i] = sinf(i)*sinf(i);

47

h_b[i] = cosf(i) * cosf(i);

48

}

49

size_t globalSize, localSize;

50

cl_int err;

51

// Number of work items in each local work group

localSize = 64;

53

// Number of total work items - localSize must be devisor

globalSize = ceil(n/(float)localSize)*localSize;

// Bind to platform

56

err = clGetPlatformIDs(1, &cpPlatform, NULL);

57

// Get ID for the device

58

err = clGetDeviceIDs(cpPlatform, CL_DEVICE_TYPE_GPU, 1, &device_id,

59

NULL);

// Create a context

60

context = clCreateContext(0, 1, &device_id, NULL, NULL, &err);

61

// Create a command queue

62

queue = clCreateCommandQueue(context, device_id, 0, &err);

63

// Create the compute program from the source buffer

64

program = clCreateProgramWithSource(context, 1,

65

(const char **) & kernelSource, NULL, &err);

66

// Build the program executable

67

clBuildProgram(program, 0, NULL, NULL, NULL, NULL);

68

// Create the compute kernel in the program we wish to run

69

kernel = clCreateKernel(program, "vecAdd", &err);

70

// Create the input and output arrays in device memory for our

71

calculation

d_a = clCreateBuffer(context, CL_MEM_READ_ONLY, bytes, NULL, NULL);

72

```

```

d_b = clCreateBuffer(context, CL_MEM_READ_ONLY, bytes, NULL, NULL);

73

d_c = clCreateBuffer(context, CL_MEM_WRITE_ONLY, bytes, NULL, NULL);

74

// Write our data set into the input array in device memory

75

err = clEnqueueWriteBuffer(queue, d_a, CL_TRUE, 0,

bytes, h_a, O, NULL, NULL);

77

err |= clEnqueueWriteBuffer(queue, d_b, CL_TRUE, 0,

78

bytes, h_b, 0, NULL, NULL);

// Set the arguments to our compute kernel

80

= clSetKernelArg(kernel, 0, sizeof(cl_mem), &d_a);

err

81

err |= clSetKernelArg(kernel, 1, sizeof(cl_mem), &d_b);

82

err |= clSetKernelArg(kernel, 2, sizeof(cl_mem), &d_c);

83

err |= clSetKernelArg(kernel, 3, sizeof(unsigned int), &n);

84

// Execute the kernel over the entire range of the data set

85

err = clEnqueueNDRangeKernel(queue, kernel, 1, NULL, &globalSize, &

86

localSize,

O, NULL,

87

NULL);

// Wait for the command queue to get serviced before reading back

88

results

clFinish(queue);

89

// Read the results from the device

90

clEnqueueReadBuffer(queue, d_c, CL_TRUE, 0,

91

bytes, h_c, 0, NULL, NULL );

92

//Sum up vector c and print result divided by n, this should equal 1

93

within error

double sum = 0;

94

for(i=0; i<n; i++)</pre>

95

sum += h_c[i];

96

printf("final result: %f\n", sum/n);

97

// release OpenCL resources

98

clReleaseMemObject(d_a);

99

clReleaseMemObject(d_b);

100

clReleaseMemObject(d_c);

101

clReleaseProgram(program);

clReleaseKernel(kernel);

clReleaseCommandQueue(queue);

104

clReleaseContext(context);

105

//release host memory

106

free(h_a);

107

free(h_b);

108

free(h_c);

109

return 0;

110

111 }

```

Listing 1.3: example of vector add in OpenCL

All the functions specific to OpenCL are prefixed by cl, but differently from CUDA, there are many functions that are completely different from C and unknown to C/C++ developers that have never written code using OpenCL. Moreover, the verbosity is noticeable in the complete example, which has about 60 lines of code more than CUDA and it is the simplest possible with no particular implementation or algorithm. A reason for verbosity is also that in OpenCL programmers need to take care of the creation of the context in which the code will run, the device, all the possible errors, and kernel argument. The learning curve is much steeper than CUDA or OpenACC.

#### SYCL

SYCL has the same approach CUDA had 15 years ago with C, it tries to have a structure of the code as close as possible to modern C++. The idea of the *Khronos Group* is to make it as easy as possible for C++ developers to write code following the SYCL standard. Right now, SYCL2020 follows the C++17 standard, and for any C++ developer learning it is effortless.

The following code is concise and the part related to the GPU code is pure C++. It uses buffers to handle the vector's lifespan on GPU and accessors to access it. The kernel code starts at line 31 and finishes at line 36. It is very concise, easy to write, and flexible. There's no memory handling by programmers, and it reduces complexity. All the memory handling in listing 1.4 is related to the code written in C, which could be replaced with a modern container in pure modern C++ style, but I want to keep it consistent within all the examples.

```

int main(int argc, char* argv[]) {

int n = 100000;

2

// initiliaze host vectors

3

double* h_a;

4

double* h_b;

5

double* h_c;

6

size_t bytes = n*sizeof(double);

7

h_a = (double*)malloc(bytes);

8

h_b = (double*)malloc(bytes);

9

h_c = (double*)malloc(bytes);

10

for(int i = 0; i < n; ++i) {</pre>

h_a[i] = sin(i) * sin(i);

12

h_b[i] = cos(i) * cos(i);

13

}

14

{ //open scope for buffers

```

```

//initialize buffers from host memory

16

cl::sycl::buffer<double, 1> buff_a(h_a, n);

17

cl::sycl::buffer<double, 1> buff_b(h_b, n);

18

cl::sycl::buffer<double, 1> buff_c(h_c, n);

19

//set up range for parallel code on GPU

20

cl::sycl::nd_range<1> thread_range{static_cast<int>(n*1024),1024};

21

//select available GPU to run code on

22

cl::sycl::queue q(cl::sycl::gpu_selector{});

23

//submit code that will run on GPU and set up memory access

24

q.submit([&] (cl::sycl::handler& h){

//set up accessor for GPU access

26

auto acc_a = buff_a.get_access(h);

27

auto acc_b = buff_b.get_access(h);

28

auto acc_c = buff_c.get_access(h, cl::sycl::write_only,cl::sycl::

29

no_init);

//kernel code

30

h.parallel_for(thread_range ,[=](cl::sycl::nd_item<1> it){

31

int i = it.get_local_id(0)+it.get_group().get_id(0)*it.

32

get_local_range(0);

if(i < n)

acc_c[i] = acc_a[i] + acc_b[i];

34

});

35

}).wait();

36

}// close the buffer

37

//free host memory

38

free(h_a);

39

free(h_b);

40

free(h_c);

41

return 0;

42

43 }

```

Listing 1.4: example of vector add in SYCL

The way listing 1.4 is written is not the only way possible in SYCL. The kernel can be in a different file or within a class. The buffer/accessor memory handling can be substituted with the use of usm(Unified Shared Memory) writing code even more similar to CUDA, even though it forces developers to renounce to some modern C++ features because it consists in managing memory using pointers as it is in CUDA. Moreover, the way the accelerator is selected in listing 1.4 targets only GPUs, but it is possible to target also FPGA and CPUs, with the same code. Given its characteristics, nowadays SYCL is probably the easiest way C++ programmers can access heterogeneous computer programming exploiting all the flexibility, customization of the code, and computing power available by using GPUs.

#### Final Comparison on Programmability

Overall all the solutions proposed have pros and cons and their particularities. It is evident that OpenACC is the most concise one for small and intuitive code to be parallelized, CUDA and SYCL follow the same idea of how to divide the code between platforms and how to write flexible and reusable code. SYCL is closer to standard C++ and offers higher abstraction to the programmer that may simplify and speed up the learning curve. For what concern OpenCL code(listing 1.3), it is easy to say that it seems way more verbose and less intuitive than the others. It comes from old paradigms and requires a lot of effort and attention from the programmer to be correct.

#### 1.6.2. Portability

The second fundamental characteristic is **Portability**. With this term, I mean the capabilities/possibility of a language to target different hardware and processors. This feature is going to be a decisive characteristic since, in recent years, there has been a huge investment in high-level GPUs and accelerators by the industry. So starting from now, having the possibility to write the code ones(or with a unique language) and run it on whatever hardware will be a key feature.

The time in which a language was designed and which problems were targeted has a great effect on the current portability.

CUDA was the first language designed, furthermore, it is created and shaped by **NVIDIA** for their GPUs. It shows how they see the future of GPGPUs computing and what they can make hardware-wise, so there is no space for portability, it runs only on NVIDIA's GPUs or chip.

The first version of *OpenACC* still comes from **NVIDIA**, but with a different idea in mind. They wanted to have an easier gateway for heterogeneous programming for developers and open this standard also for other manufacturers such as AMD. But the evolution of the support for the standard is slow both for NVIDIA and AMD. Currently exist many different compilers that support it on NVIDIA GPUs, and the ROCm compiler by AMD should support it. The biggest effort to bring a common compiler for both comes from GNU/GCC even though it's evolving slowly. Right now, the version of it that supports OpenACC is not distributed but programmers should recompile GCC with the appropriate flags to have it. In any case, it has better support than CUDA for multiple hardware vendors.

The other two standards have a completely different story, starting from the oldest:

*OpenCL*. It was born with the idea of being the portable standard of the future, and it respected that promise. OpenCL does not only works on GPUs but with the correct runtime library, it works also on CPUs letting developers choose where to run the code and how to optimize it. The problem with it comes from fragmentation, as stated in section 1.2. Every company decides to support up to a certain version of it, if programmers are not careful and use functions not covered by all the targeted hardware, the code would not be portable anymore. An example related to HPC is NVIDIA's decision to stop support at standard 1.2 until last month while AMD supported also version 2.0+, so some functions may not work on NVIDIA, breaking applications. Recently NVIDIA declared support for OpenCL 3.0 and the situation is flipped, even though standard 3.0 is closer to 2.2, rather than 1.2, so developers should get more portability and performance from this decision. This example is only in HPC because when targetting embedded systems the situation is even worst.

SYCL is the last standard that emerged, and it is possible to consider it the evolution and best version of *OpenCL*, these considerations are evident even in portability. The portability of code written in SYCL is extremely dependent on which compiler will be used as image 1.3 shows very well. Different companies support different hardware. I will make some points on the two compilers more related to Heterogeneous computation on GPUs. The first one is DPC++ open source project led by **Intel** and joined **Codeplay** last year. They aim to upstream their code for compiling SYCL to the original LLVM/clang. Their last version of it, SYCL 1.2, was entirely based on OpenCL, so the same portability is guaranteed as long as the runtimes libraries are installed on the systems. The current version, SYCL2020 now allows different backends to enable the same level of portability with better performance, e.g., on NVIDIA's GPUs it uses NVPTX backend, on AMD's GPUs it uses ROCm while, where the proprietary backend is not available, it still uses OpenCL. The second option in this environment is *hipSYCL* open source project, developed by Aksel Alpay and Vincent Heuveline at the University of Hamburg, which has a completely different approach. It exploits compilers from different vendors to make the code portable.

It is important to mention that the portability in SYCL doesn't stop at GPUs compilation, but it can be expanded also to FPGA, making it more future-proof. There already are other compilers that try to bring SYCL code on FPGA, like trySYCL from *Xilinx*, that have recently been thinking about joining forces with DPC++, and DPC++ itself has basic support for Intel's FPGA.

The following table sums up portability for different standards. SYCL column doesn't consider any particular compiler implementation, but the standard in general, as it is

#### 1 State Of The Art

|              | CUDA         | OpenACC      | OpenCL       | SYCL         |

|--------------|--------------|--------------|--------------|--------------|

| x86_64       | -            | _            | $\checkmark$ | $\checkmark$ |

| ARM          | -            | -            | $\checkmark$ | $\checkmark$ |

| NVIDIA's     | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| GPUs         |              |              |              |              |

| AMD's GPUs   | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Intel's GPUs | -            | -            | -            | $\checkmark$ |

| FPGA         | -            | -            | -            | $\checkmark$ |

done for OpenACC.

Table 1.1: Portability of code in different standards

In the coming years, the United States will open four new supercomputers for research purposes, and three of them don't have NVIDIA's GPUs but Intel's or AMD's ones. Specifically Intel will build *Aurora* [4] and AMD will build *Frontier* and *El Capitain* [3]. This means that the importance of portability of code is a fundamental aspect for them and all world of HPC. Even European Union is starting some new supercomputers based on AMD's GPUs, like Lumi [2] which will be the European more powerful supercomputer. Given these facts, the table 1.1 shows eloquently the situation and how SYCL is supposed to be the standard of the future.

## **1.6.3.** Performance

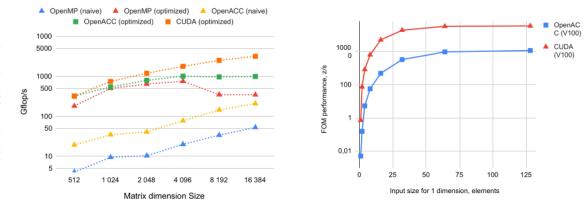

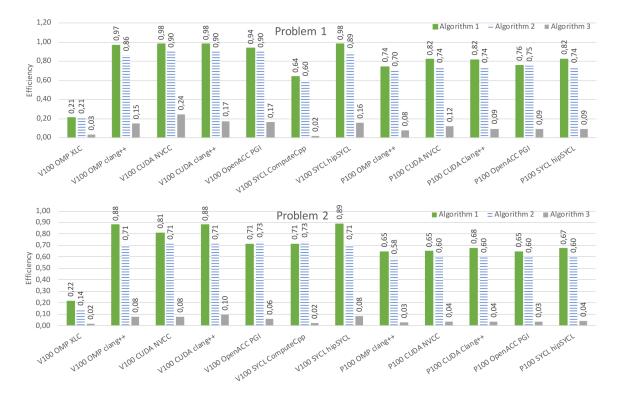

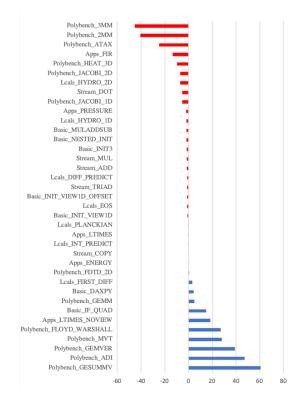

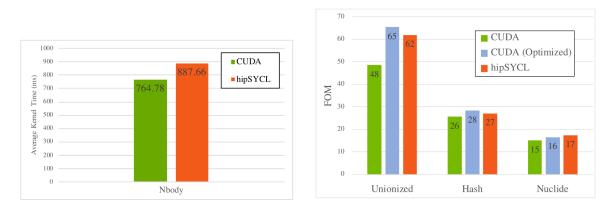

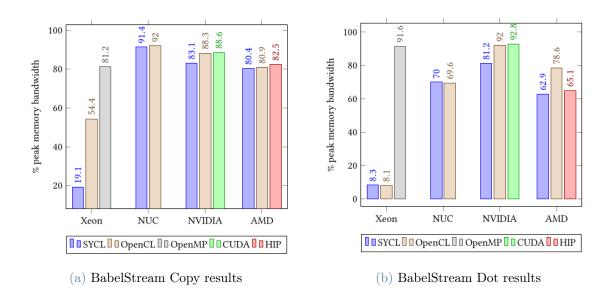

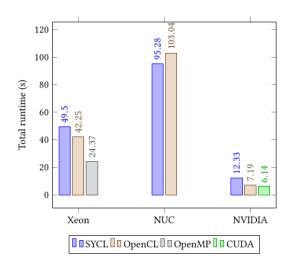

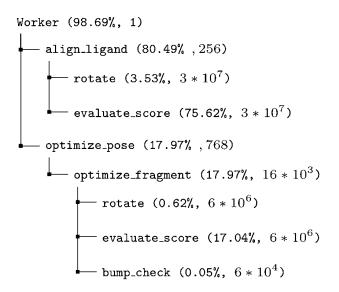

The last aspect to take into account is the *Performances*. This is even more important when choosing and analyzing a language/framework in the HPC world. Currently, there aren't any works that provide a complete comparison of all the considered frameworks. So I illustrate the situation by providing different views that allow me to make an extensive comparison of them. The scarcity of papers is mainly due to the very early stage of *SYCL*'s life. This problem is evident, particularly for what concerns its performance on GPUs. It is more difficult to have a complete overview since every implementation has slightly different results.

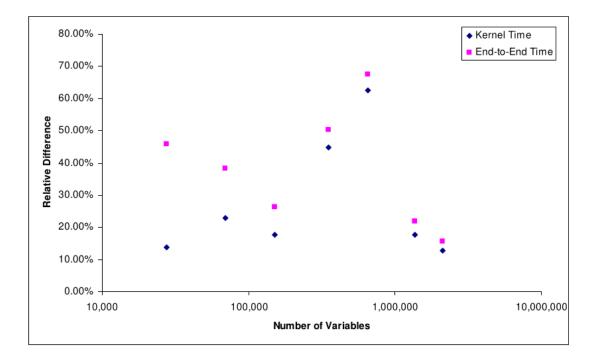

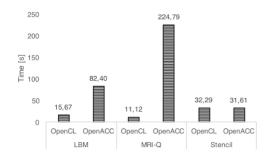

In comparing the frameworks, I start by looking at how CUDA and *OpenCL* compare to each other, then I see the two NVIDIA's standards compare to each other and for last I show the current state of the art of SYCL running on GPUs, primarily against the same implementation in CUDA, but also with comparisons with *OpenCL* and *OpenACC*.

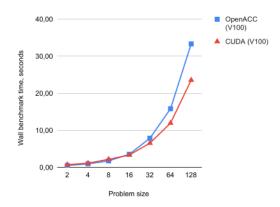

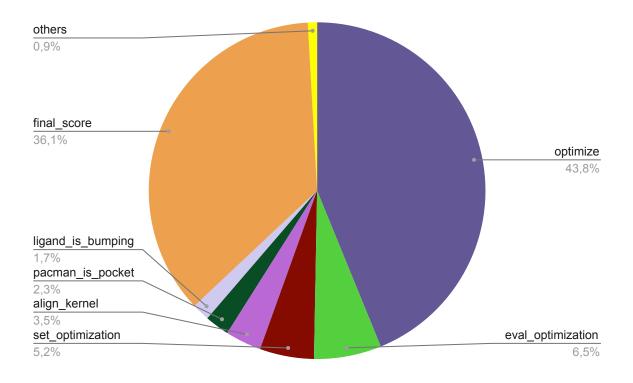

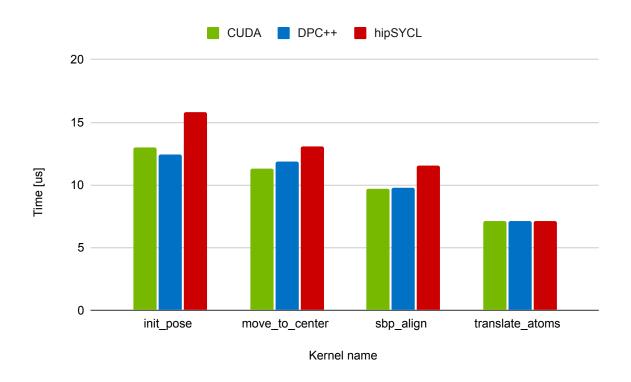

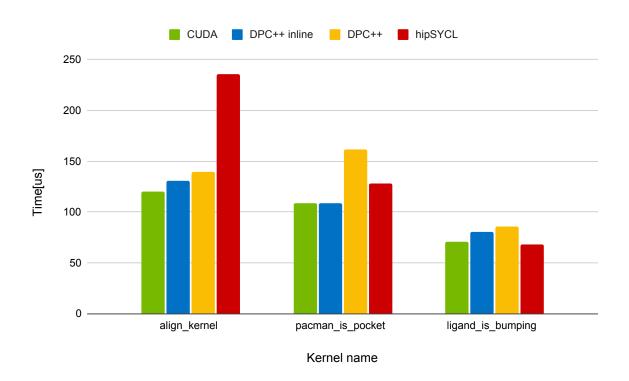

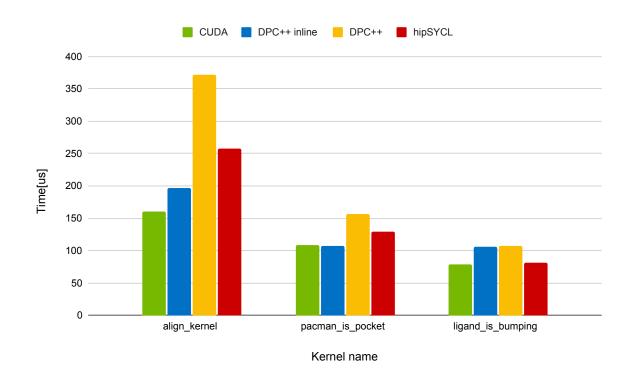

Figure 1.4: Relative difference in running time between CUDA and OpenCL, image from [16]