## Modeling and Fabrication of Electret-based 2D Micro Energy Harvester

Andrea Crovetto – 750342

## Supervisors

Dr. Roman Sordan, Politecnico di Milano Dr. Fei Wang, DTU Prof. Ole Hansen, DTU

## In collaboration with:

DTU Nanotech Institut for Mikro- og Nanoteknologi **DTU Danchip** Danchip

Master's Thesis for Physics Engineering Degree Politecnico di Milano, July 25th, 2012

# Preface

This Master's Thesis has been written in order to complete a M.Sc. program in Physics Engineering at Politecnico di Milano, Italy. The whole process has been supervised by Dr. Roman Sordan, head of the Nanoscale Device Group at L-NESS, Como, Italy

The backbone for this report has been an eight-month research stay (October 2011 - May 2012) at the Department of Micro- and Nanotechnology, Technical University of Denmark (DTU). I joined a pre-existing project (started in July 2010) on electret-based energy harvesting in the Silicon Microtechnology research group. The responsible scientist for the project, as well as my guide and supervisor, has been Assistant Professor Fei Wang.

Work has been carried out at the Nanotech Department (modeling, design, and project management), in the Danchip cleanroom (fabrication), and in the MEMS Laboratory (testing). All aforementioned facilities are located on DTU campus.

There are many people who deserve credit for their support within this project. They will be acknowledged at the end of this report.

**DTU Nanotech**

Department of Micro-and Nanotechnology Ørsteds Plads, Building 344 Technical University of Denmark 2800 Kgs. Lyngby, Denmark

# Contents

| Pı       | refac | e                                                        | II           |

|----------|-------|----------------------------------------------------------|--------------|

| A        | bstra | $\mathbf{ct}$                                            | $\mathbf{V}$ |

| R        | iassu | nto                                                      | VII          |

| 1        | Intr  | oduction                                                 | 1            |

|          | 1.1   | Wireless Sensor Networks                                 | 1            |

|          | 1.2   | Overview of Micro Energy Harvesting                      | 2            |

|          | 1.3   | Vibrational Harvesting and Introduction to our Device    | 3            |

|          | 1.4   | Thesis Outline                                           | 5            |

| <b>2</b> | The   | eory and Modeling                                        | 7            |

|          | 2.1   | Properties of Polymer Electrets                          | 8            |

|          | 2.2   | Corona Charging                                          | 12           |

|          |       | 2.2.1 Introduction $\ldots$                              | 12           |

|          |       | 2.2.2 Corona Setup                                       | 12           |

|          |       | 2.2.3 Physics of Charging                                | 13           |

|          |       | 2.2.4 Measurement of Implanted Charges                   | 16           |

|          | 2.3   | Electrical Domain                                        | 17           |

|          |       | 2.3.1 Introduction                                       | 17           |

|          |       | 2.3.2 Static Model                                       | 18           |

|          |       | 2.3.3 Dynamic Model                                      | 20           |

|          |       | 2.3.4 Results                                            | 23           |

|          | 2.4   | Mechanical Domain                                        | 26           |

|          |       | 2.4.1 Proof Mass Oscillation with Harmonic Source Motion | 26           |

|          |       | 2.4.2 FEM analysis                                       | 28           |

|          | 2.5   | Coupled Electromechanical System                         | 29           |

|          |       | 2.5.1 In-Plane Electrical Force Analysis                 | 29           |

|          |       | 2.5.2 Coupled Equations                                  | 30           |

|          |       | 2.5.3 Results                                            | 31           |

|          |       | 2.5.4 Correction with Simulated Capacitance              | 34           |

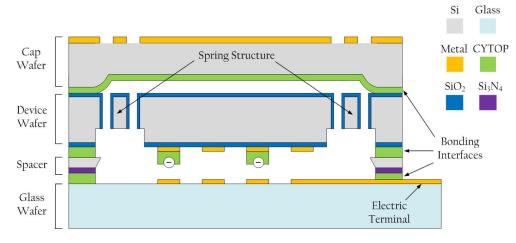

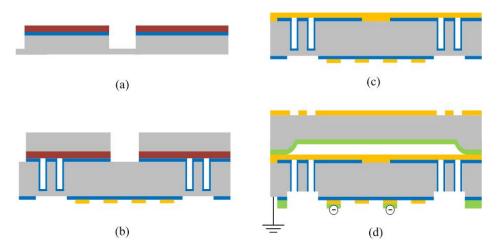

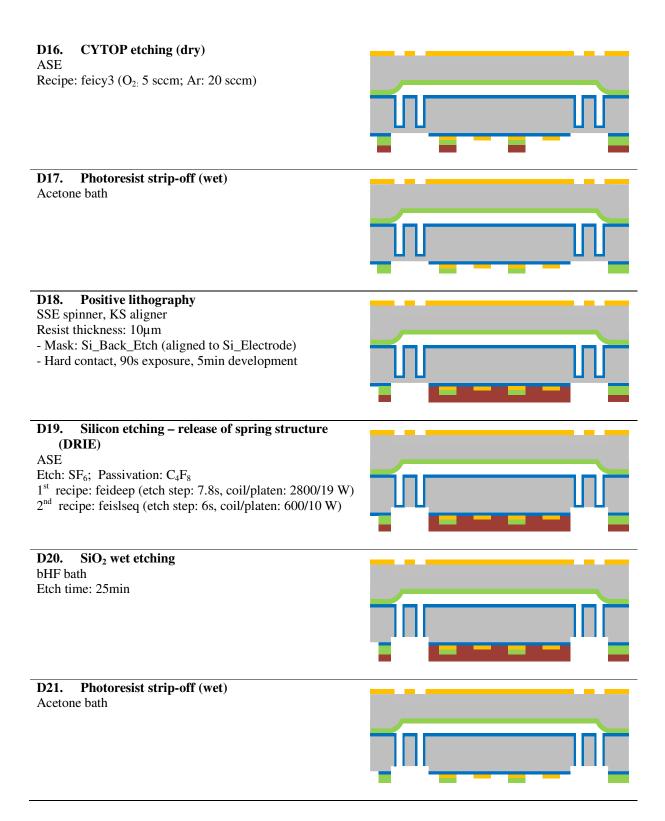

| 3        | Des   | ign and Fabrication                                      | 39           |

|          | 3.1   | Introduction to MEMS Fabrication                         | 40           |

|          | 3.2   | Process Flow Overview                                    | 40           |

|          | 3.3   | Cap Wafer                                                | 42           |

|          | 3.4   | Device Wafer                                             | 44           |

|          | 3.5   | Spacing Wafer                                            | 53           |

| CON | ITE | NTS |

|-----|-----|-----|

| COL |     | VID |

|              | 3.6   | Glass Wafer                          | 53 |

|--------------|-------|--------------------------------------|----|

|              | 3.7   | Corona Charging                      | 56 |

|              | 3.8   | Final Steps                          | 57 |

|              |       | 3.8.1 Device-Glass Wafer Bonding     | 57 |

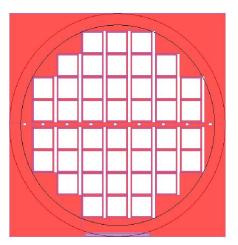

|              |       | 3.8.2 Dicing                         | 59 |

| 4            | Test  | ting and Results                     | 61 |

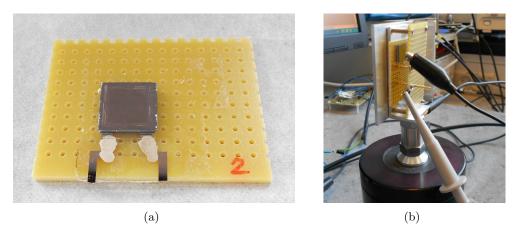

|              | 4.1   | Chip Preparation                     | 62 |

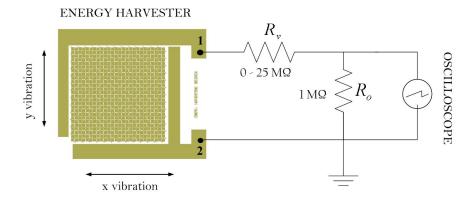

|              | 4.2   | Test Setup                           | 62 |

|              | 4.3   | Results and Model-Experiment Fit     | 63 |

| <b>5</b>     | Disc  | cussion and Future Improvement       | 67 |

|              | 5.1   | Modeling                             | 67 |

|              | 5.2   | Fabrication and Process Optimization | 68 |

|              | 5.3   | Testing                              | 70 |

|              | 5.4   | Parameter Optimization               | 70 |

| Co           | onclu | ision                                | 73 |

| $\mathbf{A}$ | Out   | -of-Plane Force Analysis             | 75 |

| в            | Fab   | rication Process Flow                | 79 |

| $\mathbf{C}$ | Equ   | ipment                               | 87 |

| A            | cknov | wledgements                          | 89 |

| Bi           | bliog | graphy                               | 91 |

## Abstract

A prototype micro energy harvester is designed, fabricated, and tested, with the goal of generating electrical power from two perpendicular ambient vibration components. Target vibration sources are typical machinery vibrations with low acceleration (0.01-0.5 g) and frequency in the 100-500 Hz range.

The device includes a suspended proof mass, which is excited at its resonance frequency by the vibration source. The transduction mechanism is induction charge flow between capacitor plates having a time-varying overlap due to proof mass oscillation. A permanent charge bias for electrostatic induction is provided by polymer electrets. The electret material is CYTOP<sup>©</sup>, which is patterned by Reactive Ion Etching and charged quasi-permanently up to  $-3.5 \times 10^{-4} \text{ C/m}^2$  with a corona setup. CYTOP is also employed as an adhesive material for full wafer bonding processes.

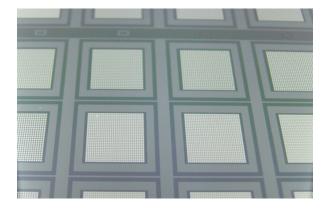

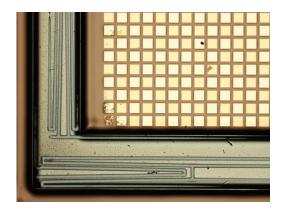

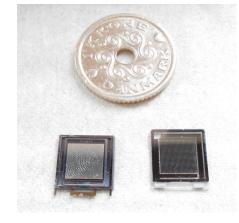

The harvester is fully packaged into a  $1.1 \times 1.0 \times 0.15$  cm chip fabricated with MEMScompatible wafer-level processes exclusively. As a result, device embedding into complex microsystems can be envisioned. Powering of wireless sensor network (WSN) nodes is one of the most promising applications.

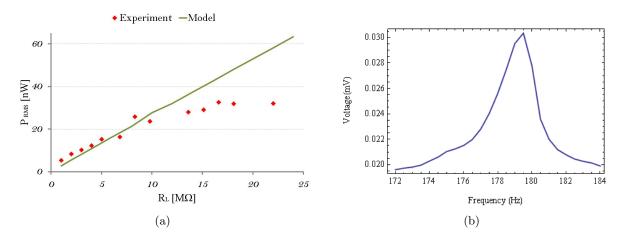

A new hybrid analytical/numerical model is proposed that describes the physics of the harvesting process and accurately predicts the device's operation performance. With the current device design, a maximum RMS power of 32.5 nW is achieved with a load of  $17 \text{ M}\Omega$ , a source vibration frequency of 179 Hz, and a source acceleration amplitude of 0.03 g.

The model suggests that power outputs as high as 90  $\mu$ W might be obtained by further optimization of device parameters and advances in a few key fabrication processes. Such performance level would render our energy harvester highly attractive for future applications.

## Riassunto

Nel presente lavoro si discute di un nuovo tipo di *micro energy harvester* progettato, fabbricato e testato nel corso di questa tesi. Lo scopo del dispositivo è ottenere potenza elettrica da sorgenti di potenza meccanica di tipo vibrazionale presenti nell'ambiente. Possibili sorgenti di simili oscillazioni sono macchinari industriali o casalinghi che spesso presentano uno spettro vibrazionale con picchi nella regione tra i 100 e i 500 Hz, caratterizzati da ampiezza sotto il  $\mu$ m e bassa accelerazione (0.01-0.5 g).

Il dispositivo comprende una massa inerziale collegata tramite molle a un sistema di riferimento solidale con la sorgente vibrante: il sistema deve essere progettato in modo tale da ottenere una frequenza di risonanza coincidente con uno dei picchi dello spettro vibrazionale della sorgente. Il meccanismo di trasduzione è il flusso della carica indotta elettrostaticamente su diversi condensatori. La carica si sposta da un condensatore a un altro poichè l'overlap tra le loro armature dipende dal tempo a causa dell'oscillazione della massa inerziale. Elettreti polimerici sono inclusi nel dispositivo per fornire una carica di bias che garantisce l'induzione elettrostatica. Il polimero usato è il CYTOP<sup>©</sup>, che sarà modellato da un processo di Reactive Ion Etching e caricato quasi-permanentemente fino a  $-3.5 \times 10^{-4} \,\mathrm{C/m^2}$  da una scarica corona in condizioni controllate. Il CYTOP sarà anche usato come materiale adesivo in processi di wafer bonding.

L'energy harvester è racchiuso in un chip di dimensioni  $1.1 \times 1.0 \times 0.15$  cm, interamente costruito con tecniche di microfabbricazione standard per i microsistemi elettromeccanici (MEMS). Si può dunque pensare di integrare il dispositivo in esame in microsistemi di elevata complessità. L'applicazione più naturale è la fornitura di energia a sensori a basso consumo connessi alla nascente tecnologia dei wireless sensor network (WSN). Se un energy harvester potesse essere integrato in ciascun nodo del network e fornisse potenza sufficiente a tutti gli elementi del nodo, le batterie potrebbero essere eliminate e non sarebbe richiesto alcun intervento di manutenzione elettrica.

Si propone inoltre un nuovo modello, in parte analitico in parte numerico, per descrivere la fisica dell'energy harvester e del processo di conversione. Si mostrerà che il modello è in grado di prevedere accuratamente il comportamento del dispositivo. Con il design e i parametri implementati in questa tesi, si raggiungerà una potenza massima (RMS) di 32.5 nW con un carico di 17 M $\Omega$  e una sorgente vibrante a 179 Hz con un'accelerazione di ampiezza 0.03 g.

Il modello suggerisce che potenze di output oltre i 90  $\mu$ W possono essere ottenute ottimizzando i parametri geometrici del dispositivo e raggiungendo un maggiore controllo di alcuni processi chiave nella fabbricazione. Un simile risultato renderebbe questo energy harvester molto promettente per future applicazioni.

## Chapter 1

# Introduction

## 1.1 Wireless Sensor Networks

A dense network of intercommunicating centimeter-sized wireless computers able to measure almost any quantity in the surrounding environment is starting to populate our world [1]. *Wireless sensor networks* (WSN) allow to ubiquitously monitor movement, pressure, temperature, pollution, location of persons, structural health of mechanical elements, and even human health. Radio-frequency (RF) wireless communication between sensor nodes allows them to be deployed in previously unaccessible places at only 1 to 10 meters from each other, which would be very costly for a wired system [2]. Each of these microsystems typically comprises: [3]

- one or more microsensors to physically interface with the environment

- an RF receiver and transmitter to exchange data with neighboring nodes

- a computational unit (microprocessor) to process sensor data and manage send/receive operations

- a device that supplies power to all these components

- an electric circuit to appropriately connect the various elements together

The standard way to power sensor nodes is through conventional batteries. Despite recent advances in low-power electronics resulting in a trend of ever-decreasing power requirements for both analog and digital circuits [4], the lifetime of a state-of-the-art non-rechargeable lithium battery for an typical sensor node is still less than one year [2]. Replacing billions of batteries on a regular basis is not feasible and impairs WSN technology from reaching its full potential. Additionally, sensor nodes often need to be placed in remote areas where maintenance is virtually impossible. For these reasons, there is a strong ongoing research effort focused both on prolonging battery lifetime and on experimenting new power sources with the ultimate goal of making future sensor nodes self-sustainable over their whole lifetime.

Energy may be provided by two main kinds of devices. *Energy reservoirs* (such as batteries, fuel cells, and micro heat engines) feature a pre-defined amount of stored energy: therefore the power they are able to provide decreases as the expected lifetime of the node increases. On the other hand *energy harvesters* are much like power plants, as they feature a transducer that instantaneously turns a form of ambient power into electrical power. If the ambient energy source is steadily available, the power supplied by such a device is not limited by the node's lifetime but solely by failure of its own components.

### **1.2** Overview of Micro Energy Harvesting

A micro energy harvester (also called micro energy scavenger or simply micro generator in the literature) is a device with features in the micro scale designed to "harvest" a specific form of energy from the surrounding environment and make it available to another appliance in the form of instantaneous electrical power. The collected power signal can be conditioned if necessary and either be used immediately to power the target device or be transferred into a separate energy accumulator. Depending on the selected energy source, the transduction mechanism into the electrical domain will vary. Table 1.1 gives a brief overview of energy harvesting technology as of today. Physical effects exploited for transduction, energy availability, state-of-the-art output powers, and limitations are listed.

Power requirements for WSN applications may vary to a great amount, but in general a higher power is needed for sensors with a higher signal rate of change. The amount of data transmitted by the RF apparatus also affects how much power needs to be harvested for correct functioning of the sensor node. The low power range is pW to nW for devices that only need to perform a few measurements per day or during their entire lifetime. A more common situation with frequent sampling would probably lead to power requirements of the order of  $\mu$ W or mW [11].

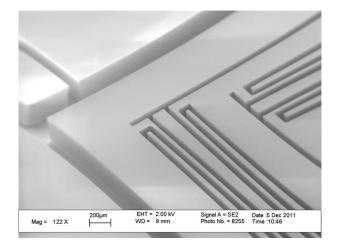

It is especially convenient to fabricate energy harvesters with MEMS fabrication techniques, as the device to be powered is likely to be manufactured with IC/MEMS processes as well. This allows for greater compatibility and easier integration of both elements (and related electrical circuits) on the same chip. Integration can be *monolithic*, i.e. with all components fabricated

| Energy<br>type      | Transduction                                                                                 | Sources                                                                                                                             | State of the art                                                                                                 | Limiting factors                                                                                                 |

|---------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Thermal             | thermoelectric<br>effect                                                                     | body heat, waste heat<br>(from plants, machinery,<br>lamps), daily tempera-<br>ture change                                          | 260 $\mu$ W/cm <sup>3</sup> with a<br>15°C gradient;<br>2200 $\mu$ W/cm <sup>3</sup> with a<br>35°C gradient [5] | temperature gradients,<br>Carnot efficiency                                                                      |

| Light               | photovoltaic<br>effect                                                                       | sunlight, artificial light                                                                                                          | $8000 \mu W/cm^3$ (full sun-<br>light); $4 \mu W/cm^3$ (office<br>lighting) [2, 6]                               | cloudy days, solar cell ef-<br>ficiency (15-20%), artifi-<br>cial source distance                                |

| Radio-<br>Frequency | receiving an-<br>tenna                                                                       | mobile phones, Wi-Fi<br>routers, laptops, tele-<br>vision/ radio broadcast<br>stations, mobile base<br>stations                     | 1000-5000 $\mu$ W (at 1m from a 3W transmitter);<br>10-100 $\mu$ W (at 10m) [7]                                  | governmental regula-<br>tions, transmitter's<br>distance and emitted<br>power, RF to DC<br>conversion efficiency |

| Vibrational         | electrostatic<br>induction,<br>electro-<br>magnetic<br>induction,<br>piezoelectric<br>effect | building walls/floors,<br>engines, bridges, vehi-<br>cles, industrial machin-<br>ery, kitchen/laundry<br>equipment, human<br>motion | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                             | source acceleration, vi-<br>bration direction, fre-<br>quency matching, inter-<br>mittent vibration              |

| Table | 1.1:                  | Energy  | harvesting | techniques |

|-------|-----------------------|---------|------------|------------|

| Table | <b>T</b> . <b>T</b> . | LICE S. | mar vooung | 000mmquob  |

on the same substrate, or different elements can be manufactured separately and then packaged together with assembling techniques [12].

Five serious issues need to be considered for most kinds of energy harvesters:

- 1. the size of the harvester must be kept under a certain threshold in order to be efficiently embedded into centimeter-sized microsystems. Above a size of 1cm<sup>3</sup>, the harvester would most likely dominate the system volume.

- 2. scavenged power under realistic environmental conditions must be high enough for its target application requirements. Since there are stringent requirements both on output power and size, a figure of merit for a generic harvester is volume power density, measured in  $[\mu W/cm^3]$ . This quantity has already been used in Table 1.1 to evaluate state-of-the-art harvesters. A target value that could suit a variety of applications is  $100 \,\mu W/cm^3$  [2].

- 3. parameters such as optimal load, signal frequency, voltage, and current must have reasonable values or it will be hard to make the harvested power available in the form needed by the target device.

- 4. if a predictable amount of energy is to be harvested per unit time, the ambient source should provide energy steadily or at least in a predictable way. Unpredictable sources make harvester design and optimization extremely difficult.

- 5. in general, none of the proposed harvesting techniques has a high degree of versatility. They all require environmental conditions that are quite peculiar, so every potential application must be evaluated separately and the harvester itself should be tuned each time to maximize power transfer from the available power source.

## **1.3** Vibrational Harvesting and Introduction to our Device

In vibrational energy harvesting a variety of acceleration sources and transduction mechanisms can be potentially employed in order to transform some mechanical power due to source vibration into usable electrical energy. A first distinction can be made between a *steady* and an *impulsive* vibration source. The former can be roughly approximated to a harmonic oscillator at constant amplitude and constant frequency, corresponding to a peak of the source's vibration spectrum (see Figure 1.1). Typical examples are machinery casings and human or animal bodies during regular motion, such as walking or running. The latter is characterized by acceleration impulses of a relatively large magnitude with a fast decay. It could be a slamming door, or tree branches being displaced due to air moved by a nearby car. We will not consider this kind of vibration source in our analysis.

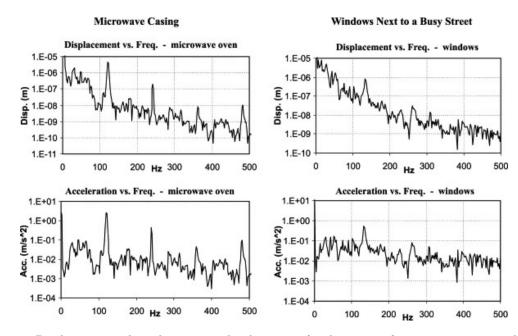

Steady vibration sources can be further split into human-based and machinery-based: it is found that human body motion typically features large displacement amplitudes (a few mm) and low frequencies (a few Hz). On the other hand, machinery vibration shows lower displacement amplitudes (from nm to  $\mu$ m) and higher frequencies (50-500 Hz) but similar accelerations (0.01-1g) [2]. Figure 1.1 shows measured vibration spectra of two sample machines. It is evident that machinery vibrations occur within a large bandwidth. Both spectra show relatively narrow amplitude peaks at a number of frequencies, suggesting that a resonant system could be devised in order to exploit the larger accelerations available at a few well-defined frequencies.

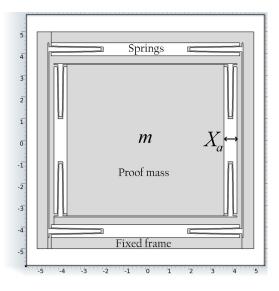

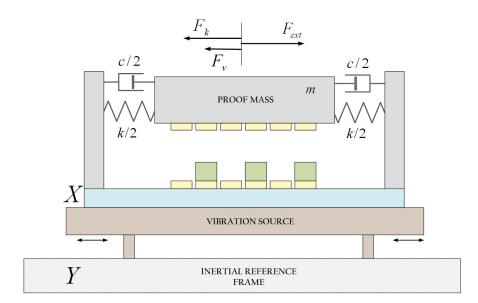

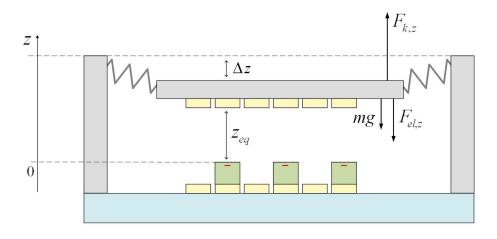

Machinery-based vibrations are chosen as the application target for the harvester proposed in this work. We will adopt an *inertial* mechanical system as the one shown in Figure 1.2. An inertial mass (or *proof mass*) is suspended to a fixed frame structure through a spring system. Source acceleration induces proof mass motion with respect to the frames. If the resonance

Figure 1.1: Displacement and acceleration amplitude spectra for the casing of a microwave oven and the base of a milling machine, measured with a piezoelectric accelerometer. Taken from [2].

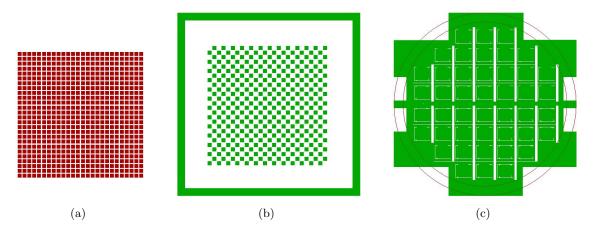

frequency of the proof mass is tuned to match one of the amplitude peaks in the source's vibrational spectrum, a *resonant* generator is achieved. The advantage of a resonant system is that, if the frequency is tuned correctly, a small source acceleration is sufficient to drive the proof mass to large oscillation amplitudes provided that its mechanical q-factor is not too low (see Section 2.4.1). Figure 1.2 shows that our design allows for easy proof mass oscillation along two perpendicular components. As will be shown in Chapter 2 and Figure 3.3, the device's electrical domain is also designed to allow for similar harvesting performance regardless of which of the two normal directions is excited. The idea behind 2D energy harvesting is that the acceleration direction of the source is often unknown, so a two-dimensional design increases the chance of the

Figure 1.2: Top side view of our harvester's mechanical domain. m is the proof mass,  $X_a$  is the maximum proof mass oscillation amplitude allowed by the spring system. The proof mass can vibrate in two perpendicular directions.

#### 1.4. THESIS OUTLINE

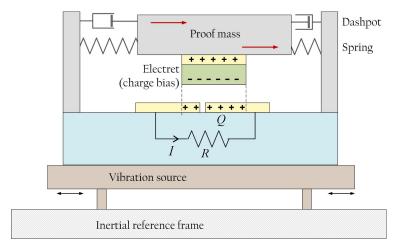

Figure 1.3: Simplified side view of our harvester during operation. Only three metal plates have been drawn for simplicity.

proof mass picking up vibrations coming from random directions. Three kinds of transduction mechanisms have been consistently employed in past resonant microgenerators:

- *piezoelectric* [10]: a flexible suspension, such as a cantilever beam, is fabricated with a piezoelectric material or at least coated with it. When it is mechanically stressed by an external vibration matching its resonance frequency, it generates charge cyclically due to the piezoelectric effect. The resulting current is led through a load resistance in order to obtain power.

- *electromagnetic* [9]: a few permanent magnets, mounted on a resonating cantilever beam, move with respect to a fixed coil. Because of the relative motion between a magnetic flux gradient and a conductor, a current is induced in the coil following Faraday's law, and it can be harvested by an external load.

- electrostatic [21]: With reference to Figure 1.3, a permanent charge or voltage bias is placed between two sets of capacitor plates in order to permanently induce charge on them. One set is fixed, while the other is situated on the moveable proof mass. When the mass vibrates, induction charges move periodically between connected capacitor plates due to capacitance changes related to a time-varying pattern overlap or to a time-varying gap. If a resistive load is connected between the plates where charge exchange occurs, it means that a power  $P = RI^2 = R (dQ/dt)^2$  is harvested, where Q is the total induced charge on the connected plates.

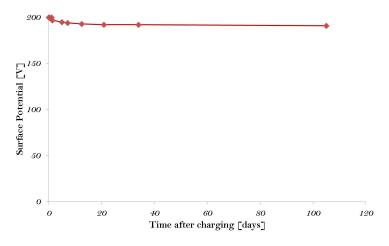

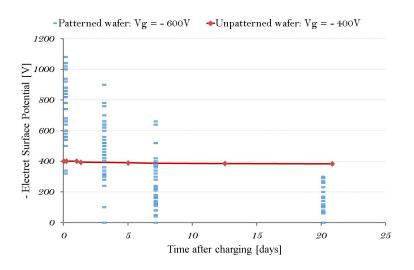

One problem about electrostatic harvesters is that they need an extra input voltage or charge in order to generate electric fields between the capacitor plates and thus induce charge on them. A practical solution is found by using *electrets*, i.e. dielectric materials with exceptional charge retention properties (see Section 2.1). Electrets can be patterned on top of one set of capacitor plates and charged with an appropriate technique as shown in Figure 1.3. In an ideal situation, only a negligible charge decay should be observed until months or years after the charging process (see [11] and also Figure 2.1 for a partial demonstration).

## 1.4 Thesis Outline

This thesis will describe the application of the electrostatic harvesting principle on a real device design, and will discuss its predicted and experimental performance.

Chapter 2 lays the theoretical base for understanding basic physics of electrets and of the electret charging process. A model for device operation is then proposed by following a successive approximation procedure that adds further refinement and corrections at each step, eventually leading to a nonlinear coupled electromechanical model with the inclusion of a FEM result.

Chapter 3 presents the actual device microfabrication step by step. Challenging processes are highlighted and discussed in detail, while constant reference is made to design choices and to how they compare to fabrication results.

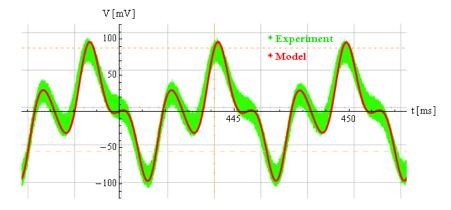

Chapter 4 describes the test setup used for characterization of the device output power and reports the few test results available. The level of agreement with the model of Chapter 2 is discussed, and a few unknown parameters are extrapolated from experimental results using the model.

Finally, Chapter 5 analyzes the results obtained in the different chapters and provides suggestions for future improvement in the next fabrication batches.

## Chapter 2

# Theory and Modeling

This chapter provides a modeling framework for the device proposed in the previous chapter. Section 2.1 presents basic properties of electrets. Types of stored charges, self-produced fields, charging methods, and charge decay mechanisms are briefly discussed, focusing on the material and techniques actually employed in this project. Section 2.2 gives theoretical background for electret charging using a corona setup and subsequent charge density measurement. Section 2.3 proposes a new electrical model of operation that applies to our harvester. In Section 2.4 a well-established model for inertial forced harmonic motion is shown. Finally, Section 2.5 couples the electrical and mechanical equations to find a general solution for proof mass motion and harvested power under a known source oscillation. A FEM study is also included to describe the effect of fringing fields on the device.

### 2.1 Properties of Polymer Electrets

An *electret* is a piece of dielectric material able to retain electrical charge *quasi-permanently*, i.e. the characteristic time constant for charge decay is much longer than the duration of the performed studies. If there is a non-zero net charge or if charges do not compensate everywhere in the material, Gauss's law states that an isolated electret produces a *constant external electric field*, which is also quasi-permanent (see Figure 2.1). Hence, charges can be induced on a conductive surface nearby according to the laws of electrostatics. This will be discussed in detail in Sections 2.2 and 2.3 for our specific device. In the following, a rectangular geometry as the one in Figure 2.2 will be assumed.

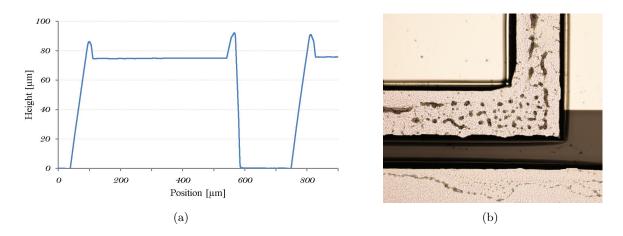

Figure 2.1: Experimental time decay of surface potential due to quasi-permanent surface charges on unpatterned  $10\mu$ m-thick polymer electret film

Many types of dielectric materials can be employed as electrets. Examples are microfabrication-friendly dielectrics like silicon dioxide or silicon nitride, and amorphous polymers such as Teflon. They are typically in thin-film form, with thickness in the  $1 - 100\mu$ m range. A feature of amorphous polymers is a change in physical properties around a characteristic glass transition temperature  $T_G$ . Above this temperature, the material turns from a brittle state into a rubber-like viscous state with a smooth step in its thermal expansion coefficient, specific heat and viscosity. This is caused by thermal energy being high enough to allow for significant sliding of the polymer's molecular chains [13]. Stored electrical charge can be of various nature (see Figure 2.2):

- molecular polarization charges: in the absence of an electric field, intrinsic electric dipoles present in polar molecules are randomly oriented because of the uniform angular distribution of thermal forces. If an external field is applied, a torque acts on the dipoles to align them to the electric field against the thermal drifts. As a consequence, a polar material shows an average polarization in the field direction. Permanent polarization in polymer electrets can be achieved by *thermal poling*. Because there is a characteristic dipolar activation energy, a field is applied to create a net polarization at a temperature high enough to allow for easy dipole orientation. Then the field is kept constant while the sample is cooled below its glass transition temperature, where thermal energy is far below the dipolar activation energy. As a result, the polarization is frozen and it shows a slow thermal decay with a dipole relaxation frequency that decreases with decreasing temperature [14, 15].

- *real charges*: positive or negative carriers are implanted in some parts of the material without discharging. According to their space distribution, they can be described as a

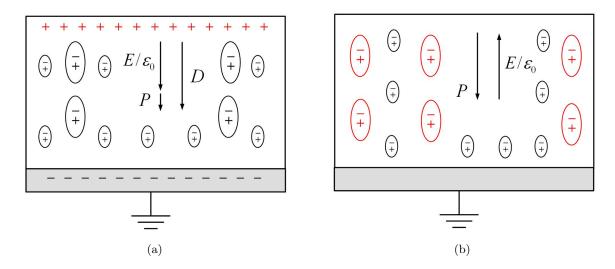

Figure 2.2: Self-fields on one-side metallized rectangular electrets. Quasi-permanent charges produced by charging techniques are drawn in red. Large and small dipoles represent molecular and atomic dipoles respectively. 2.2(a): uniform real surface charge layer.  $\hat{\mathbf{E}} \neq 0$  outside the electret because of its net charge, so counter charge is induced on the metal. 2.2(b): frozen uniform polarization charges. Because of charge balance,  $\hat{\mathbf{E}} = 0$  outside the electret and the metal has no induced charge

net surface or volume charge density, or as a combination of the two. Charges can be injected or deposited by contact electrification, discharges or electron/ion beams. Another technique is to generate carriers in the dielectric by radiation or heat while simultaneously separating them with an electric field. It should be remembered that, if the material is polar, the self-field given by a permanent real charge distribution will also induce a molecular polarization. Real charges are typically trapped in surface or bulk levels located in the energy gap between the valence and conduction band [14]. Their decay is associated to internal and external processes. *Internal* phenomena include ohmic conduction (from the few thermally activated intrinsic carriers) and real charge drift: electrons and holes that overcome the energy barrier between the valence and conduction band are accelerated by the internal field. The effect increases with temperature because of higher average thermal energy in carrier. Real charge diffusion involves motion of stored charges in the direction of their concentration gradient, but it usually plays a minor role. *External* processes are due to electric fields extending outside the electret and compensation charges being attracted to the electret surface in the form of atmospheric ions or polar particles.

• electronic polarization charges: It is important to note that non-polar materials can still be polarized by the electric field produced by their own real charge distributions, but this does not happen at a molecular level. Instead, it is a field-induced polarization due to the orientation of all *atomic* dipoles in the dielectric (consisting of nuclei and tightly-bound electrons) along the internal field direction. This type of polarization is present in all dielectrics and it is the reason why the relative permittivity  $\varepsilon_r$  is always strictly greater than 1, even in non-polar materials.

Inside an electret of any shape the general expression for the electric displacement is:

$$\hat{\mathbf{D}} = \varepsilon_0 \hat{\mathbf{E}} + \hat{\mathbf{P}}_{perm} + \hat{\mathbf{P}}_{ind} \tag{2.1}$$

where  $\hat{\mathbf{D}}$  is the electric displacement,  $\hat{\mathbf{E}}$  is the electric field,  $\hat{\mathbf{P}}_{perm}$  is the permanent fieldindependent polarization, and  $\hat{\mathbf{P}}_{ind}$  is the self-induced polarization. Therefore, the field in a charged electret  $\hat{\mathbf{E}}$  can be found by knowing  $\hat{\mathbf{P}}_{perm}$  and  $\hat{\mathbf{P}}_{ind}$ , and by applying Gauss's law for a dielectric:

$$\oint \hat{\mathbf{D}} \cdot u_n \, d\Sigma = Q_r \tag{2.2}$$

Here  $\Sigma$  is a closed 3D surface,  $u_n$  is the unit vector perpendicular to it,  $Q_r$  is the sum of all *real* charges located inside  $\Sigma$ . If the electret is charged with polarization-type charges, the equation

$$\hat{\mathbf{P}} = \varepsilon_0 (\varepsilon_r - 1) \hat{\mathbf{E}} \tag{2.3}$$

does not apply because it assumes that both molecular and electronic polarization are fieldinduced, while this is true only for electronic polarization. Thus,  $\hat{\mathbf{P}}_{perm}$  must be known and an expression of  $\hat{\mathbf{P}}_{ind}$  as a function of  $\hat{\mathbf{E}}$  must be given in order to find the electric field.

If the electret charging only results in real charge distributions the situation is simpler: all polarization charges are self-induced so Eq. 2.3 is applicable and Eq. 2.1 reduces to:

$$\hat{\mathbf{D}} = \varepsilon_0 \hat{\mathbf{E}} + \hat{\mathbf{P}}_{ind} = \varepsilon_0 \varepsilon_r \hat{\mathbf{E}}$$

(2.4)

Rearranging this equation yields

$$\hat{\mathbf{E}} = \frac{\hat{\mathbf{D}}}{\varepsilon_0 \varepsilon_r} = \frac{\hat{\mathbf{E}}_0}{\varepsilon_r}$$

(2.5)

It is then evident that the effect of self-induced polarization is a reduction of the internal field by a factor  $\varepsilon_r$  with respect to  $\hat{\mathbf{E}}_0$ , the field in the  $\hat{\mathbf{P}}_{ind} = 0$  case. For a simple rectangular geometry and uniform real surface charge layers the electric fields can simply be found by applying the following boundary condition to discontinuity interfaces, i.e. material boundaries and surface charge layers:

$$\hat{\mathbf{D}}_1 - \hat{\mathbf{D}}_2 = \varepsilon_0 \varepsilon_{r,1} \hat{\mathbf{E}}_1 - \varepsilon_0 \varepsilon_{r,2} \hat{\mathbf{E}}_2 = \sigma_{1,2} \hat{\mathbf{u}}_{n,1}$$

(2.6)

where  $\sigma_{1,2}$  is the real surface charge density at the interface,  $\hat{\mathbf{u}}_{n,1}$  is the unit vector normal to the surface pointing towards region 1 and the other quantities refer to regions 1 and 2 (see Figure 2.3). This equation will be applied in the next section to derive the electric fields in the regions around a non-polar electret with a single real surface charge density.

Figure 2.3: Interface between different  $\varepsilon_r$  materials with real surface charge layer

Charging of electrets is limited by breakdown effects. Dielectric breakdown takes place when charged particles in a dielectric start to accelerate under the effect of a strong electric field. The result is an avalanche ionization and a spark discharge in the dielectric, leading to the loss

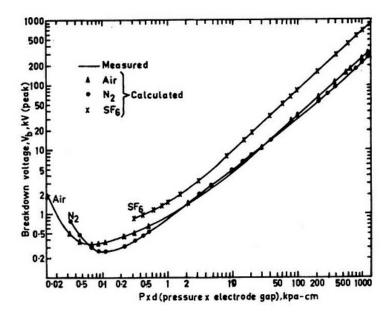

Figure 2.4: Paschen's curve for external breakdown in air and other fluids. Taken from [17]

of its insulating properties. External breakdown involves the fluid the electret is immersed in (typically air), while internal breakdown involves the electret itself.

External breakdown occurs when the voltage across the air gap between the electret and a metal electrode exceeds the value given by Paschen's law. This can be seen in Figure 2.4, where the breakdown voltage is plotted against the pressure–gap product. Paschen's curve has a minimum of 327V when pd = 0.08 kPa cm, which at atmospheric pressure means at a gap of about  $8\mu$ m. It is evident that at a given pressure, if pd is large enough, the breakdown voltage increases linearly with the gap so that the breakdown field is approximately constant and is often given as a reference for dielectric strength of materials. Paschen's law applies for air gaps above approximately  $3\mu$ m. Below this value, limitations given by field emission must be taken into account [16].

Internal breakdown is harder to quantify because it depends on the charge distribution in the electret. Assuming a permanent surface charge layer on one side and a metallized surface on the other, internal breakdown voltages for  $10\mu$ m-thick electrets can be extrapolated from reported studies and are listed in Table 2.1.

| Electret material | Breakdown voltage |

|-------------------|-------------------|

| Teflon            | 2kV [14]          |

| CYTOP             | 5kV [18, 19]      |

| $\mathrm{SiO}_2$  | 10kV [20]         |

Table 2.1: Approximate internal breakdown voltages for a few popular electret materials assuming a  $10\mu m$  thickness

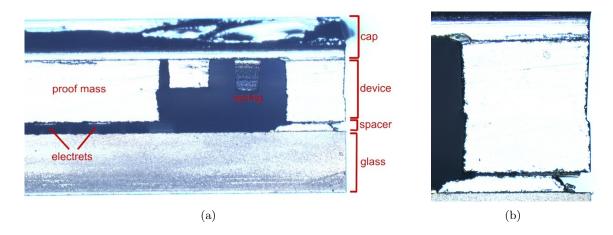

The electret material chosen for this project is CYTOP, an amorphous non-polar polymer processed to yield a thin film (about  $10\mu$ m) that is subsequently patterned into rectangles by plasma etching techniques (see also Section 3.2). The polymer is nonpolar, so molecular polarization charges can be neglected. Based on previous work on corona-charged CYTOP electrets [21, 11] it is assumed for the modeling that stored charges are situated in a uniform surface charge layer near the polymer's surface.

## 2.2 Corona Charging

#### 2.2.1 Introduction

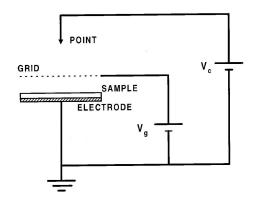

Corona charging is a popular discharge-based technique for injecting real charges into electrets. It has been employed in this project because it allows for a controlled and uniform deposition of surface charges at a high speed and relatively low cost. Electron-beam injection is far more expensive and complex to set up, while liquid contact electrification as shown in [22] is not applicable to our specific device. A corona setup is shown in Figure 2.5.

Figure 2.5: Schematic view of a corona charging setup. From [23]

A high voltage  $V_C$  is applied between a point-shaped electrode and a planar grounded electrode where the sample is placed. As a result, a discharge occurs and a current is observed in air if  $V_C$  is high enough (typically a few kV) to cause dielectric breakdown in the region near the electrode tip, where the field is the largest. This effect is enhanced by a very sharp tip, as charge accumulation in the regions with small radius of curvature produces a locally strong field. For a negatively biased tip, the discharge current is primarily made up by  $CO_3^-$  ions of thermal energy [14]. Because of their small energy, discharge ions have a low penetration depth into the sample and mostly deposit as a surface charge layer. It is assumed that they subsequently transfer their charge to surface traps in the electret. To achieve a high degree of control over the magnitude and uniformity of implanted charge, a wire grid is placed above the sample as seen in Figure 2.5. The grid is kept at constant voltage  $V_G$  to prevent the ions from accelerating towards the sample once its surface potential due to the charging has reached the value  $V_G$ . At the beginning the discharge current to the sample is "shadowed" by the grid wires but eventually the charge distribution on the sample surface is uniform if the charging time is long enough to allow the whole surface to reach the saturation potential  $V_G$ .

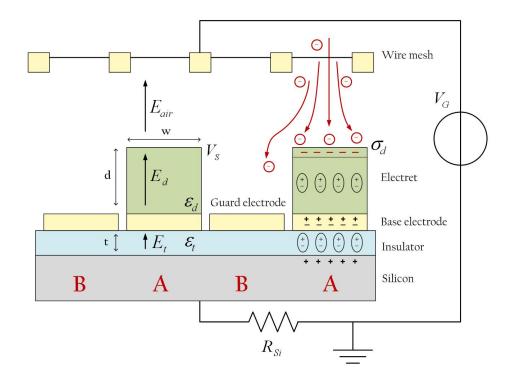

### 2.2.2 Corona Setup

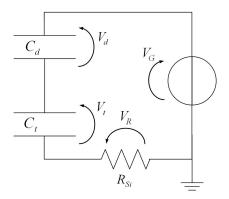

In Figure 2.6 a simple model for charging is shown. Our sample is a full doped silicon wafer with a pattern of rectangular electrets with thickness t and much larger in-plane dimensions. The electrets are metallized on the substrate side with floating *base electrodes*. Between the silicon wafer and the base electrode there is a thin insulating layer of SiO<sub>2</sub>. The silicon grounding is a critical matter for two reasons:

- 1. unlike metals, which typically have a resistivity of around  $10^{-8} \Omega m$ , n- or p-doped silicon wafers available at our facilities have a resistivity of  $10^{-1} \Omega m$ .

- 2. with the employed fabrication process flow, the only high-conductivity electrical path from

Figure 2.6: Model for electret charging. The sample is a simplified model of the device wafer fabricated for this project (see Chapter 3)

ground to the silicon beneath the electrets is through the device spring structure. The total cross sectional area for this structure is quite low.

For these reasons a significant resistance  $R_{Si}$  is expected between the silicon and the actual ground. For the theoretical model  $R_{Si}$  can be considered as zero because the effect of a finite resistance is mainly that of slowing down the charging, by introducing a time constant to the counter charge flow from silicon to ground.

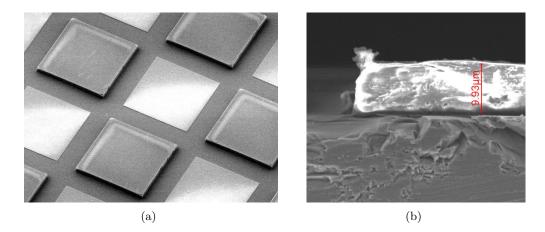

Guard electrodes are employed to improve charge uniformity on the electrets, as proposed by [11]. Uniformity issues arise when ions from the corona drift experience a repulsive electrostatic force from the already charged electret surface, so that their trajectory is deflected away and the electret surface never reaches the full potential of the grid. The effect is more pronounced at the electret edges. Due to this phenomenon, the ratio  $V_S/V_G$  between the measured electret surface potential and the grid potential decreases with a higher grid voltage and a smaller electret width. Thanks to the non-zero lifetime of deposited charges on guard electrodes, the regions next to the electrets are also charged to a certain amount, resulting in a lower repulsive force driving the corona ions away from the electret. The improvement in the maximum surface potential reached by the electrets has been measured experimentally by [11] to be between 20% and 42% for a line-space electret pattern with linewidths between 90 $\mu m$  and 180 $\mu m$ .

#### 2.2.3 Physics of Charging

A simple plane capacitor model is used for the A regions in Figure 2.6. Assuming that w and  $V_G$  are small enough to neglect ion deflection,  $E_{air} = 0$  in the region above the electrets after  $V_S$  has reached  $V_G$ . From Eq. 2.6 a boundary condition is applied at the air/electret interface:

Figure 2.7: Plane capacitor circuit model for region A

$$-\varepsilon_0 \varepsilon_d E_d = \sigma_d \tag{2.7}$$

so that the voltage drop across the electret is

$$V_d = \frac{E_d}{d} = -\frac{\sigma_d d}{\varepsilon_0 \varepsilon_d} \tag{2.8}$$

Because the base electrode is a floating conductor, it has two surface charge layers of magnitude  $-\sigma_d$  and  $\sigma_d$  on the electret side and insulating layer side respectively. A similar boundary condition can then be applied at the boundary between the base electrode and the insulator:

$$-\varepsilon_0 \varepsilon_t E_t = \sigma_d \tag{2.9}$$

so that the voltage drop across the insulator is

$$V_t = \frac{E_t}{t} = -\frac{\sigma_d t}{\varepsilon_0 \varepsilon_t} \tag{2.10}$$

Applying Kirchhoff's voltage law to the circuit as seen in Figure 2.7 results in:

$$V_G = V_d + V_t + V_R \tag{2.11}$$

Since  $V_R = 0$  when the current drops to zero after the charging is completed, the implanted surface charge density can be found using Eq. 2.8, 2.10, and 2.11:

$$\sigma_d = \frac{\varepsilon_0 V_G}{\frac{d}{\varepsilon_d} + \frac{t}{\varepsilon_t}} \tag{2.12}$$

Our designed device has approximately  $\varepsilon_d = 2$ ,  $\varepsilon_t = 4$ ,  $d = 10\mu m$ , and  $t = 1.5\mu m$ , which means that

$$\frac{d}{\varepsilon_d} \simeq 13 \frac{t}{\varepsilon_t} \tag{2.13}$$

so the insulating layer has little effect on the implanted charge density and can be neglected with an error of only  $1/14 \simeq 7\%$ , so a simpler expression for the charge density can be written as:

$$\sigma_d \simeq \frac{\varepsilon_0 \varepsilon_d V_G}{d} \tag{2.14}$$

This model assumes a clear distinction between region A and region B. In region A  $E_{air,A} = 0$ when the electret surface reaches  $V_G$ . In region B  $E_{air,B} \neq 0$ , the exact value depending on the

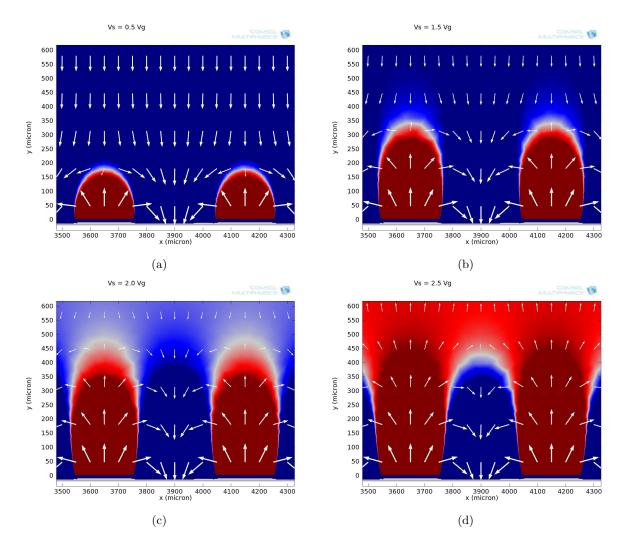

Figure 2.8: Simulated force vectors on corona ions located between the wire grid and the electret pattern for a few  $V_S/V_G$  ratios.  $200\mu m$ -wide electrets are placed on a grounded substrate and are spaced by  $250\mu m$ . No guard electrodes are present. The wire grid is kept at -200V and is 2mm away from the substrate. Colors refer to the *normal* component of the field with respect to the sample surface. Blue means attractive field, red means repulsive field. At the white border the normal field is zero. Note that the plane capacitor model predicts that the charging will stop when  $V_S = V_G$ . (a):  $V_S = 0.5V_G$ . (b):  $V_S = 1.5V_G$ . (c):  $V_S = 2V_G$ . (d):  $V_S = 2.5V_G$ .

instantaneous charge present in the base electrode. However, this is a limiting case only true at very small distances from the sample, where the overlap between  $E_{air,A}$  and  $E_{air,B}$  can be neglected. The distance between the wire grid and the sample is at least 10 times larger than the electret width, so near the grid  $E_{air,A}$  and  $E_{air,B}$  overlap almost completely. Eq. 2.14 is not valid anymore. Neglecting base electrode charging, in a full-overlap situation the total field is due to an array of point-like charges with magnitude  $\sigma_d A_{el}$  associated to each electret ( $A_{el}$  is the surface area of a single electret). Since the device area  $A_{tot}$  is about half covered by electrets, corona ions keep accelerating past the grid until

$$V_S = \frac{\sigma_d d}{\varepsilon_0 \varepsilon_d} = (A_{tot}/A_{el}) V_G \simeq 2V_G \tag{2.15}$$

To support this discussion, Figure 2.8 shows a simulation study. It is evident that the situation is qualitatively the same when  $V_S$  is well below  $V_G$  (Fig. 2.8(a)) and when  $V_S$  is well above  $V_G$  (Fig. 2.8(b)). The electric force on the corona ions is still attracting them towards

the surface until a distance that is comparable with the electret width. At this distance, an appreciable difference between region A and region B arises. Neglecting lateral deflection, corona ions can still reach the charged surface in region A if:

- 1. their kinetic energy in the normal direction is high enough to avoid inversion of motion before they reach the surface

- 2. their mean free path is at least comparable with the distance at which the normal force becomes repulsive.

It can be seen that when  $V_S = 2V_G$  the large-distance normal field has almost reached zero (Fig. 2.8(c)), and that when  $V_S = 2.5V_G$  it has become repulsive (Fig. 2.8(d)). This is because the surface coverage of electrets is a little less than  $\frac{1}{2}$ .

To conclude, a first limiting factor to the implanted charge is the  $E_{air,tot} = 0$  condition. This depends on  $V_G$  but also on the surface coverage of electrets  $A_{el}/A_{tot}$  as seen from Eq. 2.15. A second limiting factor is ion deflection. Therefore, the electrets may never reach the potential given by Eq. 2.15 due to the large lateral repulsive forces arising at a shorter distance, but it should be kept in mind that electret charging beyond the grid potential is possible. As discussed in chapter 3, a stable surface potential of slightly less than -400V has been measured for an electret pattern charged under a grid voltage of -200V with a  $\frac{1}{2}$  surface coverage.

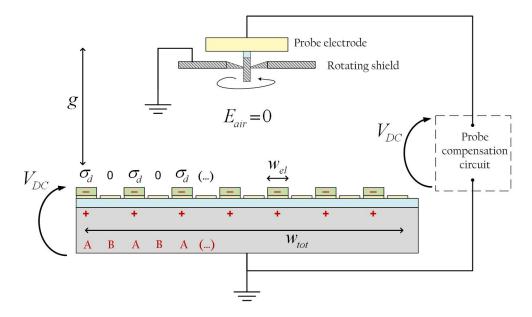

#### 2.2.4 Measurement of Implanted Charges

The surface potential measurement is carried out with a distance-compensated electrostatic voltmeter. Its operation principle is shown in Figure 2.9. A grounded rotating conductor periodically shields the probe electrode from the electric field produced by the stored charge in the electrets. As a result, induction charges on the probe electrode are modulated and an AC voltage signal is created in the probe. With a feedback mechanism, a DC voltage  $V_{DC}$  is applied between the probe electrode and the grounded substrate until the AC voltage drops to zero. Reaching this condition implies that there are no more induction charges on the probe electrode to cause an AC signal, and this only happens when  $E_{air} = 0$  near the probe. Therefore, according to Kirchhoff's voltage law the DC voltage equals the voltage drop between the charged surface and the grounded substrate [14].

Similarly to the discussion for corona charging, the actual electret surface charge density can be inferred if the probe electrode is far enough from the sample so that the fields in regions A and B overlap completely, but still close enough to neglect distance-dependent field decay, namely:

$$w_{el} \ll g \ll w_{tot} \tag{2.16}$$

In this configuration, the field close to the probe is due to a capacitor with area equal to the total device area  $A_{tot}$  and charge equal to the total stored charge in the electrets  $\sigma_d A_{el}$ . Then, using Eq. 2.15,  $V_{DC}$  is found to be:

$$V_{DC} = \frac{Q_d}{C} = \frac{\sigma_d A_{el}}{\varepsilon_0 \varepsilon_d A_{tot}/d} = \frac{A_{el}}{A_{tot}} V_S \simeq V_G \tag{2.17}$$

The fact that the surface potential measured by the electrostatic voltmeter is the wire grid potential  $V_G$  rather than the actual electret surface potential  $V_S$  can be misleading. It should be kept in mind that in order to find  $V_S$  a multiplication of the measured value by the factor  $A_{tot}/A_{el}$  is necessary.

Figure 2.9: Measurement of electret surface potential with distance-compensated electrostatic voltmeter

### 2.3 Electrical Domain

In this section a model is developed to derive electrical quantities assuming an ideal in-plane forced harmonic oscillation of the electret pattern with respect to a *counter electrode* pattern. No coupling is assumed between the electrical and mechanical parts. Such a study should only be regarded as a preliminary investigation for the fully coupled model presented in Section 2.5.

#### 2.3.1 Introduction

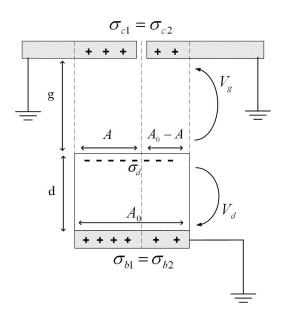

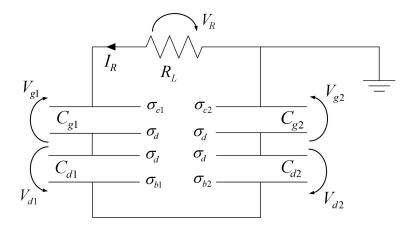

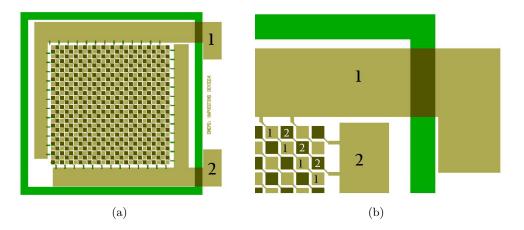

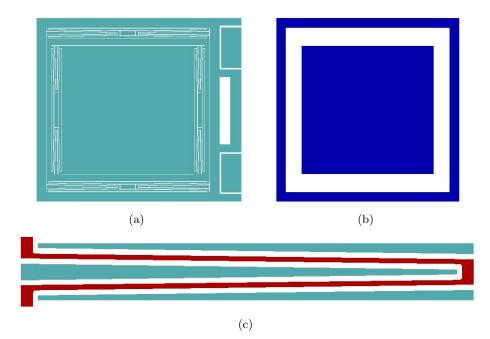

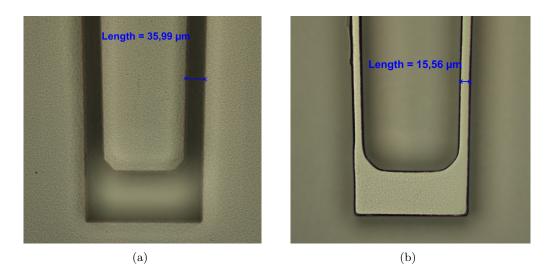

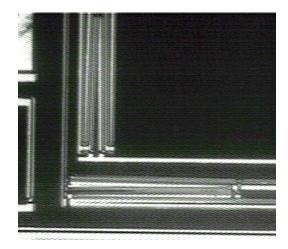

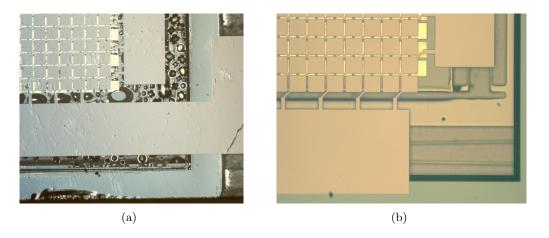

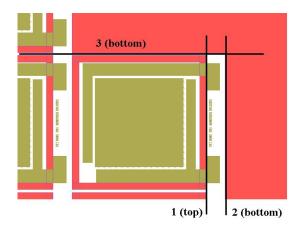

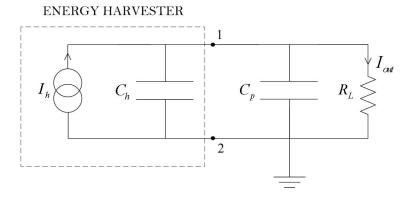

The electret and counter electrode patterns are located on a silicon and a glass substrate respectively (see also Chapter 3). Figure 2.10 gives an overview of the device electrical domain. Regions 1 and 2 both contain two time-varying capacitances due to the periodic change in overlapping area.  $C_c(t)$  is the one between the counter electrodes and the electret charge layer,  $C_b(t)$  is the one between the the electret charge layer and the floating base electrode. There is also another pair of capacitances between the base electrode and the silicon substrate across the insulating layer. Throughout the model, the spacing between counter electrodes is regarded as infinitely small. This is only an approximation as designed devices have spacings as large as  $30\mu m$  or  $50\mu m$  for an electrode width of  $200\mu m$  (see Chapter 3).

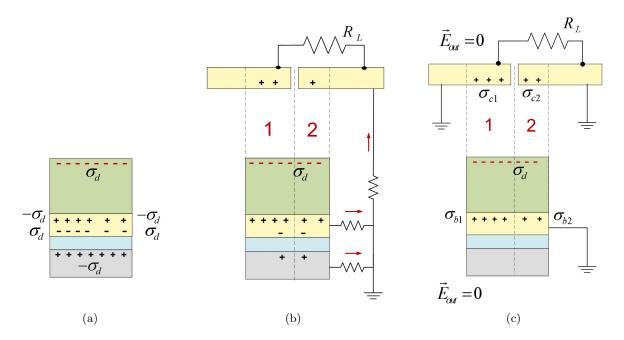

It is evident that the counter electrodes with label 1 are geometrically equivalent, and so are the ones with label 2. Then, connecting all the electrodes with the same label together is like connecting their associated capacitances in parallel. This reduces the problem to studying only a single electret "cell" made up of regions 1 and 2. The total effect can be simulated by multiplying the area of one counter electrode  $A_0$  by the number of cells n, which is like multiplying the capacitance by the same factor. The resistance  $R_L$  is placed between node 1 and node 2 to simulate the equivalent resistive load of the device to be powered by the harvester. A reference to ground is made at node 2. T Since it is practically impossible to connect the silicon substrate to ground with the current device design, it should be considered to be at floating potential. If a ground contact does occur for any reason, the model presented in the next section loses validity and reference to the model used by [24] or [11] should be made, where the substrate and counter electrode 2 are both at ground potential.

Figure 2.10: Overview of energy harvester electrical domain

### 2.3.2 Static Model

The validity of the equations used in the model is now discussed. A first assumption is that a plane capacitor model can be employed in which the capacitor width equals the overlap width between counter electrodes and electrets. Eq. (2.6) can then be used to calculate electric fields. This is only a rough approximation because the electret width is  $200\mu m$  and the gap between the two wafers is around  $100\mu m$ . Especially for small overlap areas, a significant contribution from fringing fields is expected, as has been shown by [25]. This effect will be estimated in Section 2.5.4.

Another assumption is that  $\hat{\mathbf{E}} = 0$  outside the system, i.e. the substrate and counter electrodes are at ground potential. Modeling becomes far more complex if this hypothesis is not met because the induced charges will be ill-defined, their actual value depending on electrical configurations outside the system. This problem can be solved by briefly grounding the substrate and counter electrodes at the same time before operation. If this is difficult to achieve in practice, one can wait until the very small currents due to a finite resistance between conductors and ground lead all conductive parts to ground potential (Figures 2.11(b) and 2.11(c)). Since in this situation  $\hat{\mathbf{E}} = 0$  outside the system, the fields generated by the different charge layers must compensate outside the system. With reference to Figure 2.12, the expression for each of these contributions to the field in air is

$$E_{\sigma_x} = \frac{\sigma_x}{2\varepsilon_0} \tag{2.18}$$

so the net fields outside the system for regions 1 and 2 are:

$$\begin{cases} E_1 = \frac{\sigma_d + \sigma_{b1} + \sigma_{c1}}{2\varepsilon_0} = 0\\ E_2 = \frac{\sigma_d + \sigma_{b2} + \sigma_{c2}}{2\varepsilon_0} = 0 \end{cases}$$

(2.19)

and therefore

$$\begin{cases} \sigma_d + \sigma_{b1} + \sigma_{c1} = 0\\ \sigma_d + \sigma_{b2} + \sigma_{c2} = 0 \end{cases}$$

(2.20)

**Figure 2.11:** Charge distributions at different stages of device fabrication. (a): After electret charging. (b): Slow charge flow to ground after placing the counter electrode pattern at the desired distance. (c): When all conductive parts have reached ground potential.

Using these relations, the fields within the electret can be written as:

$$\begin{cases} E_{d1} = \frac{\sigma_{b1} - \sigma_d - \sigma_{c1}}{2\varepsilon_0\varepsilon_d} = \frac{\sigma_{b1}}{\varepsilon_0\varepsilon_d} \\ E_{d2} = \frac{\sigma_{b2} - \sigma_d - \sigma_{c2}}{2\varepsilon_0\varepsilon_d} = \frac{\sigma_{b2}}{\varepsilon_0\varepsilon_d} \end{cases}$$

(2.21)

In a similar fashion, the fields in the air gap can be written as:

$$\begin{cases} E_{g1} = \frac{\sigma_{c1} - \sigma_d - \sigma_{b1}}{2\varepsilon_0} = \frac{\sigma_{c1}}{\varepsilon_0} \\ E_{g2} = \frac{\sigma_{c2} - \sigma_d - \sigma_{b2}}{2\varepsilon_0} = \frac{\sigma_{c2}}{\varepsilon_0} \end{cases}$$

(2.22)

In a static situation after the whole system has been grounded  $V_g = V_d$  so for region 1:

$$V_{g1} = V_{d1} \Longrightarrow E_{g1}g = E_{d1}d \Longrightarrow \frac{\sigma_{c1}g}{\varepsilon_0} = \frac{\sigma_{b1}d}{\varepsilon_0\varepsilon_d}$$

(2.23)

Substituting the first relation of Eq.(2.20) into the previous equation yields

$$\frac{\sigma_{c1}g}{\varepsilon_0} = \frac{(-\sigma_{c1} - \sigma_d)d}{\varepsilon_0}$$

(2.24)

By rearranging this equation and noticing that the same procedure can be applied to region 2, one finally gets:

$$\sigma_{c1} = \sigma_{c2} = -\sigma_d \frac{d}{d + \varepsilon_d g} = \sigma_{c0} \tag{2.25}$$

and

$$\sigma_{b1} = \sigma_{b2} = -\sigma_d \frac{\varepsilon_d g}{d + \varepsilon_d g} = \sigma_{b0} \tag{2.26}$$

Figure 2.12: Electrical model for grounded system with static overlap

Equations (2.25) and (2.26) are the *static* charge densities on base and counter electrodes once they have all reached ground potential. For our device  $d = 10\mu m$ ,  $g = 100\mu m$ , and  $\varepsilon_d = 2$ , so  $\varepsilon_d g \simeq 20d$ . Hence, 95% of the electret charge is induced on the base electrode and 5% on the counter electrode.

The system can be described (see Figure 2.11(a)) by equivalent capacitances

$$\begin{cases}

C_{g1} = \frac{A\varepsilon_0}{g} \\

C_{d1} = \frac{A\varepsilon_0\varepsilon_d}{d} \\

C_{g2} = \frac{(A_0 - A)\varepsilon_0}{g} \\

C_{d2} = \frac{(A_0 - A)\varepsilon_0\varepsilon_d}{d}

\end{cases}$$

(2.27)

and associated charges

$$Q_{g1} = A \sigma_c$$

$$Q_{d1} = A \sigma_b$$

$$Q_{g2} = (A_0 - A)\sigma_c$$

$$Q_{d2} = (A_0 - A)\sigma_b$$

(2.28)

where  $\sigma_c = \sigma_{c1} = \sigma_{c2}$ , and  $\sigma_b = \sigma_{b1} = \sigma_{b2}$ .

### 2.3.3 Dynamic Model

When an in-plane relative oscillation of the two patterns occurs, overlap areas become timedependent, i.e. A = A(t) and  $A_0 - A = A_0 - A(t)$ . If charge densities remained constant, there would be no difference with the static case because for a plane capacitor

$$V = \frac{Q}{C} = \frac{A(t)\sigma(t)}{\varepsilon_0 \varepsilon_d A(t)/d} = \frac{\sigma(t)d}{\varepsilon_0 \varepsilon_d}$$

(2.29)

Figure 2.13: Circuit representation of operating energy harvester.  $\sigma_d$  and  $R_L$  are constant, whereas all other quantities are time-dependent.

If  $\sigma(t)$  was constant all voltages would be the same as in the static model and there would be no voltage drop across the load resistance and no harvested power. Charge flow from counter electrode 1 to counter electrode 2 does not occur instantaneously, due to the finite response time of the system

$$\tau = R_L C_h \tag{2.30}$$

where  $\tau$  is the characteristic time constant for capacitor charging, and  $C_h$  is the equivalent capacitance in parallel with the load resistance. There are substantial differences in the employed equations with respect to the static case (regarding sign conventions, reference should be made to Figure 2.13):

- 1. Eq. (2.20) describing complete charge induction is not strictly valid anymore. This is because now only one counter electrode is locked at ground potential. The electric potentials of other electrodes depend on this reference potential and on the instantaneous physical configuration of the system. Therefore it is not true anymore that the electric field is zero outside the system, and a net induced charge can appear on external grounded conductors. However, if such external elements are kept reasonably far from the system, the field between them and the non-grounded electrodes will be very low since it scales inversely with distance. So Eq. (2.20) will be used again.

- 2. Kirchhoff's voltage law should be applied for the whole circuit in Figure 2.13 as

$$V_R = V_{g2} - V_{d2} + V_{d1} - V_{g1} \tag{2.31}$$

- 3. Voltages for all capacitors can still be found by using Eq. (2.22).

- 4. The voltage drop across the load resistance considering all n electret cells can be written as

$$V_R = R_L I_R = R_L \frac{dQ_{c1}}{dt} = R_L \frac{d(nA\,\sigma_{c1})}{dt}$$

(2.32)

5. Since the base electrode is electrically isolated, conservation of its total charge is required:

$$A \sigma_{b1} + (A_0 - A)\sigma_{b2} = A_0 \sigma_{b0} \tag{2.33}$$

where  $\sigma_{b0}$  is the static base electrode surface charge density found with Eq. (2.26).

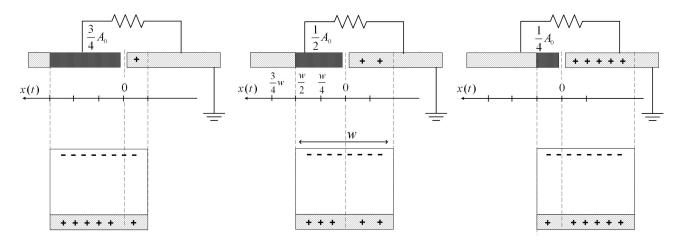

Figure 2.14: Schematic view of equilibrium point (center) and oscillation extrema (left, right)

To sum up, the following set of simultaneous equations has to be satisfied:

$$\begin{cases} \sigma_{d} + \sigma_{b1} + \sigma_{c1} = 0 \\ \sigma_{d} + \sigma_{b2} + \sigma_{c2} = 0 \\ R_{L} \frac{dQ_{c1}}{dt} = V_{g2} - V_{d2} + V_{d1} - V_{g1} \\ A \sigma_{b1} + (A_{0} - A)\sigma_{b2} = A_{0}\sigma_{b0} \\ V_{g1} = \frac{(\sigma_{c1} - \sigma_{d} - \sigma_{b1})}{2\varepsilon_{0}}g \\ V_{d1} = \frac{(\sigma_{b1} - \sigma_{d} - \sigma_{c1})}{2\varepsilon_{0}\varepsilon_{d}}d \\ V_{g2} = \frac{(\sigma_{c2} - \sigma_{d} - \sigma_{b2})}{2\varepsilon_{0}}g \\ V_{d2} = \frac{(\sigma_{b2} - \sigma_{d} - \sigma_{c2})}{2\varepsilon_{0}\varepsilon_{d}}d \\ Q_{c1} = nA \sigma_{c1} \end{cases}$$

(2.34)

If the functional form of A(t) is known, there are 9 variables and 9 independent equations (8 algebraic, 1 differential) so no more relations are needed to find a solution. By substitution, an ordinary differential equation in  $Q_{c1}$  (from now on just called Q for simplicity) is left to solve, that is:

$$\frac{dQ(t)}{dt} = -\frac{A_0(d\varepsilon_d + g)}{\varepsilon_0\varepsilon_d RnA(t)[A_0 - A(t)]}Q(t) + \frac{A_0d\sigma_d}{\varepsilon_0\varepsilon_d R[A_0 - A(t)]}$$

(2.35)

or, grouping the coefficients,

$$\frac{dQ(t)}{dt} = -m(t)Q(t) + n(t)$$

(2.36)

This is a linear first-order ODE: *linear* because Q and  $\dot{Q}$  appear with the power of 1, and of *first-order* because the first derivative is the highest-order derivative. A sinusoidal oscillation with constant amplitude of the two electrode patterns with respect to each other will be assumed for this model, such as

$$x(t) = X_a \sin(2\pi f t) \tag{2.37}$$

where x(t) is the displacement from the equilibrium position  $x_0$ ,  $X_a$  is the oscillation amplitude, and f is the oscillation frequency. If the electret surface is simply a square with dimensions  $w \times w$

| Air gap                                | g               | $100 \mu m$                      |

|----------------------------------------|-----------------|----------------------------------|

| Electret thickness                     | d               | $10 \mu m$                       |

| Electret length and width              | w               | $200 \mu m$                      |

| Number of electret cells in one device | n               | 450                              |

| Oscillation frequency                  | f               | 200 Hz                           |

| Electret surface charge density        | $\sigma_d$      | $3.54 \times 10^{-4} \mathrm{C}$ |

| Load resistance                        | R               | $1 G\Omega$                      |

| Electret relative permittivity         | $\varepsilon_d$ | 2                                |

Table 2.2: Parameters used to solve Eq.(2.36).

and overlap only varies in one direction, then the maximum obtainable overlap area is  $A_0 = w^2$ and the instantaneous overlap area is  $A(t) = w[x(t) + x_0]$ . If  $X_a = w/4$  and the equilibrium configuration is given by the electret laying exactly in the middle between counter electrodes 1 and 2, it follows that for the overlap area:

$$A(t) = \frac{A_0}{2} + \frac{A_0}{4}\sin(2\pi ft)$$

(2.38)

so that A(t) oscillates harmonically between  $A_0/4$  and  $3/4A_0$  (see also Figure 2.14).

#### 2.3.4 Results

This expression is now plugged into Eq. (2.35). An analytical solution for the equation has not been found. Therefore, an explicit expression for the output power cannot be provided. To get at least an idea of the optimal load, the model found in [11] is employed. According to this model, both the base electrode and one counter electrode are grounded and the optimal load can be found analytically to be:

$$R_{opt} = \frac{d + \varepsilon_d g}{\varepsilon_0 \varepsilon_d 2\pi f n A_0 / 2} = \frac{d + \varepsilon_d g}{\varepsilon_0 \varepsilon_d \pi f n A_0}$$

(2.39)

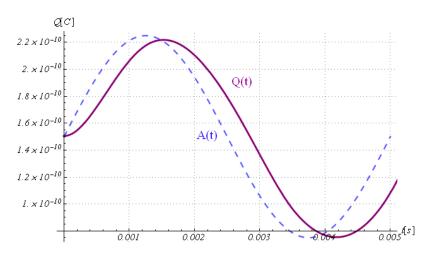

resulting in  $R_{opt} = 1.05 \,G\Omega$  for our device parameters, seen in Table 2.2. Using this optimal load, Eq. (2.35) is now solved numerically with the *NDSolve* algorithm provided by Wolfram Mathematica<sup>©</sup>. Since  $A(0) = A_0/2$  it seems reasonable to impose the following initial condition to the Cauchy problem:

$$Q(0) = \frac{nA_0}{2}\sigma_{c0}$$

(2.40)

where  $\sigma_{c0}$  is the static surface charge density on the counter electrodes found in Eq. (2.25). The numerical solution with parameters given by Table 2.2 is plotted in Figure 2.15. A comparison is made with the overlap area oscillation given by Eq. (2.38). It is evident that the charge signal is delayed with respect to the mechanical oscillation. The signal seems to stabilize at the same frequency f of the oscillation, with a phase shift that will be quantified later in this section. The numerical solution becomes unstable after one period of oscillation, so no information can be extracted beyond this limit. Because of this restriction, the following optimization loop is implemented in Mathematica to find the best fit for the phase shift of the charge function:

1. the *FindFit* function is used to fit the numerical solution to a function in the form

$$Q_{fit}(t) = \frac{Q_{max} + Q_{min}}{2} + \left(\frac{Q_{max} - Q_{min}}{2}\right)\sin(2\pi f t + \varphi)$$

(2.41)

where  $Q_{max}$  and  $Q_{min}$  are the maximum and minimum values of the previously calculated charge function, f is the mechanical oscillation frequency, and  $\varphi$  is the phase shift.  $\varphi$  is the only fitting parameter as the others are known.

**Figure 2.15:** *Purple*: numerical solution of Eq. (2.35) for charge on counter electrode 1, with Eq. (2.40) as an initial condition. *Blue*: normalized plot of A(t).

- 2. the differential equation of the system is solved again with  $Q(0) = Q_{fit}(0)$  as an initial condition.

- 3. the procedure is repeated until an acceptable fit is found.

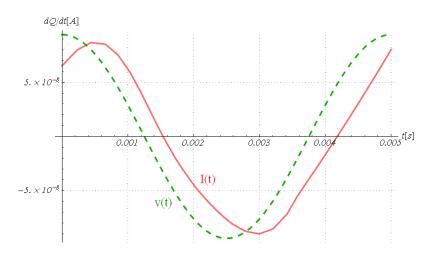

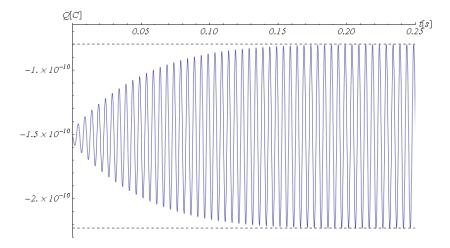

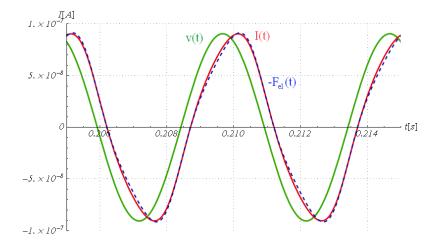

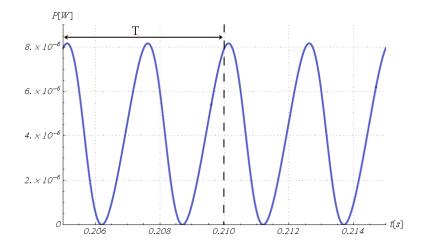

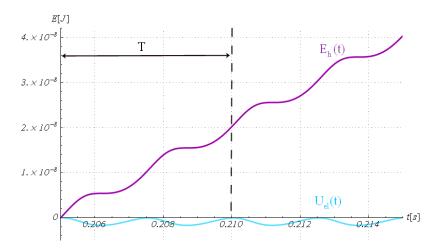

After a few loops a better approximation of  $\varphi$  is found. For the parameters shown in Table 2.2,  $\varphi \simeq 0.192\pi \simeq \frac{\pi}{5}$ . This procedure also allows to visualize easily from Figure 2.16 that also the electric current signal dQ/dt has a similar phase shift with respect to the velocity of the oscillator. This is of course expected because they are the derivatives of Q(t) and x(t) respectively. The instantaneous harvested power is simply the power dissipated in the load resistance:

$$P_h(t) = I^2(t)R = \left(\frac{dQ}{dt}\right)^2 R \tag{2.42}$$

Since the power signal is approximately a squared sine function, its RMS value is simply 1/2 of its maximum value. Hence the predicted harvested power with the current parameters is:

$$P_{h,rms} = P_{max}/2 \simeq 4\mu W \tag{2.43}$$

**Figure 2.16:** *Red*: electrical current signal as the derivative of charge signal found with optimization procedure. *Green*: normalized plot of area overlap velocity.

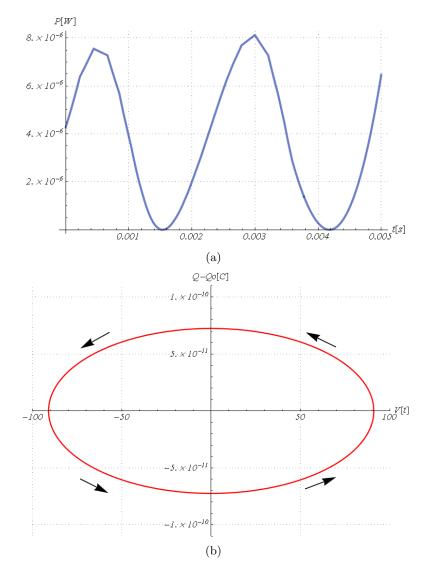

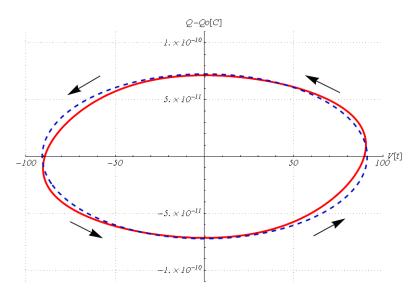

Note that this value can also be derived by calculating the area of the  $Q - V_R$  hysteresis loop, where  $V_R$  is the voltage drop across the load resistance. This area corresponds to the irreversible work done by the vibration source to move charge across the voltage  $V_R$  in one period T of oscillation. Since the hysteresis loop is roughly elliptical, its area is approximately

$$E_T = \pi (V_{max} - V_{min})(Q_{max} - Q_{min}) \simeq 26nJ$$

(2.44)

The harvested power is then

$$P_{h,rms} = E_T / T = E_T f = 4.1 \mu W \tag{2.45}$$

in good agreement with the value found using the power signal. Note that in this calculation the harmonic fit to Q(t) found with Eq. (2.41) has been used.

Figure 2.17: Two ways to calculate power output. (a): From power signal across the load resistance. (b): From hysteresis loop for counter electrode charge with respect to voltage drop in load resistance.

## 2.4 Mechanical Domain

In this section the main mechanical forces acting on the harvester are described, so that an equation of motion can be written for the device assuming no coupling with the electrical domain. A Finite Element analysis is included in order to estimate the resonance frequency of the device spring system.

### 2.4.1 Proof Mass Oscillation with Harmonic Source Motion

The proof mass is excited by the motion of a vibration source, which is modeled as a onedimensional harmonic oscillation of frequency f and amplitude  $Y_0$  with respect to an *inertial* reference frame Y:

$$y(t) = -Y_0 \sin(2\pi f t)$$

(2.46)

Of course this is only a rough approximation because the vibration source will most likely have many other harmonic components at different frequencies and directions [2]. However, a resonant system only responds to a narrow frequency range around its resonance frequency, so the latter can be designed to match a peak of the source vibration spectrum. Additionally, our device design allows two perpendicular in-plane source motion components to excite proof mass vibration, but a 2D analysis would considerably complicate the electrical model.

Following [26], a non-inertial reference frame X that follows the vibrating source is now introduced to simplify the analysis. If x and  $\tilde{y}$  are the proof mass displacements with respect to X and Y, then

$$x = \tilde{y} - y \tag{2.47}$$

With such conventions, forces on the proof mass can be described with respect to reference frame X:

•  $F_{ext}$  is the force due to source vibration, i.e. relative motion between reference frames X and Y. From Eq. 2.47,  $m\ddot{x} = m\ddot{\tilde{y}} - m\ddot{y}$  but if this force is considered alone  $m\ddot{\tilde{y}} = 0$ . Hence  $F_{ext} = -m\ddot{y}$  in the X reference frame, which can be calculated from Eq. 2.46.

Figure 2.18: Schematic view of device's mechanical domain.

#### 2.4. MECHANICAL DOMAIN

- $F_k = -kx$  is the elastic force due to the spring structure between the proof mass and the device casing.  $k = 4\pi^2 f_o^2 m$  is the total spring constant of the spring system, and  $f_o$  its resonance frequency.

- $F_v = -c\dot{x}$  is a viscous damping force due to air resistance, symbolized by the dashpots in Figure 2.18.  $c = 2\pi m f_o/q$  is the damping constant and q is defined as the quality factor of the mechanical system.

Then the following equation of motion for the proof mass can be written:

$$m\ddot{x} = F_{net} = F_{ext} + F_k + F_v = -m\ddot{y} - kx - c\dot{x}$$

(2.48)

If this equation is solved, the following steady-state solution is found:

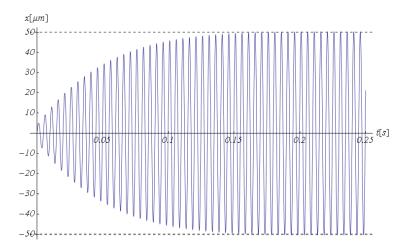

$$x(t) = X_0 \sin(2\pi f t - \psi)$$

(2.49)

This means that, after a transient, a viscously-damped proof mass will oscillate harmonically at the same frequency of the vibration source. The oscillation amplitude  $X_0$  shows a peak for f around  $f_o$  and has the following limiting values:

$$X_{0} = \begin{cases} Y_{0} & f \ll f_{o} \\ q Y_{0} & f = f_{o} \\ 0 & f \gg f_{o} \end{cases}$$

(2.50)

The last condition only applies if the quality factor is large enough  $(q \gg 1)$ , i.e. when viscous damping is reasonably low. From [26], the peak width at 1/2 of its maximum value (FWHM) can also be estimated by knowing the q-factor:

$$FWHM = \Delta f = \frac{f_o}{q} \tag{2.51}$$

Therefore, a low q-factor results in a sharp resonance peak with a large amplitude and a narrow bandwidth, whereas a high q-factor leads to a lower-amplitude peak with a broader bandwidth.

The phase delay  $\psi$  with respect to the source oscillation  $X_0$  is:

$$\psi = \begin{cases} 0 & f \ll f_o \\ \frac{\pi}{2} & f = f_o \\ \pi & f \gg f_o \end{cases}$$

(2.52)

where the sharpness of the transition between 0 and  $\pi$  increases with an increasing q-factor.

It can be concluded from this model that, at resonance, the oscillation of the proof mass is closely related to that of the source. It will be delayed by 1/4 of a period and amplified by the q-factor.

The simple mechanical model presented in this section does not take into account any electrical force on the proof mass, so it is only valid in the case of weak electromechanical coupling. However, it can serve as a reference to estimate the mechanical q-factor from experimental data whenever coupling is absent, as for uncharged electrets. Additionally, it proves useful if the electrical force is approximately proportional to velocity. In such a case, an electrical damping constant can be added to the mechanical damping constant, yielding a "mechanical" and an "electrical" q-factor. This has been successfully done by Williams and Yates [27] but cannot be applied to our harvester, as will become evident in Section 2.5.

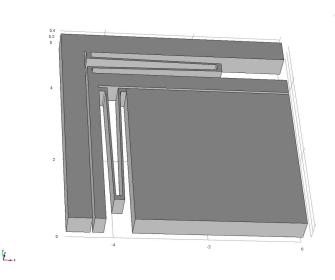

Figure 2.19: 3D view of spring system between the proof mass and the device casing.

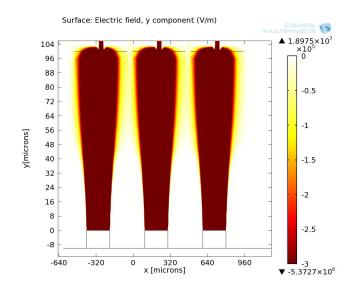

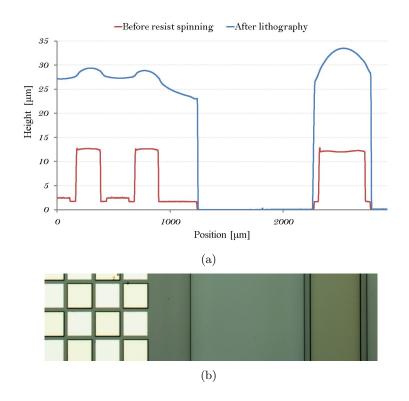

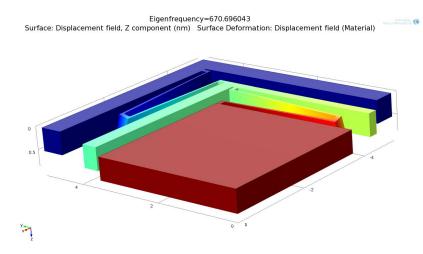

#### 2.4.2 FEM analysis

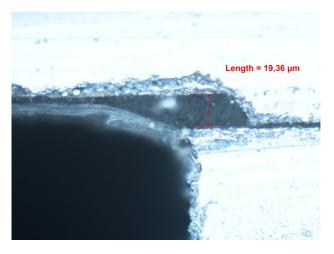

The resonance frequency of the system is estimated with a 2D simulation in COMSOL Multiphysics<sup>©</sup>. Because of symmetry, only 1/4 of the device area can be used allowing for faster computation. In a 2D model a single out-of-plane thickness has to be set for the whole system. To account for different thicknesses for the proof mass and springs, the out-of-plane thickness is set to the spring thickness and material density is redefined in the proof mass to give an equivalent effect as a different thickness. Eigenfrequency studies are set separately for the two in-plane easy axes by choosing appropriate symmetry and antisymmetry boundary conditions. Simulated resonance frequencies range from 201 Hz (long springs with small out-of-plane thickness) to 612 Hz (short springs with large out-of-plane thickness). There is a small difference between the two oscillation directions due to a slightly different oscillating mass (see Figure 2.19). It should be kept in mind that fabrication processes can alter significantly the spring shape, especially by thinning the width of the beams (see Chapter 3). Therefore, lower resonance frequencies are expected in practice.

Simulated values can be compared to theoretical predictions. A single spring is modeled as two cantilever beams in parallel: l is the spring length, t the out-of-plane thickness, and w the width. Then for a load in the l - t plane:

$$k = \frac{Etw^3}{4l^3} \tag{2.53}$$

where E is Young's modulus for the spring material (crystalline silicon). Since one spring is modeled as two cantilever beams in parallel and there are four such springs in parallel for each

| Beam length                 | 1            | 2.9 <i>m</i> m                   |

|-----------------------------|--------------|----------------------------------|

| Beam in-plane width         | W            | $40 \mu m$                       |

| Beam out-of-plane thickness | $\mathbf{t}$ | variable                         |

| Young's modulus for silicon | $\mathbf{E}$ | 170GPa                           |

| Proof mass                  | m            | $5.9 	imes 10^{-5}  \mathrm{Kg}$ |

Table 2.3: Parameters used to solve Eq.(2.54).

Figure 2.20: Simulated resonant frequencies for different out-of-plane beam thickness t

vibration direction, one can write for the resonance frequency:

$$f_o = \frac{1}{2\pi} \sqrt{\frac{k_{eff}}{m}} = \frac{1}{2\pi} \sqrt{\frac{8k_{eff}}{m}}$$

(2.54)

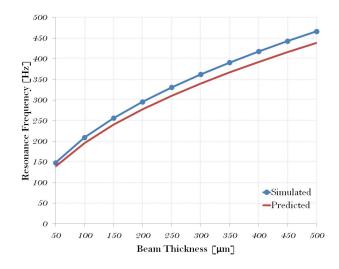

where *m* is the proof mass and  $k_{eff} = 8k$  is the effective spring constant given by 8 cantilever beams in parallel. With the parameters given in Table 2.3, simulated resonant frequencies are plotted in Figure 2.20 for a few values of *t*, together with the  $f_o(t)$  curve predicted by Eq. 2.54. The results are reasonably close and confirm that Eq. 2.53 can be used to predict resonance frequencies as a first approximation. Also the expected relation  $f_o \propto \sqrt{t}$  seems to be confirmed by the simulations.

## 2.5 Coupled Electromechanical System

In this section the mechanical vibration of the proof mass is coupled to the electrical domain, meaning that a new force  $F_{el}$  is added to the mechanical system to account for the work done by the vibration source against the in-plane electrical forces in order to convert vibrational energy into electrical energy. The vibration source motion is assumed to be unaffected by the loss of energy due to harvesting, i.e. its total vibrational power is much higher than the harvested power.

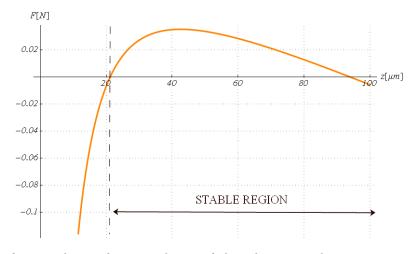

#### 2.5.1 In-Plane Electrical Force Analysis

The work done by the vibration source in the electrical domain can be written in a differential form according to the First Law of Thermodynamics:

$$dW_s = -dU_s = dE_h + dU_{el} \tag{2.55}$$

where  $dU_s$  is the change in internal energy for the source,  $dE_h$  is the *irreversible* energy loss due to dissipation in the load resistance, and  $dU_{el}$  is the *reversible* change in the total electrical energy stored in the device equivalent capacitance.  $dE_h$  is found from the expression of harvested power as

$$dE_h = P_h(t) dt = R \left(\frac{dQ}{dt}\right)^2 dt$$

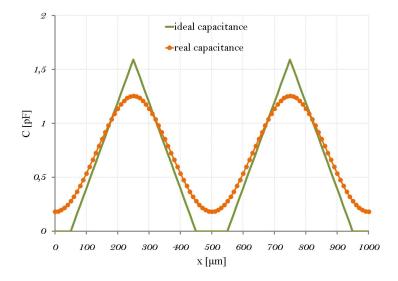

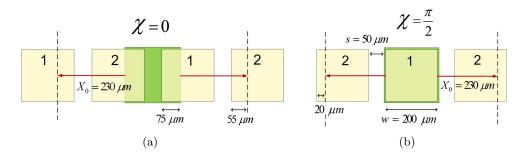

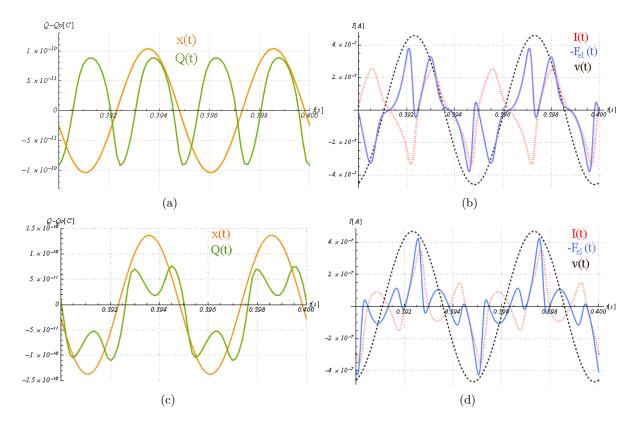

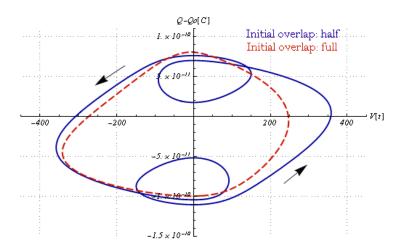

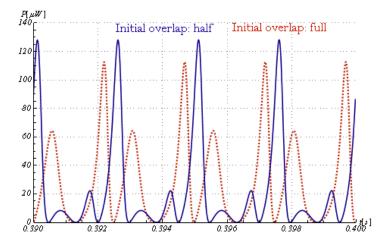

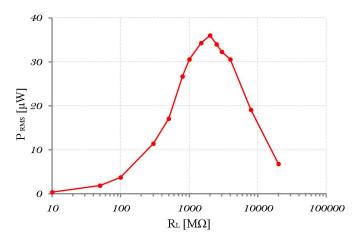

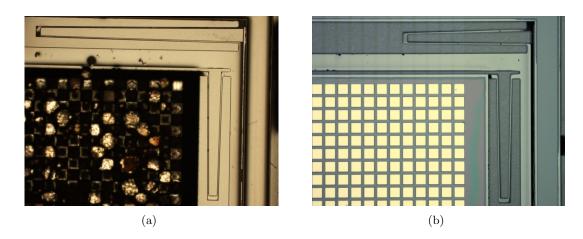

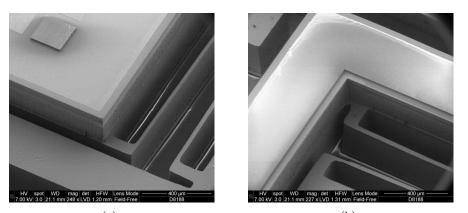

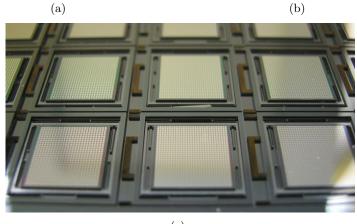

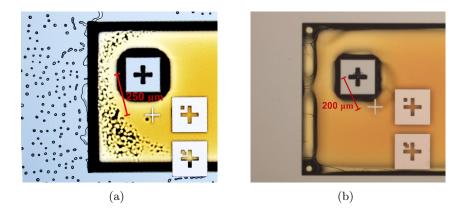

(2.56)