# Politecnico di Milano Dipartimento di Elettronica e Informazione Dottorato di Ricerca in Ingegneria dell'Informazione

# Improving Synchronization and Data Access in Parallel Programming Models

Doctoral Dissertation of:

Ettore Speziale

Advisor:

Prof. Stefano Crespi Reghizzi

Tutor:

Prof.ssa Donatella Sciuto

Supervisor of the Doctoral Program:

Prof.ssa Barbara Pernici

2012 - XXV edition

Politecnico di Milano

Dipartimento di Elettronica e Informazione

Piazza Leonardo da Vinci 32, I-20133 — Milano

# Politecnico di Milano Dipartimento di Elettronica e Informazione Dottorato di Ricerca in Ingegneria dell'Informazione

# Improving Synchronization and Data Access in Parallel Programming Models

Doctoral Dissertation of: **Ettore Speziale**

Advisor:

Prof. Stefano Crespi Reghizzi

Tutor:

Prof.ssa Donatella Sciuto

Supervisor of the Doctoral Program:

Prof.ssa Barbara Pernici

2012 - XXV edition

# **Acknowledgements**

During the last three years I had the opportunity to study and work in the amazing field of parallel programming. What makes this field unique is the mixture of techniques you have to know: you have to know how hardware works, how to compile/analyze/optimize parallel programs, and how to support their execution at run-time. But what makes this three-years long journey incredible was the companions I found along the way.

First of all, I would really like to thank my advisor, Professor Stefano Crespi Reghizzi. Beside the technical stuffs, I really like to thank him for choosing me for some teaching duties, a task that helped improving my poor communication skills. Second, I would like to thank STMicroelectronics, and, in particular, Diego Melpignano for supporting my Ph.D. studies through a scholarship.

I would also like to thank Professor Eduard Ayguadé and Doctor Vicenç Beltran, who hosted me for a long time at Barcelona Supercomputing Center, and all people I meet there. From the same institution, I also thank Professor Rosa Badia, who served as this dissertation reviewer.

Next, let me thank all people I found in the 127 office ad Dipartimento di Elettronica e Informazione.

From the Formal Languages and Compilers Group, I thank Andrea Di Biagio for teaching me a lot of stuffs about coding and compilers. Moreover, I would like to thank him for the work we did together. I thank Michele Tartara for always supporting me with administrative duties and for many brainstorms we did together. I would like to thank Alberto Magni and Michele Scandale, two exceptional coders that share with me some LLVM-related development. Last, I would like to thank Professor Giampaolo Agosta, the old man of the office, for bearing me for such a long time.

I thank members of the Cryptology group, whit whom I shared the office. In particular I would like to to thank Professor Gerardo Pelosi for its advices full of wisdom, and Doctor Alessandro Barenghi for its fools, but extremely funny, advices.

Finally, I would like to thank my parents and all friends who tolerate my delays and misses to some social activities due to last-time duties, often encountered during Ph.D. studies. Among the other, I would like to thank Doctor Martina Maggio and Doctor Guido Salvaneschi for helping me with many communication and administrative duties, and for bearing with me for more than just three years.

# **Sommario**

Oggigiorno le architetture parallele sono il principale mezzo utilizzato per sfruttare il crescente numero di transitori disponibili all'interno dei circuiti integrati. Il cambiamento epocale da architetture ottimizzate per l'esecuzione di programmi sequenziali ad architetture pensate per l'esecuzione di codice parallelo è da imputare alla non sostenibilità delle crescenti richieste di potenza elettrica e dall'inabilità del sottosistema di accesso alla memoria di fornire dati al ritmo richiesto dall'unità di esecuzione centrale. D'altronde, l'utilizzo efficiente di multiple unità di esecuzione parallele non è un compito banale. Infatti, per ottenere dei guadagni prestazionali è spesso necessario ottimizzare attentamente le applicazioni, come dimostrato da anni nel campo del calcolo ad alte prestazioni.

Per mascherare tutta questa complessità, i modelli di programmazione parallela espongono una visione semplificata dell'architettura. Invece di mostrare tutte le singole unità parallele, essi si avvalgono di costrutti di alto livello, come ad esempio i cicli paralleli. La traduzione di questi concetti sulle unità di esecuzione parallele è attuato tramite una combinazione di compilatori ottimizzanti e librerie di supporto progettate per guidare l'esecuzione del programma. Tuttavia, data la disponibilità di un grande e variegato numero di architetture parallele, mascherare i dettagli di basso livello spesso limita le prestazioni, che quindi non sono comparabili con quelle ottenibili attraverso una ottimizzazione manuale.

Lo scopo ti questa tesi è analizzare le inefficienze legate all'utilizzo di unità di esecuzione parallele, ed ottimizzarle tramite tecniche da applicare durante l'esecuzione del programma. In particolare si analizza ed ottimizza, l'esecuzione di riduzioni contestualmente ad una operazione di sincronizzazione tramite barriere. Dopodiché, si mostra come l'utilizzo di tecniche dinamiche permette di sfruttare l'affinità tra dati e computazioni per limitare il più possibile la penalità di accesso alla memoria nel contesto di architetture NUMA, dal punto di vista di due modelli di programmazione parallela: OpenMP e MapReduce. Segue quindi una proposta di utilizzo di tecniche leggere di compilazione dinamica per massimizzare l'utilizzo delle architetture parallele, ed infine si analizza la robustezza ai guasti delle primitive di sincronizzazione primitivi, un meccanismo fondamentale utilizzato da ogni programma parallelo.

# **Abstract**

Today, parallel architectures are the main vector for exploiting available die area. The shift from architectures tuned for sequential programming models to ones optimized for parallel processing follows from the inability of further enhance sequential performance due to power and memory walls. On the other hand, efficient exploitation of parallel computing units looks a hard task. Indeed, to get performance improvements it is necessary to carefully tune applications, as proven by years of High Performance Computing using MPI.

To lower the burden of parallel programming, parallel programming models expose a simplified view of the hardware, by relying on abstract parallel constructs, such as parallel loops or tasks. Mapping of those constructs on parallel processing units is achieved by a mix of optimizing compilers and run-time techniques. However, due to the availability of an huge number of very different parallel architectures, hiding low-level details often prevents performance to be comparable with the one of hand-tuned code.

This dissertation aims at analyzing inefficiencies related to the usage of parallel computing units, and to optimize them from the runtime perspective. In particular, we analyze the optimization of reduction computations when performed together with barrier synchronizations. Moreover, we show how runtime techniques can exploit affinity between data and computations to limit as much as possible the performance penalty hidden in NUMA architectures, both in the OpenMP and MapReduce settings. We then observe how a lightweight JIT compilation approach could enable better exploitation of parallel architectures, and lastly we analyze the resilience to faults induction of synchronization primitives, a basic building block of all parallel programs.

# **Contents**

| Co              | ver      |         |                                                 | i    |  |  |  |  |

|-----------------|----------|---------|-------------------------------------------------|------|--|--|--|--|

|                 | Ackı     | nowledg | ${f generits}$                                  | v    |  |  |  |  |

|                 | Sommario |         |                                                 |      |  |  |  |  |

|                 | Abst     | tract . |                                                 | ix   |  |  |  |  |

|                 | Cont     | tents.  |                                                 | xi   |  |  |  |  |

| List of Figures |          |         |                                                 |      |  |  |  |  |

|                 | List     | of Tabl | es                                              | xvii |  |  |  |  |

| 1               | Intro    | oductio | n                                               | 1    |  |  |  |  |

| 2               | An (     | Overvie | w of Parallel Computing                         | 7    |  |  |  |  |

|                 | 2.1      | Introd  | $\operatorname{uction}$                         | 7    |  |  |  |  |

|                 | 2.2      | The H   | ardware Perspective                             | . 8  |  |  |  |  |

|                 |          | 2.2.1   | Flynn's Taxonomy                                |      |  |  |  |  |

|                 |          | 2.2.2   | Traditional Hardware Performance Improvements . | 9    |  |  |  |  |

|                 |          | 2.2.3   | Dealing with the Power Wall                     | 13   |  |  |  |  |

|                 |          | 2.2.4   | Dealing with the Memory Wall                    |      |  |  |  |  |

|                 |          | 2.2.5   | The Case of GPGPUs-based Architectures          | . 17 |  |  |  |  |

|                 |          | 2.2.6   | Taking into Account the Amdahl's Law            | 20   |  |  |  |  |

|                 | 2.3      | Paralle | el Programming Models                           |      |  |  |  |  |

|                 |          | 2.3.1   | Programming Parallel Architectures              |      |  |  |  |  |

|                 |          | 2.3.2   | Data-parallel Programming Models                | 22   |  |  |  |  |

|                 |          | 2.3.3   | Task-parallel Programming Models                |      |  |  |  |  |

|                 |          | 2.3.4   | Data-flow Parallel Programming Models           |      |  |  |  |  |

|                 |          | 2.3.5   | Task/Data-flow Parallel Programming Models      |      |  |  |  |  |

|                 | 2.4      | Workle  | oad Analysis                                    | 38   |  |  |  |  |

|                 | 2.5      | Conclu  | iding Remarks                                   | 43   |  |  |  |  |

| 3               | Opti     | imizing | Reductions in Shared Memory Multiprocessors     | 45   |  |  |  |  |

|                 | 3.1      | Introd  | $\operatorname{uction}$                         | 45   |  |  |  |  |

|                 | 3.2      | Backgr  | round                                           | 47   |  |  |  |  |

|                 |          | 3.2.1   | Barrier Synchronization                         | 47   |  |  |  |  |

|                 |          | 3.2.2   | Reduction Implementations                       | 48   |  |  |  |  |

|                 |          | 3.2.3   | Atomic Operations                               | 49   |  |  |  |  |

|                 |          |         |                                                 | xi   |  |  |  |  |

# Contents

|   | 3.3  | Combining Barrier and Reduction 5                      | 1          |

|---|------|--------------------------------------------------------|------------|

|   |      | 3.3.1 Tournament Barrier 5                             | 51         |

|   |      | 3.3.2 Basic Reduction Design 5                         | 2          |

|   |      | 3.3.3 Fast Path Optimization 5                         | 5          |

|   |      | 3.3.4 Slow Path Management 5                           | 55         |

|   |      | 3.3.5 Compact Data Representation 5                    | 66         |

|   |      | 3.3.6 Nowait Reductions                                | 8          |

|   | 3.4  | Experimental Evaluation                                | 8          |

|   |      | 3.4.1 Benchmarks                                       | 9          |

|   |      | 3.4.2 GCC Optimization 6                               | 60         |

|   |      | 3.4.3 Experimental Setup 6                             | 0          |

|   |      | 3.4.4 Micro-benchmarks 6                               | 0          |

|   |      | 3.4.5 cg                                               | 51         |

|   |      | 3.4.6 312.swim_m 6                                     | 32         |

|   | 3.5  | Related Work                                           | 32         |

|   | 3.6  | Concluding Remarks 6                                   | 3          |

|   |      |                                                        | _          |

| 4 |      | <b>.</b>                                               | 5          |

|   | 4.1  |                                                        | 55         |

|   | 4.2  | 11                                                     | 66         |

|   |      |                                                        | 7          |

|   | 4.3  | 1                                                      | 9          |

|   |      | 1                                                      | 9          |

|   |      | <del>v</del>                                           | 0          |

|   |      | 0 00                                                   | 2          |

|   | 4.4  | *                                                      | 3          |

|   |      |                                                        | 3          |

|   |      | · ·                                                    | 4          |

|   | , _  | v v                                                    | 6          |

|   | 4.5  |                                                        | 6          |

|   | 4.6  | Concluding Remarks                                     | 7          |

| 5 | Tack | Assignment in Data Intensive Scalable Computing 7      | 9          |

| J | 5.1  |                                                        | <b>'</b> 9 |

|   | 5.2  |                                                        | 31         |

|   | 5.2  | <del>-</del>                                           | 32         |

|   | 0.0  |                                                        | 33         |

|   |      |                                                        | 5<br>5     |

|   |      |                                                        | 55<br>55   |

|   |      | -                                                      | 37         |

|   |      |                                                        | )2         |

|   |      |                                                        | )4         |

|   |      | 5.5.0 Formal Properties of the LADL Task Assignment. 9 | 4          |

## Contents

|    | 5.4     | Simulation Results                                    |     |

|----|---------|-------------------------------------------------------|-----|

|    |         | 5.4.1 Performance Overview                            |     |

|    |         | 5.4.2 Scalability                                     |     |

|    |         | 5.4.3 Sensitivity Analysis                            |     |

|    | 5.5     | Discussion                                            |     |

|    | 5.6     | Related Work                                          | 103 |

|    | 5.7     | Concluding Remarks                                    | 105 |

| 6  | Tow     | vards Runtime Optimization of Parallel Applications   | 107 |

|    | 6.1     | Introduction                                          | 107 |

|    | 6.2     | Related Work                                          | 108 |

|    | 6.3     | Proposed Approach                                     | 109 |

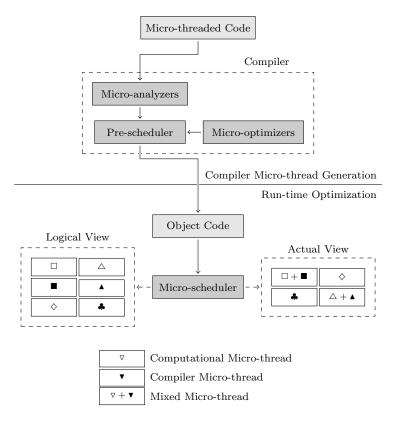

|    |         | 6.3.1 Compilation/Execution Pipeline                  | 111 |

|    |         | 6.3.2 Run-time Optimization                           | 112 |

|    | 6.4     | Foreseen Applications                                 |     |

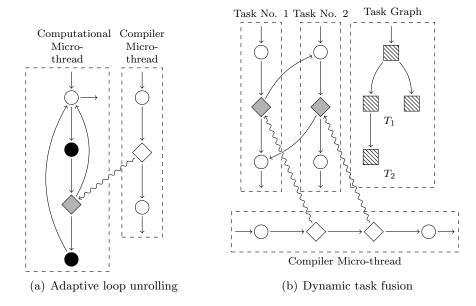

|    |         | 6.4.1 Adaptive Loop Unrolling                         |     |

|    |         | 6.4.2 Dynamic Task Fusion                             |     |

|    | 6.5     | Concluding Remarks                                    |     |

| 7  | Fau     | It Sensitivity Analysis of Synchronization Primitives | 117 |

|    | 7.1     | Introduction                                          |     |

|    | 7.2     | Faults characterization                               |     |

|    | 7.3     | The Methodology Adopted                               | 119 |

|    | 7.4     | Impact of Faults on Synchronization Mechanisms        |     |

|    |         | 7.4.1 Lock-based Critical Sections                    |     |

|    |         | 7.4.2 Transactional Memory-based Critical Sections    | 124 |

|    |         | 7.4.3 Transactional Locking-based Critical Sections   |     |

|    |         | 7.4.4 Results of the Experimental Campaign            |     |

|    | 7.5     | Concluding Remarks                                    |     |

| 8  | Con     | cluding Remarks                                       | 133 |

| Ri | hliog   | raphy                                                 | 137 |

| וט | billogi | i aprily                                              | 131 |

# **List of Figures**

| 2.1                                                                              | Interactions of Architectures with Instructions and Data .                                                                                                                                                                                                                                                                                         | . 10                                                                 |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 2.2                                                                              | String Copy on CISC and RISC Architectures                                                                                                                                                                                                                                                                                                         | . 12                                                                 |

| 2.3                                                                              | Transistor Integration                                                                                                                                                                                                                                                                                                                             | . 13                                                                 |

| 2.4                                                                              | General Purpose Processors Evolution                                                                                                                                                                                                                                                                                                               | . 14                                                                 |

| 2.5                                                                              | An Example of UMA Architecture                                                                                                                                                                                                                                                                                                                     |                                                                      |

| 2.6                                                                              | An Example of NUMA Architecture                                                                                                                                                                                                                                                                                                                    | . 18                                                                 |

| 2.7                                                                              | Heterogeneous Computing with GPGPUs                                                                                                                                                                                                                                                                                                                |                                                                      |

| 2.8                                                                              | Plot of the Amdhal's Law                                                                                                                                                                                                                                                                                                                           | . 19                                                                 |

| 2.9                                                                              | Sequential SAXPY                                                                                                                                                                                                                                                                                                                                   | . 23                                                                 |

| 2.10                                                                             | 1                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

| 2.11                                                                             | OpenMP SAXPY                                                                                                                                                                                                                                                                                                                                       | . 26                                                                 |

| 2.12                                                                             | Sequential SDOT                                                                                                                                                                                                                                                                                                                                    | . 28                                                                 |

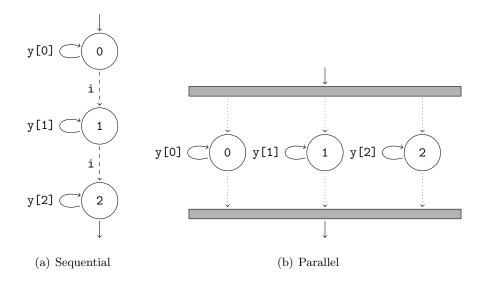

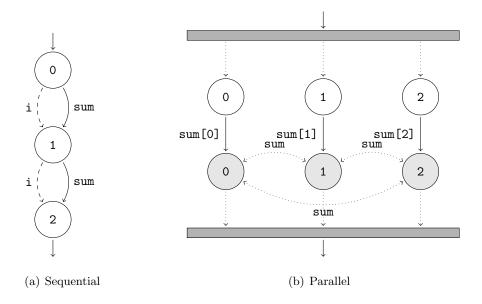

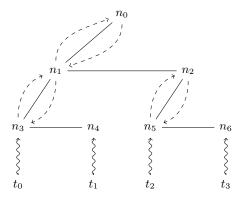

|                                                                                  | Sequential and Parallel Execution of SDOT                                                                                                                                                                                                                                                                                                          |                                                                      |

| 2.14                                                                             | OpenMP SDOT                                                                                                                                                                                                                                                                                                                                        | . 29                                                                 |

|                                                                                  | Cilk Sort                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| 2.16                                                                             | StreamIt Low Pass Filter                                                                                                                                                                                                                                                                                                                           | . 34                                                                 |

| 2.17                                                                             | StarSs Cholesky Decomposition                                                                                                                                                                                                                                                                                                                      | . 37                                                                 |

| 3.1                                                                              | Serialized Reduction Example                                                                                                                                                                                                                                                                                                                       | . 48                                                                 |

| 0.1                                                                              | Scriding a record colon bilanipie                                                                                                                                                                                                                                                                                                                  | . 40                                                                 |

| 3.2                                                                              |                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

|                                                                                  | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49                                                                   |

| 3.2                                                                              |                                                                                                                                                                                                                                                                                                                                                    | 49                                                                   |

| 3.2<br>3.3                                                                       | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | . 49<br>. 50<br>. 51                                                 |

| 3.2<br>3.3<br>3.4                                                                | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53                                                 |

| 3.2<br>3.3<br>3.4<br>3.5                                                         | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>54                                           |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                  | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>54<br>56                                     |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                           | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>54<br>56                                     |

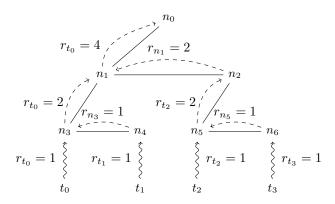

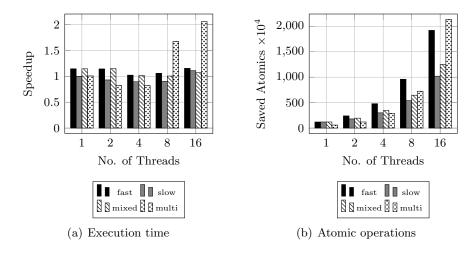

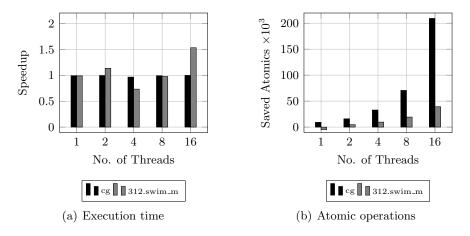

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                             | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>54<br>56<br>61                               |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                             | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>54<br>56<br>61<br>62                         |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>4.1<br>4.2               | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>54<br>56<br>61<br>62<br>67                   |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                             | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>54<br>56<br>61<br>62<br>67                   |

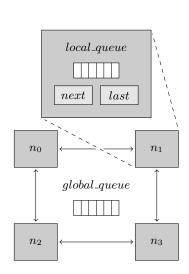

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>4.1<br>4.2<br>4.3<br>4.4 | Parallelized Reduction Example Hand-written Reduction Execution of the Tournament Barrier Algorithm Layout of the Container Type An Example of Reduction Path Management Algorithm Reduction Micro-benchmarks Results Reduction Benchmarks Results Pattern Clause Syntax Pattern Example NUMA-aware OpenMP Runtime Runtime Behaviour of a Sub-team | 49<br>50<br>51<br>53<br>54<br>56<br>61<br>62<br>67<br>68<br>71       |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>4.1<br>4.2<br>4.3        | Parallelized Reduction Example                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>54<br>56<br>61<br>62<br>67<br>68<br>71<br>88 |

# List of Figures

| 5.3        | Remote Tasks Assignment                                                      |

|------------|------------------------------------------------------------------------------|

| 5.4        | Less Loaded Servers Assignment                                               |

| 5.5        | An Example of Data Placement                                                 |

| 5.6        | Round-robin and Flow-based Assignments 93                                    |

| 5.7        | Locality Aware & Bounded Latency Task Assignments $93$                       |

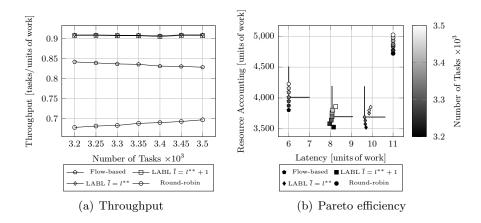

| 5.8        | Performance of Analyzed Algorithms 99                                        |

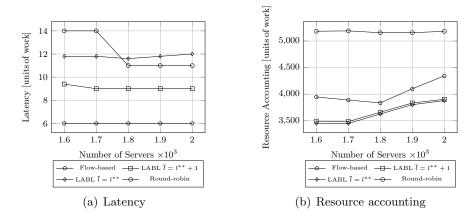

| 5.9        | Scalability of the Analyzed Algorithms 100                                   |

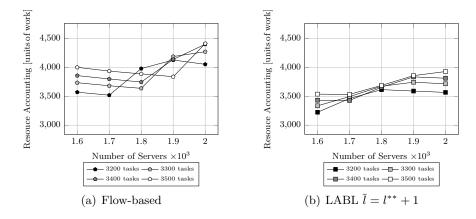

| 5.10       | Resource Awareness of Analyzed Algorithms 101                                |

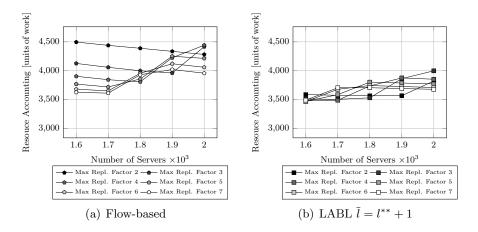

| 5.11       | Replication Factor Sensitivity of Analyzed Algorithms $$ $101$               |

| 6.1<br>6.2 | Proposed Dynamic Compilation/Execution Pipeline 111<br>Foreseen Applications |

| 7.1        | Lock-protected Shared Counter Update                                         |

| 7.2        | Shared Counter Updates Through Transactional Memory 122                      |

| 7.3        | Implementation of LockAcquire                                                |

| 7.4        | Implementation of LockRelease                                                |

| 7.5        | Transactional Memory-based Atomic Exchange $\ \ldots \ \ldots \ 126$         |

| 7.6        | Transactional Memory-based Lock Release                                      |

| 7.7        | Fault Description Example                                                    |

| 7.8        | Effects of Fault Injections                                                  |

|            |                                                                              |

# **List of Tables**

| 2.1 | Flynn's Taxonomy of Computer Architectures      |  | 1(  |

|-----|-------------------------------------------------|--|-----|

| 2.2 | HPC Dwarfs and their Descriptions – Part I      |  | 40  |

| 2.3 | HPC Dwarfs and their Descriptions – Part II     |  | 41  |

| 2.4 | New Dwarfs and their Descriptions               |  | 42  |

| 3.1 | Reduction Benchmark Characterization            |  | 59  |

| 4.1 | OpenMP Benchmarks Characterization              |  | 73  |

| 4.2 | OpenMP Benchmarks Runtime Behavior              |  | 74  |

| 4.3 | OpenMP Benchmarks Speedups                      |  | 75  |

| 4.4 | OpenMP Benchmarks Remote Accesses (in Millions) |  | 76  |

| 7.1 | Fault Sensitivity Analysis Benchmarks           |  | 127 |

|     | Results of Fault Injection on Benchmarks        |  |     |

# 1 Introduction

The switch to parallel general purpose computing is one of the most challenging steps in the history of computer science. Indeed, before 2005, parallelism was mainly exploited at the hardware level, while most of the programming models were based on the abstraction of a single execution flow. Parallel programming was relegated highly specialized application fields, such as High Performance Computing or Internet daemons.

Nowadays, the parallel nature of the hardware is fully exposed to programmers, hence improving performance of applications cannot be resolved by simply upgrading to a newest processor: the major change between two successive generation of processors is not the performance of the single execution unit, but the number of execution units. Thus, a greater number of resources is available, and programmers must correctly exploit them to increase application performance.

Different factors have led to this change in the architecture evolution trend. First of all, exposing a sequential programming model while guaranteeing excellent performance requires to automatically identify independent instructions in the input programs and to map them onto parallel hardware resources. Super-scalar processors perform this operation at run-time, exploiting aggressive *Instruction Level Parallelism* techniques in order to keep the pipeline as full as possible. Combining this with very short pipeline stages allows to boost the core operating frequency, and thus the number of completed instructions per clock cycle. However, these techniques rely on the ability to *detect* parallelism at run-time, which is definitely not an easy task [147]. Moreover, relevant power budgets are necessary [30], and the memory subsystem technologies must be in par with processing units technologies in order to fulfill data requests, which is not the case [150].

From the compiler perspective, exploitation of parallel hardware can be seen as optimization of sequential applications: the compiler is in charge of detecting parallel components in the application, and mapping them onto different processing elements. Due to the limited knowledge of source code achievable by automatic compiler-based analyses, these techniques – e.g. Decoupled SoftWare Pipelining [114] – cannot fully exploit all available parallel processing units, thus programming models exposing the true parallel nature of the hardware look better for achiev-

ing maximum performance, as proved by MPI [103] in the domain of large scale HPC applications.

On the other hand, exposing parallel resources to the programmer implies charging him with more responsibilities. For instance, when using the MPI library a programmer must both organize communication between the different processing units, and distribute data across them. To reduce the burden of parallel programming, different programming models focus on hiding these aspects behind high-level constructs, such as *parallel loops*. The compiler, eventually assisted by a runtime, is then in charge of mapping parallel constructs over the available processing units.

A parallel programming model is often based on one of the following parallel computing idioms: i) data-parallelism; ii) task-parallelism; iii) data-flow parallelism. Each of them is specialized in handling a different kind of parallelism.

Data-parallel programming models support regular applications, such as HPC codes. That code is characterized by computing a value out of a set of input matrices. Usually, inputs are analyzed by a means of a loop which iterations are almost independent. Programmers identify such loops, and tell the compiler that their iterations can be scheduled in parallel. Synchronization inside loop iterations is up to programmers. OpenMP [16] mainly supports parallel loops in the context of shared memory machines. However, since in modern machines the memory access cost is not uniform across different processing units, Partitioned Global Address Space languages, like Unified Parallel C [143] and Chapel [44] have been introduced. Together with the identification of parallel loops, they allow programmers specifying how matrices should be distributed across available processing units. This extra information allows the compiler to schedule iterations in order to minimize the cost of accessing the memory. A special case of data-parallelism is represented by languages targeting GPGPUs, like CUDA [6] and OpenCL [87], that allow fine tuning of parallel loop iterations in order to maximize performance. On the other hand, portability is achieved only at the language level, and little changes in the target architecture can exhibit very different performance. Moreover, full exploitation of GPGPUs resources requires non trivial programming efforts.

Task-parallel programming models focus on extracting as many as possible parallelism from applications that do not exhibits a regular behaviour. Indeed, there are no parallel loops to identify. Rather than, at some point, the application spawns independent computations. They are identified by programmers, and called *tasks*. Since at compile-time parallel computations cannot be identified, this approach completely

relies on efficient run-time techniques to manage task lifetimes. Cilk [56] is the best known task-parallel language.

Finally, by specializing the language for a specific application domain, it is possible to completely hide parallelism to programmers. For instance, in the context of signal processing, data-flow programming models allow expressing applications by a means of graphs. Each node represents a small computation, often a filter application. Each arc is labelled with two labels: the label at the source node represents the number of resources produced by running the computation related to the source node, while the label at the target node represents the number of resources needed to trigger the execution of the target node computation. The compiler analyzes the data-flow graph and builds a schedule, which steady state can be run in a lock-step fashion by means of multiple processing units. StreamIt [62] is the best known data-flow language.

#### Thesis Contribution

The main goal of this dissertation is to analyze performance problems hidden in explicit parallel programming models, and optimize them to enable full exploitation of parallel processing units.

**Dealing with Synchronization Primitives** Embarrassing parallel applications allow efficient parallelization because the work can be partitioned into independent sections, that can be executed without any synchronization by available parallel processing units. However, this kind of application is not very common. Indeed, if multiple processing units contribute in computing something, they must coordinate through synchronization primitives.

In the HPC setting, synchronization is mainly achieved through the barrier primitive. Due to its large usage, efficient algorithms have been developed [72] to limit as much as possible the bottleneck it introduces in parallel computations. A barrier synchronization is often associated with the computation of an aggregate value – reduction. This results in introducing two bottlenecks in the parallel computation, one due to the barrier synchronization, and the other due to reduction computation.

The barrier execution can be seen as an opportunity to optimize reduction computation. Indeed, Chapter 3 shows how reduction computation can be performed together with the execution of the barrier algorithm, hence paying synchronization cost once. Results of this work have been published in [134].

As a side note, incorrect usage of synchronization primitives is known to be one of the most common error in concurrent, and thus parallel, programming. Moreover, silicon technologies have reached the point where *soft faults* can happens also inside the integrated circuit rather than only at its boundaries [43], so a key question is how faults insisting on hardware related to the execution of synchronization primitives influence parallel computations. Chapter 7 investigates the problem, by analyzing the robustness to faults of critical sections, either protected by means of mutexes of by exploiting hardware transactional memory. Results of this work have been published in [64].

Efficient Data Access Many parallel architectures include memory subsystems that exhibit different performance depending on which processing unit is requesting the data. Thus, loads and stores must be carefully organized to avoid incurring in expensive accesses. Traditional approaches – e.g. PGAS languages [14, 44, 128, 143] – distribute data structures across the memory subsystems, and then schedule computations to maximize data locality according with the selected distribution.

However, this implies programmers must take into account the distribution of data across available processing units. Chapter 4 faces the problem from a different perspective. Instead of specifying how data structures must be distributed, programmers specify the expect access pattern to the data. This information is exploited by a customized OpenMP runtime to schedule parallel loop iterations on processing units where the expected memory access penalty is minimized. Results of this work have been published in [25].

Efficient data access is also a relevant feature when considering the cost, in term of needed resources, to perform a memory access. In the setting of *Data Intensive Scalable Computing*, tasks access data which is potentially spread across an entire cluster of commodity machines. Executing tasks on machine with no local copy of input data results on accessing disks on a remote machine, thus the resource usage is increased, both in terms of energy requirements, and of network bandwidth.

Chapter 5 introduces a task assignment algorithm that takes into consideration resource usage as well. Given a DISC job, modelled as a set of independent tasks, it keeps under control consumed resources by means of a latency threshold. Indeed, assignments involving expensive data accesses are considered only up to the latency threshold. If the latency goal is not satisfied – e.g. no assignment can be found – consuming more resources does not allow to achieve good latency performance, hence the algorithm assigns left tasks by containing resource consumption.

**Runtime Optimization** A key feature of parallel computing is the lack of a reference architecture. Indeed, with respect to architectures designed to support sequential programming models, explicitly parallel hardware is shipped with a higher number of configurations. This prevent the construction of an exact model of the target architecture, which in turns limits aggressive compiler optimizations.

To offset such problems, some programming models exploit a *Just-In-Time* compiler to delay final code emission just before the application is run. For instance, in CUDA [6] code intended to be run on GPGPU is distributed in form of a byte-code language, while in OpenCL [87] kernel source codes is distributed together with the application.

However, using a JIT compiler incurs in relevant performance penalties, both in terms of raw performance and from the resource usage perspective. Chapter 6 proposes the design of a compilation pipeline that splits the optimization duty between compile-time and run-time. At compile-time, code should be analyzed and code sections suitable for run-time optimization must be detected. Then, instead of employing code specialization, the compiler emits code to apply the optimization at run-time. This should avoid using a full-fledged JIT compiler, while keeping some of its features. This work was initially introduced in [52].

#### **Thesis Structure**

The rest of this dissertation is organized as follow. Chapter 2 introduces the world of parallel computing, from both the hardware, software, and workload perspectives. Chapter 3 describes the optimization of reductions by means of a special barrier synchronization primitive. Chapter 4 deals with the problem of locality-aware scheduling of OpenMP parallel loop iterations, while Chapter 5 focuses on efficient task assignment in the DISC setting. Chapter 6 introduces a proposal for a lightweight JIT optimization pipeline, and Chapter 7 analyzes the robustness of synchronization primitives to faults. Finally, Chapter 8 concludes.

# 2 An Overview of Parallel Computing

Today, multi-core technologies are the main vector to increase performance of computer architectures. The shift from sequential to parallel processing has been enforced by physical limits, such as high power budgets and the inability of the memory subsystem to feed high-speed CPUs, which prevent efficient improvements of sequential performance. However, dealing with multi-core architectures is harder than programming single-core architectures, due to the exposure of the parallel hardware to programmers. In this chapter we propose a brief survey about parallel architectures, parallel programming models, and workloads expected to be run on multi-core machines.

## 2.1 Introduction

After decades of performance improvement guaranteed by boosting single-core capabilities, the computer science discipline has to find alternative ways to continue increasing performance. Indeed, semiconductors physical limits, disparity between improvements in core and memory subsystems, and increased power requests have been identified as the main factors preventing performance improvement of single-core architectures.

An alternative way was found in the context of *multi-core* architectures. Instead of providing architectures built around the concept of a single, powerful core, starting around 2005 architecture designers started providing processors composed by multiple simpler cores. With respect to previous solutions, the performance of the single core is lower, but due to Moore's law effects, the available transistors allow to pack more than one core per die, thus the overall performance of the processor – as a collection of cores – is increased.

However, with respect to single-core technologies, programming multicore architectures has to face with a wider range of problems. For instance, there is no an unique reference model, hence for each kind of architecture, different programming models and best practices must be employed. Moreover, it is not guaranteed that every algorithm can be efficiently parallelized – the parallel versions cannot scale, or even worst, the sequential version is more efficient.

Nowadays, parallel processing is a very diversified realm. To correctly exploit the available resources, programmers must be aware of the available parallel architectures. They also need to know the different parallel programming models, and how each application can benefit from parallel hardware. This allow to pursuit the most suitable parallelization strategy, to select the most appropriate programming model, and to target the most suitable architecture.

The rest of this chapter is organized as follow. Section 2.2 deals with parallel computing from the hardware perspective, while Section 2.3 introduces the best known programming models and languages for parallel computing. Section 2.4 briefly depicts the workload expected to be run by parallel hardware. Finally, Section 2.5 concludes.

## 2.2 The Hardware Perspective

During the entire life of Computer Science as a discipline, hardware has driven the evolution of languages, programming models and software architectures. Hardware has been continuously improved in order to allow programs to run faster.

Language and programming models are built on top of hardware, hence in order to achieve good performance it is needed to select the right language and programming model for each hardware device. The choice must be taken considering hardware features, so, due to the huge amount of available devices, a taxonomy is required to model relevant hardware features.

### 2.2.1 Flynn's Taxonomy

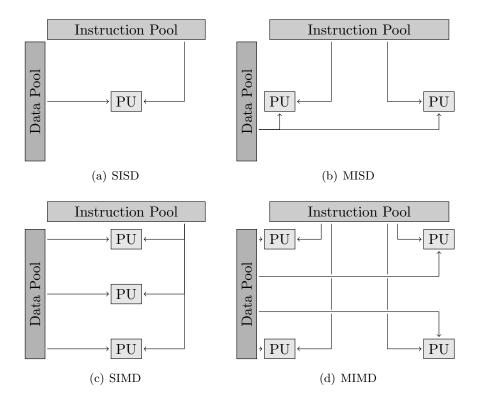

Hardware can be classified considering its elementary building blocks. In the Flynn's taxonomy [54] each hardware device is modelled as a set of *processing units*, in charge of executing program instructions fetched from an *instruction pool* by means of *instruction streams*. Data is stored in a *data pool*, accessed through *data streams*.

Classification is performed considering the number of processing units, and how they are connected to the instruction pool and to the data pool.

**Single Instruction Single Data** The architecture is composed by a single processing unit. There is a single data stream feeding the processing unit. This kind of architecture dominates the general purpose market

up to year 2005. Today, it is used as a base building block for designing large multi-core machines, and it is still used in applications were raw computational capabilities is not a strict requisite, such as embedded micro-controllers. A single core desktop processor, like the Intel Pentium, is a representative of this class.

Single Instruction Multiple Data The architecture is composed by multiple processing units. Every processing unit executes the same instruction, but data is fetched from different streams. Vector processors, equipped with vector functional units able to apply the same operation over large arrays, was among the firsts members of this class. Today, GPGPUs multi-processors are the last instances of this class. Indeed, each multi-processor is actually composed by multiple highly-coupled processing units. Each of them executes the same instruction, while referencing a different set of memory locations.

Multiple Instruction Multiple Data The architecture is composed by multiple independent processing units. Each of them executes different instructions, coming from different streams. Data needed by each instruction is fetched from different streams. Modern multi-core processors fall into this category. Indeed, each core is completely independent from the other, and thus it can execute whichever instruction it wants, working on a private data stream.

Multiple Instruction Single Data The architecture is composed by multiple processing units, executing different instructions working on the same data. This class has been defined for symmetry purposes, so finding a representative is not trivial. However, systolic arrays can be interpreted as MISD architectures.

Table 2.1 summarize Flynn's taxonomy, while Figure 2.1 gives a graphical representation of how different Flynn's classes access to instruction and data. All architecture classes must access to both instructions and data, respectively represented by *Instruction Pool* and *Data Pool*. Access is performed by means of streams, represented by arrows connecting processing units to pools.

#### 2.2.2 Traditional Hardware Performance Improvements

Up to 2005, the majority of general-purpose architectures were SISD, thus computer architects focused on efficiently supporting sequential applications.

| Table 2.1: Flynn's taxonomy of computer a | er architectures |

|-------------------------------------------|------------------|

|-------------------------------------------|------------------|

|                  | Single<br>Instruction | Multiple<br>Instruction |

|------------------|-----------------------|-------------------------|

| Single<br>Data   | SISD                  | MISD                    |

| Multiple<br>Data | SIMD                  | MIMD                    |

Figure 2.1: Interactions of Flynn's taxonomy classes with instruction and data. The fundamental building-block is the processing unit. Classification is based on how processing units access data and instructions through streams

Improvement of sequential performance was initially achieved through extending the architecture in order to implement in hardware some heavily-used functionalities. This in turn fostered the diffusion of *Complex Instruction Set Computing* architectures, which became the dominant ones in the '60 and '70. Typical characteristic of CISC architectures are specialized instructions for handling string operations and complex memory addressing modes.

The key idea of CISC architectures is to improve program performance by reducing the overall latency of groups of instructions. This approach is inherently limited. Indeed complex instructions require complex hardware, so the critical path in their implementations represents a limit – more complex instructions requires longer critical paths.

For this reason, starting from the mid '70, computer architects focused on improving the *throughput* of completed instructions – the *Instructions Per Cycle*. An improvement of the *IPC* directly influences the improvements of a section of code. Indeed, the *Cycles Per Instruction*, CPI = 1/IPC is inversely proportional to the instruction completion throughput.

To achieve this goal Reduced Instruction Set Computing architectures split the execution of a single instruction into stages. Stages are connected through a pipeline. Instructions are issued by the first stage and committed by the last. At each clock cycle, the architecture executes all stages of the pipeline in parallel, thus the clock cycle is determined by the latency of the slowest stage. The latency of an instruction is the latency of the pipeline, but instruction throughput is increased because an instruction is completed at every clock cycle.

In this schema, RISC architectures exploit parallelism between instructions in a single execution flow –  $Instruction\ Level\ Parallelism$  – to execute them in parallel, while still exposing a sequential programming model. Semiconductor technology improvements can be effectively exploited by RISC architectures. Indeed, new technologies allow increasing the clock frequency, thus decreasing the CPI.

RISC architectures can guarantee performance as long as they can keep the pipeline busy, that is at every clock cycle an instruction must be issued to the pipeline. If this is not possible, a bubble is inserted into the pipeline, and the overall efficiency is decreased. This behaviour is due to *hazards* induced by the instruction stream. A *control hazard* is generated when the pipeline stalls because the address of the next instruction is not yet ready. A *data hazard* arises when data needed by an instruction is not available. A *structural hazard* is due to the lack of hardware resources for executing the instruction.

In order to keep the pipeline busy, aggressive optimization techniques

```

cld

mov r8,#0x400

1

$src, %esi

movl

2 loop_header:

2

$dst,%edi

r8, r8, #0x1

3

movl

movl

$0x400, %ecx

4

ldrb

r9,[#src,r8]

4

strb

r9,[#dst,r8]

rep

movsb

r8,loop_header

cbnz

(a) X86 string copy

(b) ARM string copy

```

Figure 2.2: Trivial implementation of string copy on a CISC architecture (Figure 2.2(a)) and on a RISC architecture (Figure 2.2(b)). The CISC variant employs specialized instructions, while in the RISC case an explicit copy loop must be used

have been implemented along the years: pipeline forwarding, out-oforder execution [141], branch prediction [151], .... In order to increase performance, instructions have been split into a large number of short stages, thus allowing to boost clock frequency.

Example 2.1. Figure 2.2(a) shows the implementation of a 1024-elements string copy in a CISC architecture, the Intel x86 [80]. First, the direction flag is reset (Line 1) so that subsequents instructions assume strings are visited in ascending order, from the first character to the last. Then, the base pointers of the two arrays are loaded into registers %esi (Line 2) and %edi (Line 3), while, the number of elements to copy is written into register %ecx (Line 4). The movsb instruction (Line 6) copies the content of the memory cell referenced by %esi into the memory pointed by %edi, then it increments the two registers. The rep prefix (Line 5) instructs the hardware to execute movsb and to decrement the content of register %ecx until it reaches 0, thus it allows to copy the whole \$src array into the \$dst array.

Example 2.2. Figure 2.2(b) reports the implementation of a 1024-elements string copy in a RISC architecture, the ARM [17]. The instruction set is not rich as in a CISC architecture, thus an explicit loop with 1024 iterations is needed in order to copy each element from the #src array into the #dst array. The first instruction of the loop body decrements the induction variable, stored inside register r8 (Line 3). Then, in order to copy one element, it is necessary to load it from memory to a temporary register (Line 4), and to perform a store (Line 5). Finally, a cbnz is executed in order to check whether there are no more iterations to execute (Line 6).

RISC architecture concepts was the driving force of computer architecture evolution up to year 2005. They was also integrated into popular

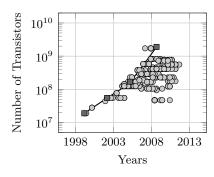

- (a) Number of transistors vs years

- (b) Core frequency vs years

Figure 2.3: Transistor integration. Figure 2.3(a) reports the variation of the number of transistors along the years. Reducing transistor size allows to boost the switching frequency, and thus the core operating frequency. This behaviour becomes unsustainable past year 2005 (Figure 2.3(b)), where power requirements becomes too large. Data from Intel [3]

CISC design – internally an Intel x86 core is a RISC architecture. At that time, limits of ILP [147] becomes unsurmountable walls. Mechanism needed to keep the pipeline busy require a lot of power. Moreover, increasing the clock frequency directly increases the dynamic power consumed by the architecture. This problem is generally identified with the term *power wall* [30].

Apart of the power requirements, another problem of aggressive RISC architectures is that they primarily focus on the processor. Data hazards due to memory accesses are indirectly tackled through cache hierarchies <sup>1</sup>, but the problem of feeding the processor with data still persists. The inability of the memory hierarchy to fulfill the data requests by the processor is identified with the term memory wall [150].

#### 2.2.3 Dealing with the Power Wall

Figure 2.3(a) plots the number of transistors employed by Intel processors from 1999 to 2012 [3]. It is clear that the Moore's law is still in effect, indeed the number of transistors per die continually increases.

Looking at Figure 2.3(b) we can observe that the increased transistor density has been primarily exploited to boost the core operating frequency. However, as discussed before, increasing the switching frequency of a transistor directly influences the amount of required dynamic power. For CMOS technology, it is ruled by the following relation:

<sup>&</sup>lt;sup>1</sup>Another power-hungry component

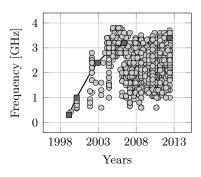

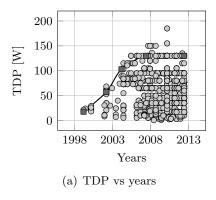

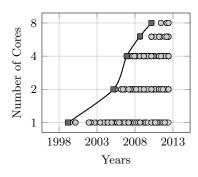

(b) Number of cores vs years

Figure 2.4: General purpose processors evolution. Increasing frequency to improve performance leads to power-hungry designs (Figure 2.4(a)). Acting on the number of available cores (Figure 2.4(b)) allows to contains power requirements. Data from Intel [3]

$$P_{dyn} \sim \frac{1}{2} \times C \times V^2 \times f$$

where C is the driven capacitive load, V is the working voltage and f is the switching frequency. Since C is a function of the number of transistors connected to the output and of the technology, the tunable parameters are V and f. In order to limit the consumed power while, at the same time, increasing the switching frequency, the working voltage has been progressively dropped from 5V to just under 1V.

Past year 2005, the frequency of the cores did not further increase, due to the inability of exploiting ILP and of the huge power requests. The connection between frequency and power can be easily seen in Figure 2.4(a), which plots the *Thermal Design Power* of Intel processors from 1999 to 2012 [3]. The TDP growth stops at the same time of core frequency.

To contain power requests, architecture designers removed powerhungry components required by aggressive ILP techniques. With respect to processors of the ILP-era, these new processors have shorter pipelines, a narrow instruction issue window, and static scheduling instead of dynamic scheduling. Sometimes, in-order execution is preferred to out-of-order execution.

However, relying on simpler processors do not necessarily mean that we cannot execute more complex applications. Indeed, for many duties, these processors allow to execute a wide range of applications, without any performance penalty. At the same time, simple designs allow to better accommodate emerging performance indicators, such as power consumption.

On the other hand, for some applications raw performance is an essential requisite. For instance, given a time budget, HPC applications need faster processors in order to perform more accurate simulations. Another example is related to graphic-intense applications, who aim at improving the user experience quality year after year.

To provide raw performance for such kind of applications, mechanism other than ILP should be exploited. In the general purpose CPUs market, past 1995 architecture designers started the trend of exposing parallel features to the programmer. For example, the concept of *vector* instructions has been borrowed from vector processors [127] and adapted to general purpose CPUs, leading to vector instruction set extensions [50, 118].

The exposure of hardware parallel feature to the programmer reached a critical point around 2005. Indeed, vector instruction sets just introduced new data types and instructions, thus available parallelism can be efficiently masked by well-written libraries. In order to get more performance, parallelism must be exploited in a more explicit way.

Initially, Symmetric Multi Threading (e.g. Intel Hyper-treading [101]) designs allowed to execute more than one independent execution flow on the same core. Stalls due to hazards in one execution flow are used to execute another execution flow. The natural evolution of this approach is Symmetric Multi Processing, where the architecture exposes multiple independent processing elements. This technique, initially exploited at multiple package level – i.e. installing more than one single-core processor on the same motherboard –, has been widely applied at the single package level – i.e. putting more than one core on the same die – starting from 2005.

Figure 2.4(b) reports the number of cores per Intel processors starting from 1999 up to 2012 [3]. Comparing it with Figure 2.3(a), it is clear that past 2005, increasing the number of cores became the primary way to exploit available transistors.

The modus operandi of architecture designers is clear. First, build a simple architecture to contain power requirements, then replicate the design multiple times to guarantee performance. This methodology leads to architectures that can be classified as MIMD in Flynn's taxonomy.

## 2.2.4 Dealing with the Memory Wall

The problem of feeding a processor with data is orthogonal to the power problem, however the same techniques used to cope with the power wall can also be useful for fighting the memory wall.

On SISD machines there is an unique path for accessing the main memory – all accesses must pass through the *memory controller*. It is on charge of serializing all memory accesses. The primary measure of its efficiency is the *bandwidth*, that is the number of bytes it can transfer from/to the memory per second.

Along the years, the memory controller has been integrated with the processor, and they start sharing the same die. It works closely with the cache hierarchy, and, together, they are responsible for ensuring *memory consistency* [12].

Vectorial instruction set extensions usually provide instructions accessing memory with a relaxed consistency. This allows super-scalar out-of-order processors to perform a more aggressive instruction reordering and to skip the cache hierarchy while accessing memory needed for that kind of instructions. The net result is an increased bandwidth for vector-related instructions.

Due to memory consistency and caching constraints, memory accesses generated by non-vector instructions cannot use this fast-path to the memory. Considering that the memory access latency and bandwidth do not evolve like the performance of the core, it is clear that the memory controller quickly becomes a bottleneck. Moreover, past 2005, the increasing number of cores per die imposes a further load on the memory controller. Indeed, instead of feeding one core, the memory controller now has to provide data for all cores in the die.

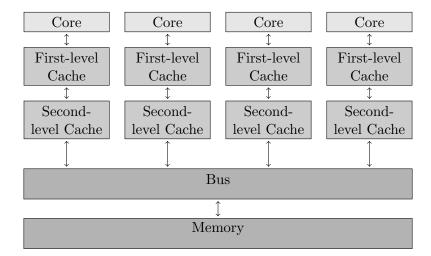

Regardless of the number of cores, architectures where the memory access latency is constant among all processors are called *Uniform Memory Access* architectures. Figure 2.5 reports an example of a 4-core UMA architecture. Each core has a private cache hierarchy, thus as long as memory requests can be fulfilled by caches, each core can perform accesses independently.

When an access to the main memory is generated, regardless of the originating core, it must be handled by the memory controller. This is usually implemented using a simple design, such as a shared bus.

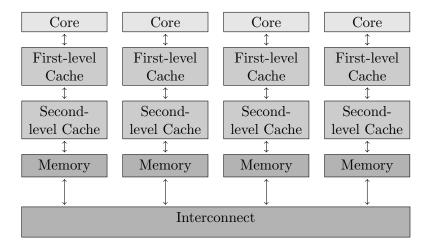

To remove the bottleneck, the number of paths to access the memory must be incremented. That is, each core must be equipped with a private memory controller, directly connected to a different memory module. Accesses to that module are called *local accesses*. When a core has to access to a memory module different from the local one, it performs a *remote access*. In that case, the access must be performed by mean of the memory controller of another core, thus with respect to a local access, the latency is greater. On the other hand, the overall bandwidth is increased.

Figure 2.5: An example of UMA architecture. The latency of an access to main memory is constant across all cores. This is due to the availability of an unique path for accessing the main memory

Such kind of architectures, where the memory access latency depends on the core originating the access and on the accessed memory module are called *Non Uniform Memory Access* architectures. The core, the cache hierarchy, the memory controller, and the local memory module constitute a *node*. Communication between nodes is ensured by an *interconnect network*.

Figure 2.6 reports an example of NUMA architecture composed by four nodes, each composed by one core with a two-level private cache hierarchy.

UMA designs are still used in small multi-core architectures. When the number of available cores becomes greater than eight, NUMA designs becomes more attractive. Usually, a hybrid solution is adopted. For instance, consider an architecture composed by four interconnected processors. Each processor is equipped with four cores and is attached to a local memory module. Such an architecture has NUMA characteristics between the four processors, and UMA characteristics inside the single processor.

#### 2.2.5 The Case of GPGPUs-based Architectures

Up to the end of the last millennium, graphics boards were in charge of handling output to the screen. The actual computation of what to display was performed on the CPU, with little assistance from the graphics

Figure 2.6: An example of NUMA architecture. The latency of an access to main memory is a function of the core where the access occurs and of the physical location of the accessed address. This is due to the need to walk the interconnect network when accessing a memory location not stored in the memory element directly connected to the core where the access initiates

#### board itself.

Starting with NVIDIA GeForce 265 [8], part of graphics rendering started to be offloaded on the graphics board. Graphics hardware then took the characteristics of stand-alone processors, able to substitute the CPU in performing complex graphics operations. The term *Graphics Processing Unit* was introduced to refer to that kind of graphics processors

GPU architectures focus on performing large numbers of mostly independent operations on points – vertices – composing a scene to be rendered. This kind of computation sports remarkable similarities with the kind of scientific code known as massively parallel. For instance consider N-body simulations or PDE solvers. The same function is applied to all points of the input domain, to iteratively update some property – e.g. the position in the case of an astronomical N-body simulation, or the temperature in the case of a PDE solver simulating heat conduction. Functions are applied in parallel to all points in the domain, and synchronization happens only at the bounds of the computation, that is at the start/end of the iterative step.

In order to exploits GPUs for efficiently executing this kind of applications, GPU designers started supporting a limited form of programmability, leading to *General Purpose GPUs*.

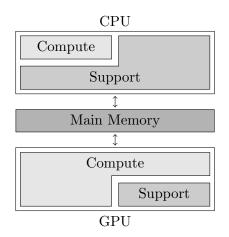

Figure 2.7: Heterogeneous computing with GPGPUs. Hot spots of the application run on the GPGPU to exploit its better computational capabilities

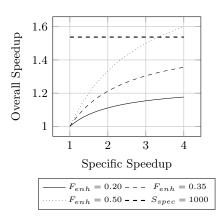

Figure 2.8: Plot of the Amdhal's law for different values of the enhanced fraction  $F_{enh}$ . The bold dashed line is the overall speedup achieved with  $F_{enh} = 0.35$  and a specific speedup  $S_{spec} = 1000$

GPGPUs are basically large sets of synchronous processors. They are specialized on executing massively parallel programs, with little synchronization and a regular behaviour. According to Flynn's taxonomy, GPGPUs fall into the SIMD category, although NVIDIA refers to them using the *Single Instruction Multiple Threads* name, pointing out the ability of executing SIMD code with no fixed vector width [7], thus with an increased efficiency with respect to the most widespread SIMD architecture at that time – vectorial instruction set extension.

Starting from NVIDIA GeForce8800GT [9], massively parallel processors start to be available at modest prices. This lead to a renewed interest in heterogeneous architectures, that could be composed by a general purpose processor, and one or more GPGPUs.

In the GPGPUs setting, the general purpose processor is used to drive the computation. If application hot spots exhibit regular behaviours, they can be offloaded to the GPGPUs, taking advantage of the more specialized hardware. The control processor and the accelerator communicates through the main memory. An example of this setup is depicted in Figure 2.7.

With respect to a typical CPU, a GPGPU dedicates a higher ratio of its area to computational resources. This allows excellent speedups [142] on applications which hot spots can be efficiently mapped on the GPG-PUs. On the other hand, the greater die area dedicated to support

computation on the CPU – e.g. caches – allows to execute a more wider range of applications with reasonable efficiency.

There is a growing trend in the semiconductor industry towards designs that take cues from the GPGPU experience – e.g. coupling CPU cores with heterogeneous parallel accelerator on the same die [2, 152]. The goal is to minimize the overhead of performing data movement between the CPU and the GPU. On the other hand, in HPC environments, stand-alone architectures still dominates the market [4, 10], due to the request of higher peak performance.

## 2.2.6 Taking into Account the Amdahl's Law

Given a program and an optimization, let  $F_{enh}$  the fraction of the program improved by the optimization and  $S_{spec}$  the speedup due to the optimization on the fraction  $F_{enh}$ . Amdahl's law states that the overall speedup of the program due to the optimization  $S_{over}$  is related to the enhanced fraction  $F_{enh}$ :

$$S_{over} = \frac{1}{(1 - F_{enh}) + \frac{F_{enh}}{S_{snec}}}$$

The main consequence of Amdahl's law is that the maximum achievable speedup of an optimization is bound by the optimized fraction:

$$\lim_{S_{spec} \to +\infty} S_{over} = \frac{1}{1 - F_{enh}}$$

Figure 2.8 depicts this behaviour. It plots the overall speedup  $S_{over}$  for different values of the enhanced fraction  $F_{enh}$  varying the specific speedup  $S_{spec}$ . The dashed bold line represents the overall speedup that can be achieved with a specific speedup of 1000x over the 30% of a program. Comparing it with the dotted line, representing the overall speedup when optimizing 50% of the program, one can observe that a more modest speedup of 4x is more effective.

Performance gains expected due to parallel execution are also subject to Amdahl's law. For instance, consider the case where a fraction of the program can be perfectly parallelized. The specific speedup due to the optimization  $S_{spec}$  is thus linear in the number of available processing elements  $N_{pe}$ . The Amdahl's law can be rewritten as following:

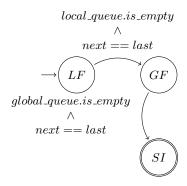

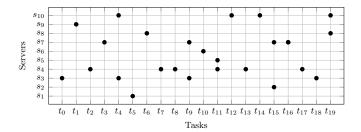

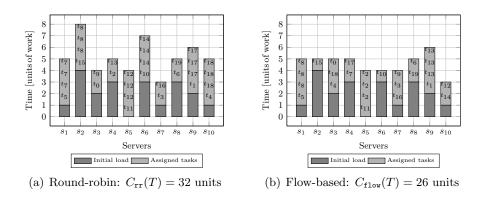

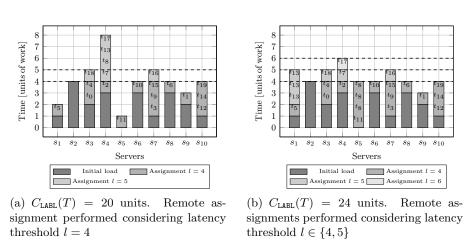

$$S_{over} = \frac{1}{(1 - F_{enh}) + \frac{F_{enh}}{N_{ne}}}$$