# Preface

In the following thesis I consider the realm of Complex Events Processing, the answer to the necessity of extracting new information from continuous streams of events data flowing from peripherals observers to a central system, extracting patterns of events temporally bound. More in details I will focus on TRex, a CEP middleware based on the TESLA formal language, developed by Cugola and Margara [7] [5].

The core component of this middleware is the CEP engine; the kind of information processed and algorithm employed by the engine are suitable to offer a great level of parallelism. As a result in this thesis I will describe the development of a new engine for TRex that uses NVIDIA CUDA [4] to exploit the processing power of modern GPUs to improve CEP performance. My work extends a test project [6] developed by Cugola and Margara that already focused on this goal.

The resulting engine, called GTRex, proved to be very efficient in many scenarios and with the same API and feature set of the default TRex engine, CPU based.

This allowed me to modify the TRex middleware to integrate both engines at the same time. The two can now be used interchangeably applying each of them to the rules it executes more efficiently.

# Contents

| In       | Introduction               |                                        |    |  |  |  |  |  |

|----------|----------------------------|----------------------------------------|----|--|--|--|--|--|

| 1        | 1 Complex Event Processing |                                        |    |  |  |  |  |  |

|          | 1.1                        | Introduction                           | 3  |  |  |  |  |  |

|          | 1.2                        | TESLA                                  | 5  |  |  |  |  |  |

|          | 1.3                        | TRex Middlware                         | 8  |  |  |  |  |  |

|          | 1.4                        | TRex Engine                            | 8  |  |  |  |  |  |

|          |                            | 1.4.1 Automata Incremental Processing  | 9  |  |  |  |  |  |

|          |                            | 1.4.2 Column-based Delayed Processing  | 11 |  |  |  |  |  |

| <b>2</b> | Ger                        | neral Purpose computation on GPU       | 15 |  |  |  |  |  |

|          | 2.1                        | Introduction                           | 15 |  |  |  |  |  |

|          | 2.2                        | Graphics Processing Units              | 15 |  |  |  |  |  |

|          |                            | 2.2.1 NVIDIA GPU architectures         | 17 |  |  |  |  |  |

|          | 2.3                        | CUDA                                   | 21 |  |  |  |  |  |

|          |                            | 2.3.1 Programming model                | 22 |  |  |  |  |  |

|          |                            | 2.3.2 Computing resources organization | 23 |  |  |  |  |  |

|          |                            | 2.3.3 Memory spaces                    | 25 |  |  |  |  |  |

|          |                            | 2.3.4 GPU Occupancy                    | 27 |  |  |  |  |  |

|          |                            | 2.3.5 The SIMD architecture            | 28 |  |  |  |  |  |

|          |                            | 2.3.6 CPU-GPU parallelism              | 29 |  |  |  |  |  |

| 3        | GT                         | cex implementation a                   | 31 |  |  |  |  |  |

|          | 3.1                        | Introduction                           | 31 |  |  |  |  |  |

|          | 3.2                        | The new server                         | 31 |  |  |  |  |  |

|          | 3.3                        | CPU code                               | 32 |  |  |  |  |  |

|          | 34                         | CDP on CUDA                            | 34 |  |  |  |  |  |

|    | 3.5   | Compatibility                | 42 |

|----|-------|------------------------------|----|

|    |       |                              | 43 |

|    |       | -                            | 43 |

|    |       | -                            | 45 |

|    |       |                              | 47 |

|    | 3.6   |                              | 48 |

|    |       |                              | 48 |

|    |       | 0                            | 50 |

| 4  | Fun   | erimental results            | 55 |

| 4  | -     |                              |    |

|    | 4.1   |                              | 55 |

|    | 4.2   | 5                            | 55 |

|    | 4.3   |                              | 56 |

|    | 4.4   | 0                            | 57 |

|    | 4.5   |                              | 58 |

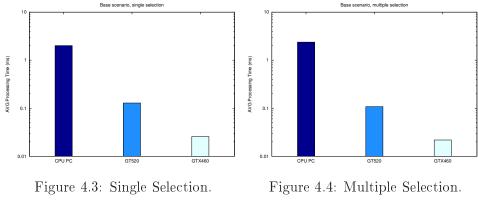

|    | 4.6   | Base Scenario                | 60 |

|    | 4.7   | Length of sequences          | 61 |

|    | 4.8   | Number of Values             | 62 |

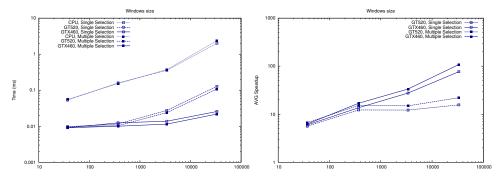

|    | 4.9   | Size of windows              | 63 |

|    | 4.10  | Number of Rules              | 64 |

|    | 4.11  | Negations                    | 65 |

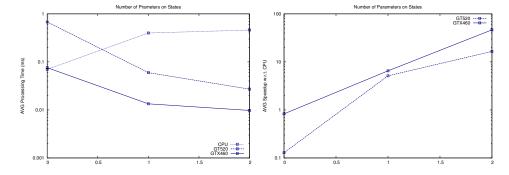

|    | 4.12  | Basic Single Selection Rules | 66 |

|    | 4.13  | Memory Manager performance   | 67 |

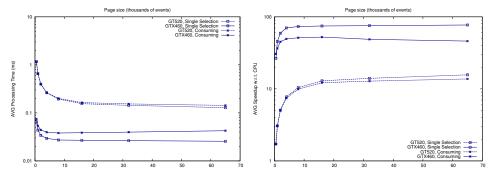

|    |       | 4.13.1 Page Size             | 67 |

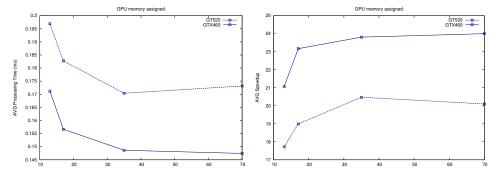

|    |       | 4.13.2 Swapping              | 69 |

| Co | onclu | sions                        | 71 |

| Bi | bliog | raphy                        | 73 |

# List of Figures

| 1.1 | Overview of a CEP application.                                                     | 4  |

|-----|------------------------------------------------------------------------------------|----|

| 1.2 | Overview of the middleware                                                         | 8  |

| 1.3 | Example of the AIP model of rule R1                                                | 9  |

| 1.4 | Example of evolution with the events from table 1.1. $\ldots$ .                    | 10 |

| 1.5 | CDP data structures                                                                | 11 |

| 1.6 | Example of CDP processing                                                          | 14 |

| 2.1 | Sketch of the NVIDIA G80 streaming processors array archi $$                       |    |

|     | tecture.                                                                           | 17 |

| 2.2 | Sketch of the model of a shader processor in the $\mathrm{G80}/\mathrm{G92}$ gpus. | 18 |

| 2.3 | Sketch of the NVIDIA GF100 streaming processors array ar-                          |    |

|     | chitecture                                                                         | 19 |

| 2.4 | Sketch of a multiprocessor on the GF100 gpu, with the new                          |    |

|     | cuda core                                                                          | 20 |

| 2.5 | Sketch of a multiprocessor on the GF100 gpu, with the new $$                       |    |

|     | cuda core                                                                          | 21 |

| 2.6 | Sketch of the typical workflow in a CUDA enabled program                           | 22 |

| 2.7 | Sketch of the grid of threads in cuda                                              | 23 |

| 2.8 | Memories available in the device code                                              | 25 |

| 3.1 | Overview of the new TRex Server.                                                   | 32 |

| 3.2 | Overview of the GPU Engine                                                         | 33 |

| 3.3 | Algorithm execution example, Multiple Selection                                    | 38 |

| 3.4 | Algorithm execution example, Single Selection.                                     | 41 |

| 3.5 | Workflow of a reduction kernel                                                     | 46 |

| 3.6 | Paged memory.                                                                      | 49 |

| 3.7 | Paged memory.                                                                      | 50 |

## LIST OF FIGURES

| 3.8  | Example of a paged memory configuration                     | 52 |

|------|-------------------------------------------------------------|----|

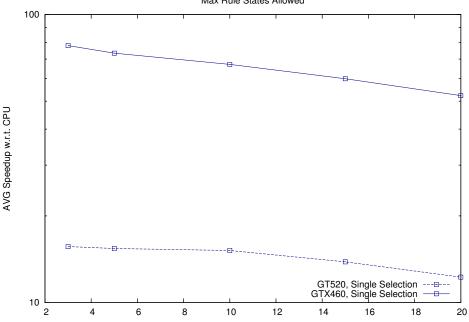

| 4.1  | Impact of an oversized max rule fields parameter $\ldots$ . | 57 |

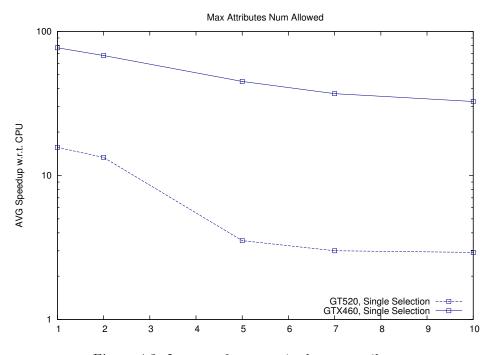

| 4.2  | Impact of an oversized max attributes                       | 58 |

| 4.3  | Single Selection.                                           | 60 |

| 4.4  | Multiple Selection.                                         | 60 |

| 4.5  | Base Scenario                                               | 60 |

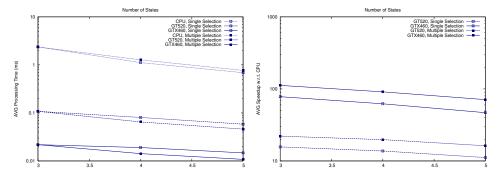

| 4.6  | Varying Sequence Length Scenario                            | 61 |

| 4.7  | Varying Number of Values                                    | 62 |

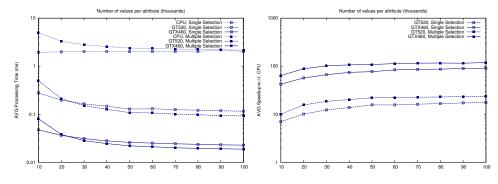

| 4.8  | Varying Size of Windows                                     | 63 |

| 4.9  | Varying Number of Rules                                     | 64 |

| 4.10 | Varying Number of Negations                                 | 65 |

| 4.11 | Varying Number of Parameters between states                 | 66 |

| 4.12 | Varying Page Size                                           | 67 |

| 4.13 | Varying Page Swapping Usage                                 | 69 |

# List of Tables

| 1.1 | Example of packets as | rriving | • • | • | <br>• | • • | <br>• | • | <br>• | · | • | • | • | • | 10 |

|-----|-----------------------|---------|-----|---|-------|-----|-------|---|-------|---|---|---|---|---|----|

| 4.1 | Components of PC1     |         |     |   |       |     |       |   |       |   |   |   |   |   | 56 |

| 4.2 | Components of PC2     |         |     |   |       | •   |       |   |       |   |   |   |   | • | 56 |

# List of Algorithms

| 1.4.1 CDP Algorithm on CPU                                | 13 |

|-----------------------------------------------------------|----|

| 3.3.1 Overview of the handling code                       | 35 |

| 3.4.1 CDP Algorithm on GPU, Multiple Selection            | 36 |

| 3.4.2 CDP Algorithm on GPU, Single Selection, last-within | 39 |

| 3.4.3 Reduction method used for Single Selection          | 40 |

| 3.5.1 GPU function that controls negations                | 45 |

# Introduction

Complex Event Processing is an important topic in information technology: it analyzes streams of information coming from multiple sources to extract new, more complex, knowledge. Many CEP middlewares, taking different approaches, have been developed as a solution to the CEP problem; one of these is TRex2, developed by Cugola and Margara [5].

At the same time modern graphics cards with powerful Graphics Processing Units (commonly abbreviated GPU), are nowadays installed in every computer sold, and using their capabilities for general purpose computation is quickly becoming a common technique. NVIDIA is the major player in this field, thanks to it proprietary technology called CUDA, that greatly simplifies the usage of their GPUs to make generic computations not related to the visualization of an image on the computer display.

In this thesis indeed CUDA will be exploited to boost the performance of the TRex2 core engine; CHAPTER 1 starts with an exemplified introduction to the CEP problem and continues with the description of the current version of the TRex2 middlware and, with more details, of its core engine.

CHAPTER 2 instead gives an overview of the typical architecture of a modern GPU, explains the principles of GPU programming and shows the programming model and some of the features of CUDA.

CHAPTER 3 is where the actual work done in this project is described: it contains the core algorithms of the GPU powered version of the engine as well as many descriptions of the solutions adopted to make everything work.

CHAPTER 4 analyzes with many benchmarks trying different workloads the performance gains obtained over the standard CPU version of TRex2. Each test is presented with a pair of graphs and an interpretation of the result. Introduction

## Chapter 1

# **Complex Event Processing**

## 1.1 Introduction

Sometimes information systems have to deal with big quantities of flowing data that enter the system continuously; as example fraud detection tools, financial applications and even airlines must promptly take actions based on the information they gather in real time. Being able to timely process this data to extract new knowledge is not trivial, and is the main goal of Complex Event Processing.

Recently, different approaches to the problem have been studied: some rely on the solid base of DBMS (DataBase Management Systems), introducing some modifications to better adapt those systems to the world of live streams of data, others are built from the beginning around the idea of event notifications, observers and sinks.

As example, Data Stream Management Systems allow data to be processed in streams, while it flows through the system, with continuous query execution. They operate on windows of events, where a window is a finite collection of events temporally bound. These systems operate mainly on pure relational tables, where they index the incoming data before the computation begins. This kind of computation is indeed unnatural and not enough flexible to support the constructs needed by a complex event processing language, that selects complex patterns of events bound by temporal relations.

On the other hand there are systems built around a native concept of

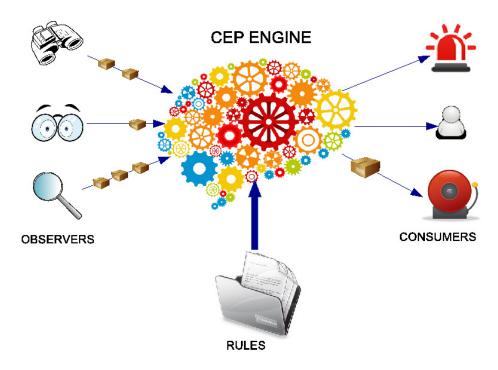

event notification. In these systems (like the one shown in FIGURE 1.1) many components collaborate exchanging information about events occurring: some of these components publish notifications about events happened (they are the observers), while others (the consumers) subscribe to notifications of events they are interested in. The whole system relies on a message based communication (the boxes in the picture). The dispatcher is in charge of routing the events to the subscribers. In this scenario a CEP engine (the brain in the centre of the picture) generates complex events based on combinations of events notifications as described in specific rules, installed in the engine.

Figure 1.1: Overview of a CEP application.

TRex2, the CEP middleware presented and enhanced in this thesis, is based on the latter kind of systems. One basic example, that will guide us throughout the thesis, is the following possible scenario in which a CEP middleware acts: in an automation system there are N tanks that contain some kind of liquid. Each tank has its own valve that can be opened and closed remotely. In order to make the system safe, an alarm state must be notified in the following cases:

- a specific tank is not empty within 10 minutes after a valve open command has been issued for the same tank

- a specific tank is empty and not any valve open command has been issued in a 10 minutes interval before the empty tank notification

- the maximum level of liquid in a specific tank is greater than a specified treshold within 1 minute from a valve open command for the same tank

- the level of liquid for a specific tank is increasing in the last 10 readings and a valve open command has been issued within 1 minute

In this example each of the four data extraction paths is specified in a different rule; the sensors for the level of the liquid installed in the tanks are the observers, while the alarm systems are the sinks.

As the will see below TRex2 has observers, an engine and a dispatcher; rules for the TRex2 engine are written in the TESLA specification language, that will be introduced in the next section.

### 1.2 TESLA

TESLA is a complex event specification language; it has been proposed by Cugola and Margara in 2010 [7]. It combines a simple and clean syntax with an high expressiveness and flexibility. It provides content and temporal constraints, parameterization, negations, sequencies, aggregates, timers and fully customizable policies for events selection and consumption. With these features it fits the requirements needed to express all the four formulations of the example problem. It considers incoming data items as notifications of events and defines rules declaring how they combine to build new complex events. *Events* happen instantaneously at some point in time and are observed by sources, which encode them in event notifications. Each event has a type, a timestamp and a set of attributes, identified by their name and information kind.

In the automation system example a reading for the level of liquid in a tank is an event with the attributes Value, stating the level of the liquid, and TankID, representing the tank for which the level has been read. Also the valve open commands issued can be thought at as events, with a TankID attribute representing the target tank.

As example the event stating that at time 10 a liquid level of 5 for tank number 1 has been read is formatted as:

Level@10{TankID = 1, Value = 5}

while an event stating that at time 3 a valve open command for tank 1 has been issued can be formatted as:

#### $Open@3{TankID = 1}$

Parameters express relations between attributes of different events: the fact that the the tank for which the level of liquid is read and the valve open command has been issued must be the same, as example, is expressed through a parameter on the TankID attribute of the *Open* and *Level* events, that must be equal.

*Negations* instead state what should not happen at some time in the events sequence: as example the second formulation of the example above specifies that there must not be any Open event in a 10 minutes range before the Level event.

Aggregates allow the computation of a single value as a function of the values of attributes of the events respecting the aggregate constraints; as example the maximum of levels read in a time interval can be computed as a max function on the values read.

Selection Policy is an important aspect in the rule definition, as it affects deeply how the simple events are used and combined to form complex events; let's see what it does with the help of the following general structure of a TESLA rule:

```

Rule Definition

```

| define    | $CE(Att_1:Type_1,,Att_n:Type_n)$ |

|-----------|----------------------------------|

| from      | Pattern                          |

| where     | $Att_1 = f_1, \dots, Attn = f_n$ |

| consuming | $e_1,, e_n$                      |

*Define* describes the complex event created by the rule, with its name and its attributes.

The *pattern* clause is probably the most important, because it describes the pattern of events that form the complex event. The temporal relation between them, the static constraints on their attributes as well as the selection policy are defined here.

The first event defined in the pattern clause is called *terminator*; it is indeed the event that closes a sequence of events that can create a new complex events and whose timestamp is used as timestamp for the event to be created. As we will see later, it is very important especially in the CDP [sec 1.4.2] algorithm because it is the event that triggers the key compution for the creation of new complex events.

Each event in the clause following the terminator is preceded by the *selection operator*: the selection operator can be one out of each-within, last-within or first-within. It allows to define precisely and without ambiguity which simple events must be selected for the creation of the complex event.

Finally all the events of the pattern clause are translated in *states*, that will become important when talking about the implementations of the CEP engines.

The *where* clause instead specifies parameters binding different events, while the *consuming* one specifies which events will be consumed, thus deleted, once they have participated to the creation of a complex event.

The first formulation of the automation example above can thus be expressed with the following TESLA rule:

| $\underline{\text{Rule } \text{R1}}$ |                                                    |

|--------------------------------------|----------------------------------------------------|

| define                               | Alarm(TankID:int)                                  |

| from                                 | Level(TankID = \$x, Value < 5)                     |

|                                      | and last $Open(TankID = \$x)$ within 10 from Level |

| where                                | TankID = \$x                                       |

Note that the selection policy for the Open event is of the last-within kind. This means that if there are more than 1 Open events occurred in the last 10 minutes when a terminator arrives, only the last valid one will be selected, and only one complex event will thus be created. With an each-within selection instead each Open event would have caused the creation of 1 complex event.

## 1.3 TRex Middlware

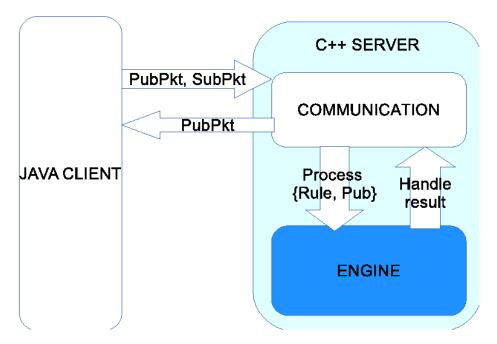

TRex is a complete middleware for complex event processing. It is based on a simple publish-subscribe architecture [5] It has a server that initializes the computation engine, deploys rules and listens for new subscriptions and events notifications. These are provided by java clients, that use specific TRex libraries. Clients send subscription packets (SubPkt) and event notifications (PubPkt) to the server, that accordingly, and using the rules deployed, creates and publishes complex events (still represented as PubPkt) to the subscribed clients, as shown in FIGURE 1.2. Still the most critical component in this system is probably the engine: it is the most impacting component on overall performance of the middleware, when it is not limited by other factors like poor network connections.

Figure 1.2: Overview of the middleware.

## 1.4 TRex Engine

Three versions of the engine have been created before my project took off: two of them run on the host CPU and employ different algorithms, AIP and CDP, while a third one, still based on the CDP algorithm, used CUDA to speed up the computation, but was a very limited test project with only a small subset of functinalities. Currently the AIP version has been dropped, because it demonstrated to be less efficient than the CDP one; still I will give a basic introduction to the AIP, as it represents the typical approach to rule processing adopted by commonly available CEP engines.

#### 1.4.1 Automata Incremental Processing

The AIP approach is probably the most natural one when creating an algorithm to process complex events; it is also used by Esper [1], that is the most used open source CEP system. It models rules as linear, deterministic and finite automata, which evolve with the events entering the engine.

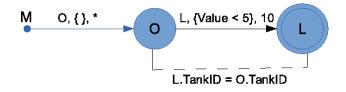

Figure 1.3: Example of the AIP model of rule R1.

FIGURE 1.3 is an example of such rule model for rule R1. To keep track of the history of events arrived, instances of the automata are created; each instance that is not in a final state represents a partial sequence.

A partial sequence is a collection of events that partially satisfies a specific rule installed in the engine. Still it can't trigger the creation of a new complex event since there are still missing packets to complete the sequence required by the rule.

At the beginning all the automata have a single state, the initial one (M in FIGURE 1.3). When a new event enters the engine the computation starts checking all the available automata and deleting the ones that clearly can't evolve any further because their timing constraints can't be compatible with any event occurring from that moment on. Then the kind and the parameters of the new event are checked against the transition constraints of the current state of the automata. These constraints depend on the rule that the automata is following and the parameters of the events that brought to that specific automata up to that moment. As example, in FIGURE 1.3, a transition from the state M is triggered when an event of kind O is received at any time and with any attribute value. The transition from state O to state L is allowed only when an event Level arrives with a V attribute lower than 5 and with a TankID equal to that of the O event. If everything is compatible, a new automata is created from the previous one, that is not deleted because it may still evolve differently with future events. When an automata reaches its ending state, the corresponding complex event is generated and the automata is deleted.

Table 1.1: Example of packets arriving

| Time | Event                |

|------|----------------------|

| 1    | $O{TankID = 3}$      |

| 2    | $O{TankID = 4}$      |

| 4    | $O{TankID = 1}$      |

| 5    | $O{TankID = 5}$      |

| 7    | $O{TankID = 3}$      |

| 12   | $L{TankID = 3, V=1}$ |

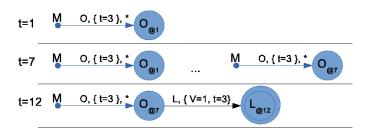

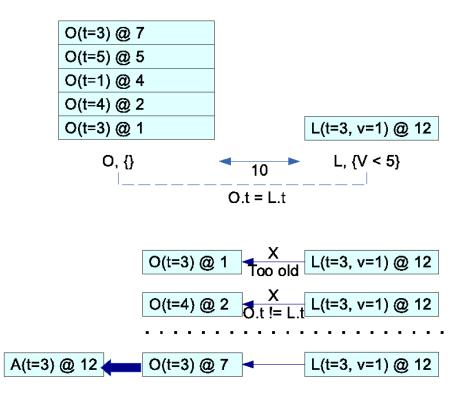

Consider as example the events from table 1.1, showing a possible occurrence of incoming events; they produce the computation showed in FIGURE 1.4. At time 1 the event  $O{\text{TankID} = 3}$  arrives and a new instance of an automata is created. The same happens at time 2, when there will be 2 automata instances waiting for a possible terminator event L. At time 12, when a terminator arrives, the instances created at time 1 and 2 previously will be deleted, since they will be too old to trigger any new complex event. On the other hand there will be an automata, created at 7, that will evolve in its final state. That automata will create a new complex event.

Figure 1.4: Example of evolution with the events from table 1.1.

If a multiple selection policy is adopted, then all the automata must be checked for every new event. Instead, with a single selection policy, the computation triggered by the arrival of the last terminator event can be stopped as soon as the first valid automata evolution is found, as long as they are checked in the order requested by the selection policy. The algorithm is quite simple, but, even if implemented efficiently, can consume quite a lot of memory, and is not as efficient as the CDP algorithm.

#### 1.4.2 Column-based Delayed Processing

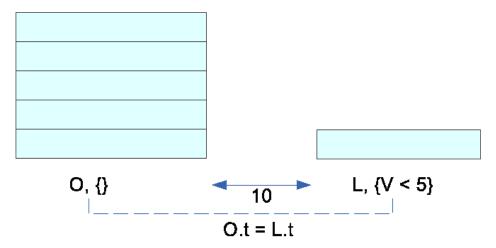

The CDP approach is the opposite when compared to AIP: when a new event is notified the engine does nothing but storing it for a delayed computation. The representation of events and partial sequences is, indeed, completely different from the AIP. The basic data structure employed is a column: one column stores all the received events that are relevant for a specific state of an installed rule, as shown in FIGURE 1.5; the columns are bound with constraints on the timestamps and on the attributes of their events. Moreover the dimension of the columns reserved for the terminator events is only 1: this is because at any time only 1 terminator at maximum will be stored in the engine.

Figure 1.5: CDP data structures.

Only one physical copy of the event is stored, so that the events in the columns are in reality only pointers to the unique original event. As said before the computation is delayed, and is launched only when a terminator event is collected, because a terminator is the necessary condition for a complex event to be created. So when a new event arrives it is checked against all the rules installed and added to the columns of the corresponding

states declared in the rule, if any. In this phase also the static constraints on their attributes are checked. If one of these states is a terminator one, the computation for the related rule is launched, as shown in algorithm 1.4.1.

- line 5: old events in the columns that can't combine with any newly generated event are deleted

- line 7: all the columns are checked in turn and partial sequences are created; a partial sequence is the corresponding element of the automata of the AIP approach: it is a sequence of primitive events that up to the state currently being checked form a valid sequence for a complex event. Again, if a full valid sequence is found, a corresponding complex event is generated. Events in the columns are stored in order from the oldest to the newest, so that the computation for a specific state, when a single selection policy is applied, can be stopped as soon as the first valid element is found and added to the partial sequence. With a multiple selection policy, instead, all the elements of a column must be checked in any case.

- line 8: if there are valid sequences the corresponding complex events are created

FIGURE 1.6 shows an example of computation for rule R1. There are two columns, one for the event type O and one for the terminator event L, with a size of 1.

At time 12 the terminator arrives and the computation starts: the O column is analyzed in order, from the last or the first event depending on wether the selection policy is first, last or each within. The event with timestamp 1 is immediately discarded and deleted, since it won't be compatible with any future terminator. The rest of events are all analyzed, but only O(t=3)@7 meets all the requirements and is used to form a valid sequence. From this valid sequence the complex event A(t=3) is created, with the same timestamp of the terminator in its sequence.

#### **Computing Aggregates**

The computation of aggregates specified in a rule is performed at the end of the work cycle related to the arrival of an event, since it is only needed

| Alg      | gorithm 1.4.1: CDP Algorithm on CPU                                |

|----------|--------------------------------------------------------------------|

| 1 fe     | $\mathbf{oreach}$ rule in getMatchingRules(e) $\mathbf{do}$        |

| 2        | ${f for each}\ column\ in\ getMatchingColumn(rule)\ {f do}$        |

| 3        | $\operatorname{column.add}(e)$                                     |

| 4        | if column.isLast() then                                            |

| 5        | deleteOldEvents(column)                                            |

| 6        | partialSequences.insert(e)                                         |

| 7        | sequences = computeSequences(partialSequence.column)               |

| 8        | ${ m generateCompositeEvents(sequences)}$                          |

|          |                                                                    |

| 9 d      | eleteOldEvents(col)                                                |

| 10       | if col.isFirst() then                                              |

| 11       | $\operatorname{return}$                                            |

| 12       |                                                                    |

|          | ol.getPreviousCol().deleteOlderThan(col.getFirstTS()-col.getWin()) |

| 13       | deleteOldEvents(col.getPreviousCol())                              |

|          |                                                                    |

|          | omputeSequences(partSeqs, col)                                     |

| 15       | if col.isFirst() then<br>return partSeqs                           |

| 16<br>17 | previousColumn column.getPreviousColumn()                          |

| 18       | foreach p in partSeqs do                                           |

| 19       | foreach ev in col.getPreviousCol().getEvents() do                  |

| 19<br>20 | if p.checkParameters(ev) then                                      |

| 20<br>21 | newPartSeqs.insert(createPartSeq(p,ev))                            |

| 22       | if checkSingleSelection() then                                     |

| 23       | break                                                              |

| 24       | computeSequences(newPartSeqs, col)                                 |

|          |                                                                    |

when new complex events are found. It is performed sequentially on the events requested by the rule definitions. The events relevant for a specific aggregates have their own columns assigned, just like the events used for the computation of the states transitions. The algorithm loops through them and, if the parameter verification succeeds, their attribute are processed as needed to complete the computation.

#### **Computing Negations**

Negations, in the CDP algorithm, are checked within the computation routine. Indeed when a new candidate primitive event for a partial sequence

Figure 1.6: Example of CDP processing.

is found, negation constraints are sequentially checked, looping over the negations column, and eventually invalidate the new possible partial sequence, that is deleted. Again, just like aggregates, events relevant for a negation are stored in a dedicated column.

#### Exploiting multi-core CPUs

Exploiting modern CPUs having multiple computational cores efficiently is quite easy, at least in theory, in a CEP engine. Indeed a very simple form of parallelism is exposed by the fact that usually an engine must handle multiple rules; so both AIP and CDP can easily distribute the compution designating different CPU threads to different rules. Each thread can then perform its jobs without affecting or being affected by the others, thus exploiting all the physical cores available, as long as there are enough rules to occupy them.

## Chapter 2

# General Purpose computation on GPU

## 2.1 Introduction

In this chapter I will introduce Graphics Processing Units and describe in details the General Purpose computing on GPU programming model, with its advantages and disadvantages. I will focus on CUDA, since it has reached a great success and maturity, and is the recommended choice for general purpose GPU programming.

### 2.2 Graphics Processing Units

A GPU (Graphics Processing Unit) is a specialized processor designed to efficiently make the computations necessary to create an image to be displayed. It is the core of a graphics card, that also incorporates dedicated memory chips and the circuitry to allow communications between the GPU and the rest of the computer system, like the host CPU and DMA controllers.

From the very first models, developed in the first '80s, graphics cards were designed with very specific functionalities; they had custom microchips implementing a very limited set of functionalities, for which they were great. On the other hand they couldn't do anything but what they were designed for. They were mainly used to draw simple geometric shapes like lines and circles first, and for playing 3D games or high-end 3D rendering then. With the advent of the OpenGL API and similar functionality in DirectX, GPUs added programmable shading to their capabilities. Each pixel could now be processed by a short program that could include additional image textures as inputs, and each geometric vertex could likewise be processed by a short program before it was projected onto the screen.

Indeed the workload for the creation of a 3d scene is more or less the same for every pixel and vertex of the scene, so that an architecure with hundreds or thousands of simple computation units performing floating point algebra following the same rules is the ideal solution. The costs could be kept low because the basic architecture was very simple.

NVIDIA was the first to produce a chip capable of programmable shading, the GeForce 3 (code named NV20). By October 2002, with the introduction of the ATI Radeon 9700 (also known as R300), the world's first Direct3D 9.0 accelerator, pixel and vertex shaders could implement looping and lengthy floating point math, and in general were quickly becoming as flexible as CPUs, and orders of magnitude faster for image-array operations. Pixel shading is often used for things like bump mapping, which adds texture, to make an object look shiny, dull, rough, or even round or extruded.

In 2006, though, NVIDIA released the G80 GPU. It was the very first GPU with programmable generic stream processing units. Thus the G80 could be exploited to make general purpose computation, not necessarily related to the creation of an image to be displayed.

Actually there are two alternatives to develop gpu enabled programs: OpenCL [3], and NVIDIA CUDA [4]. While the former generates code usable on a wide range of devices such as GPUs from different manifacturers and multi core CPUs with different architectures, the latter can only do it for NVIDIA GPUs; still, being targeted for a narrow scope of devices, it is more optimized to exploit all the capabilities of the specific hardware. I will analyze only the NVIDIA framework, which is the most used and probably the easiest to start gpu development with, but the ideas showed in this thesis should apply to any of these parallel development environments, with exception of the CUDA only dynamic parallelism (cap 3), that will be supported soon anyway also by OpenCL.

#### 2.2.1 NVIDIA GPU architectures

Before showing the programming model, it is important to describe a bit the hardware that will run the CUDA programs, since it is fundamental to analyze and understand the performance of the programs that they execute.

Since CUDA has been very appreciated in different fields of the information technology, from financial to physics and medicine, NVIDIA continued to improve the general purpose computing capabilities of its GPUs with every new architecture, and even producing some specific models designed specifically for this purpose, without any capability of showing an image on a display. From 2006, when it was introduced, there have been mainly three significant architecture advancements, G80, Fermi and Kepler, as described in the next sections. Within a single family, moreover, the same architecture is configured in different ways: as example the GPU could be sold with different numbers of active cores, with faster or slower memory, with different core clocks and so on to cover all the slices of the market. Still the capabilities of the GPU within the same family don't vary.

#### **G80**

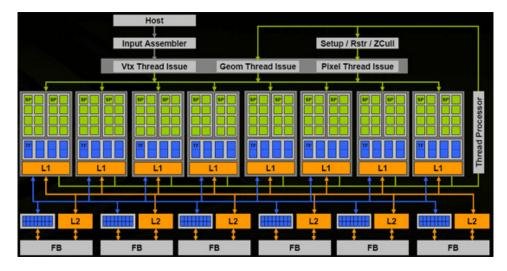

Figure 2.1: Sketch of the NVIDIA G80 streaming processors array architecture.

The G80 chipset is the first that unifies all the shaders (pixel, vertex, geometrix or physics) under one computational unit, called Stream Processor,

CHAPTER 2. General Purpose computation on GPU

Figure 2.2: Sketch of the model of a shader processor in the G80/G92 gpus.

that is the core of CUDA. As we see in FIGURE 2.1, in one GPU there is an array of identical SPs.

In the sketched fig. 2.2 the layout is made clearer: there are many streaming multiprocessors (SM), where each has a number of SPs, each with its own **Registers**, one common **Shared Memory** and one **Instruction Unit**, that is in charge of mapping active threads on the available SPs.

Within the SM there are also the read only **Constant Memory** and the Texture Memory. The device memory, called **Global Memory** resides outside the multiprocessor, being effectively the DRAM of the board, available to every multiprocessor. The image also shows that the only memory locked to one SP is the register space, while each other memory is shared between all the SP of one multiprocessor or between different SMs too. A SP is a fully pipelined single-issue processing core with two ALUs and a single floating point unit (FPU). Single integers operations are performed with a 24bit precision.

SM are in turn grouped by two or three in Texture Processor Clusters (TPC), that includes support for Texture processing, though these features are seldom used for general purpose computing and will not be investigated in this thesis.

**Evolutions:** Fermi, Kepler

Figure 2.3: Sketch of the NVIDIA GF100 streaming processors array architecture.

The Fermi architecture made its debut in the end of 2009 and greatly enhanced the GPGPU capabilities, as a response to the notable interest gained by CUDA. The GPUs used in chapter 4 to test the performance of GTRex are both based on this architecture, that is today largely diffused in most personal computers. Fig 2.3 shows the new blocks (still called SM, streaming multiprocessors), now with 32 or 48 cores each. SPs are now called Cuda Cores, showing the intent of NVIDIA to push and promote the CUDA technology. With a total of 16 SM, GF100, the reference GPU for the Fermi family, can reach 512 cuda cores. Each cuda core executes 1 warp of 32 threads.

One of the most interesting extra of the new core is the presence of an L2 cache between the SM and the global memory that relaxes the constraints to obtain coalesced memory accesses with the first generation GPU and also allows a more efficient usage of the global memory. This is indeed a very important aspect as will be shown below.

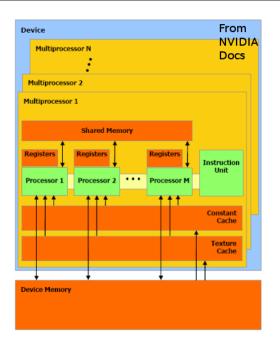

Figure 2.4: Sketch of a multiprocessor on the GF100 gpu, with the new cuda core.

Fig 2.4 shows the new SM, even if it remains quite similar to the preceeding ones. The interesting news are the number of registers available, now 32768 per SM and the new INT unit to make operations with integers natively. This feature is another example of enhancements introduced specifically for the GPGPU, since vertex and pixel computations rely on floating point math.

Finally, with Kepler, released in 2012, the GPGPU capabilities of the NVIDIA GPUs were enhanced even more, with a brand new SM (shown in FIGURE 2.5), now called SMX, grouping 192 Cuda Cores and bringing a new specialized unit to allow dynamic parallelism, a major enhancement for CUDA that will probably make even more profitable the usage of CUDA to accelerate parallel applications.

On the other hand the GPUs based on Kepler are still high priced and not so much diffused, so that I hadn't the chance to try this innovation for GTRex. More considerations on possible Kepler advantages for the project are shown in the conclusions of this thesis.

Figure 2.5: Sketch of a multiprocessor on the GF100 gpu, with the new cuda core.

## 2.3 CUDA

The CUDA toolkit is composed of a compatible driver, a closed source compiler (nvcc) and a set of libraries to interact with the gpu from within a normal C program. Many wrappers exist that allow the usage of cuda in different programming environments, but it is designed for C and C++. To interact with the graphic hardware there are two methods, not compatible one with another. They are C for CUDA and Driver API. While the first is simpler to use, the latter exposes more options and low level functions, giving a better level of control over the hardware. For the project the C for CUDA approach was used, since it allows to write a smaller and simpler code granting at the same time all the features exploited by the engine. In the following I will not analyze in details all the specific functions to call in order to initialize the environment; all those informations can be found in the NVIDIA CUDA Programming Guide [2]; I will try to give an overview of the basic principles to understand in order to program with CUDA. From now on I will call **host** code the program that will run on the CPU, while the program run by the graphic card will be referred to as **device**.

#### 2.3.1 Programming model

The most important concept in the development of a cuda application is the **kernel**: it describes the job that will be done by the gpu. It is the equivalent of the main() function of the host code. The keyword to declare such a function is **\_\_global\_\_**, and it must return a void type. From a kernel the programmer can call other functions run by the gpu and declared as **\_\_device\_\_** that don't need to necessarily return a void.

The memory space accessed by the kernels is completely separate and independent from the memory of the C program using CUDA, at least in the most general and more efficient case where the unified address space is not used. Thus, in order to give the GPU the data to work on, specific functions to copy memory areas to and from the GPU must be used.

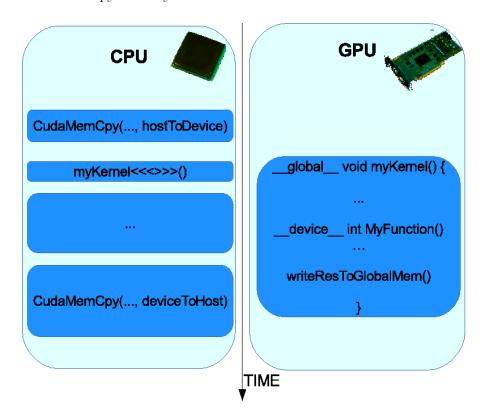

Figure 2.6: Sketch of the typical workflow in a CUDA enabled program.

FIGURE 2.6 represents the typical workflow: the program at a certain point asks the CUDA driver to copy some data to the device, then it invokes the kernel that will be executed on the GPU. The kernel launch request on the host side is asynchronous and typically very quick. From this moment the CPU and the GPU work in parallel. On the GPU the kernel can call other functions that will be executed on the device and share the memory space with the callee; at the same time the CPU can do anything else. Finally the host program asks for the resulting data to be copied back to the host memory. This call instead is typically blocking, since the completion of the kernel is necessary for the data to be copied back to be valid and consistent. In this way the memory copy from the device will end a bit later than the end of the GPU computation, because of the time necessary to phisically move the data.

Figure 2.7: Sketch of the grid of threads in cuda.

#### 2.3.2 Computing resources organization

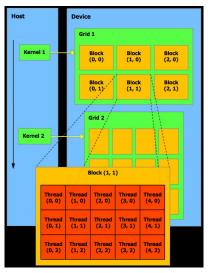

The amount of parallel processing units on a GPU is great, but coordinating and managing all them is not trivial: the following hierarchical model is used.

From the smallest to the biggest, the massive amount of computing units is grouped as follows: **thread**, **warp**, **block**, **grid**, as shown in FIGURE 2.7. More in details 32 threads form a warp, a custom number of threads form a block and a custom number of blocks compose the grid, that characterizes the kernel launch.

- thread: it's the basic computational unit; this means that the code of the kernel will be effectively executed by each thread. Each thread is uniquely identified in a kernel launch thanks to the intrinsics threadIdx, blockIdx and blockDim. All these three-dimensional variables have x, y and z subfields. Indeed the threads can be organized in multi dimensional grids. As example, in the common convention, the first thread of a 1 dimensional grid will be the one having threadIdx.x and blockIdx.x equal to 0

- warp: the warp abstraction is hidden to the developer, since there's not any routine or API call to modify a warp anyhow. Indeed it is directly bound to the physical configuration of the GPU. It's important to know of its existence because it is a set of 32 threads that in a given moment will be performing exactly the same instruction, since it is supplied by a single instruction issuer. So, when a kernel includes some divergent paths, if all the threads of one warp will take the same path it would not harm the result too much, but this will be shown in SECTION 2.3.5

- block: the block dimension must instead be set by the developer, and can be read from the kernel code with the blockDim variable. It is a 1,2 or 3 dimensional group of threads that share the same shared memory and that will be scheduled for execution at the same time by the driver. The optimal choice of the dimension of one block is a multiple of 32 that is a multiple of the dimension of a warp -, because otherwise there would be for sure some shared processors idling for the duration of the entire kernel.

- grid: the biggest grouping entity is the grid. It is only 1 in a kernel; like for the threads and blocks, though, it provides the **gridSize** variable, that represents the number of blocks per dimension (x, y and z like before) and can be accessed from each thread. This comes useful when the developer has to map different memory areas to each thread within his kernel.

One trivial example for the grid organization, where only one dimension is defined for each entity: if we launched 10 blocks, each with 32 threads, we would have a total of 320 threads numbered from 0 to 319, with blockIdx.x varying from 0 to 9 and threadIdx.x varying from 0 to 31 and blockDim.x fixed at 32. Each thread could compute its index and be uniquely identified as idx = threadIdx.x + blockIdx.x \* blockDim.x.

#### 2.3.3 Memory spaces

The memory area where data is copied to from the host code is physically resident on the GPU DRAM; there are many reasons for which it shouldn't be used as the default memory for the code execution and there are better alternatives offered by CUDA, that gives different kinds of memory (shown in fig. 2.8) to rely on, each with different pros and cons. The following list enumerates the memory spaces available starting from the "outer", phisically the furthest from the SP or Cuda Core, to the inner, the nearest.

| Grid               |                 |                 |                 |  |  |

|--------------------|-----------------|-----------------|-----------------|--|--|

| Block (0, 0)       |                 | Block (1, 0)    | Block (1, 0)    |  |  |

|                    |                 |                 |                 |  |  |

| Shared             | Memory          | Shared          | Shared Memory   |  |  |

| †                  | 1               |                 | <b>†</b> †      |  |  |

| Registers          | Registers       | Registers       | Registers       |  |  |

| <b>+</b>           | <b>↓</b>        | <b>↓</b>        | ↓               |  |  |

| Thread (0, 0)      | Thread (1, 0)   | Thread (0, 0)   | Thread (1, 0)   |  |  |

| \$ 111             | t 111           | 1 111           | <u> </u>        |  |  |

| Local<br>Memory    | Local<br>Memory | Local<br>Memory | Local<br>Memory |  |  |

| Global<br>Memory   |                 | Ť               |                 |  |  |

| Constant<br>Memory |                 |                 |                 |  |  |

| Texture<br>Memory  |                 |                 |                 |  |  |

Figure 2.8: Memories available in the device code.

• Global memory: it is phisically the DRAM of the graphic card, so it is the biggest space available in the device code. In fact almost the whole quantity of ram (a little space for the displayed image must not be requested) can be assigned to a single pointer. It has a huge bandwidth (more than 80GB/sec), but also a huge latency (around 400-600 clock cycles). This means that it is perfect to fetch very big and contiguous memory areas, but it is not recommended for a random access to few bits per time. In the Fermi and newer architectures this disadvantage is partially masked by the shared cache to global memory. This is the only memory that makes possible the return of values from the GPU to the host.

- **Constant memory**: as the name itself indicates, this memory is accessible in a read only way from the device code, and it can be written only from the host code. It is limited in size (64kbyte), but, being cached, it is useful when many threads concurrently access the same memory location.

- Shared memory: this small sized memory (from 16kb up to 48kb) is shared between all the threads of one block. It is very fast, but the programmer should take care to reduce concurrent access to the same memory block, otherwise the performance could drop.

- **Registers**: they are tied to one specific thread during the execution, so that they are really fast and they can't suffer from concurrent access, but they are limited and an excessive usage can restrict the number of concurrent threads really executed at the same time. Their number increases from G80/G92 to GT200 and to GF100 and GK110, and starts from a minimum of 8192 to a maximum of 65536.

So the general solution to exploit efficiently the resources of the GPU is: copy the data to the global memory, let each thread read the needed data in its registers or in shared memory, wether the threads of a block should cooperate on the same data, and finally write back the results to the global memory, from where it will be copied to the host memory.

#### Memory access coalescing

Because of the limits of the global memory, that is mainly a huge latency, it is important to organize access to this memory so that with a single transaction a lot of data can be fetched (remember also that it has an incredible bandwidth). The requirements for this to happen have relaxed from generation to generation of gpus, but I will now show the requirements needed to achieve it on every gpu family, which have been used in the current project. From the CUDA programming guide, we know that the global memory access by all threads of a half warp is coalesced into one or two memory transaction if it satisfies the following three conditions:

- each thread must access either 4, 8 or 16 bytes words, respectively coalesced into a 64, 128 or 128 bytes memory transaction

- all 16 words must lie in the same segment of size equal to the memory transaction size, or twice the memory transactio size when accessing 16byte words

- threads must access words in sequence: the  $k^{th}$  thread must access the  $k^{th}$  word of the memory segment

. If one of these conditions is not met, then 16 different memory transcations are issued, with a throughput significantly reduced. Again, with Fermi and Kepler these conditions have been relaxed a lot, so it is much easier to write an efficient code without all these constraints.

#### 2.3.4 GPU Occupancy

As said above the resources of the GPU are limited, and they will affect the real level of parallelism that a specific kernel will reach: since every kernel will need a predefined number of register per thread to work, and sometimes also shared memory, there will be often a cap to the maximum number of threads that will effectively run in parallel for a given kernel. As example if we have a kernel that needs 30 registers and runs on a G92 gpu, depending on the configuration of threads per block the occupancy of the gpu will range from 17% to a maximum of 33%. In fact with the G92 chipset each multiprocessor has 8192 registers, so each multiprocessor will run 8192/30 = 273 threads at maximum, divided in blocks of 128 threads each result in 2 active blocks per multiprocessor. But the theorical limits of the gpu allow it to run 768 threads per multiprocessor, so the occupancy is 256/768 = 0.33. Besides this, the more multiprocessor a gpu has, the more threads it will really run in parallel (in the example 256 more threads per multiprocessor). It is also important to note that a different configuration can change the occupancy of the gpu: as example if for the same kernel we would have launched 192 threads per block, then only one block of threads could have run at a given moment on one multiprocessor, and the occupancy would have dropped to 192/768 = 0.25. For this kind of considerations there is the CUDA Occupancy Calculator, a tool released by nVidia that will plot the real occupancy of a given GPU with the register/shared memory usage set by the user. Moreover the number of register used by one thread can be capped giving some instruction to the nvcc compiler, but it is important to note that not always an higher occupancy will bring better performance, because to reduce the number of registers some data can be shifted to the global memory, that has an high latency.

#### 2.3.5 The SIMD architecture

There is a big difference between writing a working code and writing an optimized code. On the gpu the hardware limits make a fine development essential to achieve the results expected from the huge computational power available. It is suggested to read the CUDA Best Practices Guide from nVidia to get some useful tricks in the optimization of the code. This is for sure the most important concept to understand in order to write cuda enabled applications with good results. What SIMD means is Single Instruction Multiple Data. This means that many computational units need to execute exactly the same instruction every other unit is doing on its own chunk of data. In fact one instruction issue unit make each thread of a specific warp perform the same instruction; as a result if only one thread of a warp needs to do a different task the parallelism is broken: in an unpredictable way first some units than some others stop working actively and just complete some dummy loops waiting to receive some good instructions, while the remaining part do some useful work. It is easy to realize that is far from the ideal case, and the resulting performance of the program is heavily compromised. Anyway sometimes it will be probably impossible to completely avoid this to happen, so in those cases the best options is to reduce the most you can the portions of code that may result in divergent paths to the shader processor of the same multiprocessor. Note that this doesn't mean you should always avoid conditional statements in your device code. In fact if one conditional statement gives the same result for all the threads launched with a specific kernel, then the performance is not affected, since there is no divergence in the execution path of the different threads. Also, when possible, the nvcc compiler will automatically avoid divergence with an equivalent machine code.

#### 2.3.6 CPU-GPU parallelism

One advantage of the gpgpu that has been extensively used in this project is the ability to concurrently run different instructions on the gpu and on the cpu. In fact when the programmer launches a kernel from the device code using indifferently the C for CUDA or the runtime API, almost all the functions used to interact, under some circumstances, with the GPU are asynchronous. This means that as soon as a memory copy or a kernel launch is requested the algorithm on the cpu can go on, without waiting for the job of the gpu to be completed. All the operations, unless otherwise specified, are still scheduled sequentially by the CUDA driver.

In order to synchronize the host program with the GPU workflow there are specific functions that can be used, both to stop the execution of the host program until the GPU has done all that has been scheduled and to poll the execution state without blocking the host program.

## Chapter 3

# **GTrex** implementation

## 3.1 Introduction

In this chapter I will show the key result of the project: a new GPU accelerated processing engine for TRex. I will start with an overview of the entire engine and of the algorithm that controls the GPU computation, then I will describe the algorithm employed for the core processing tasks, that was already existing in the test project done by Cugola and Margara [6]; finally I will show many other enhancements that optimized the code in terms of performance and features.

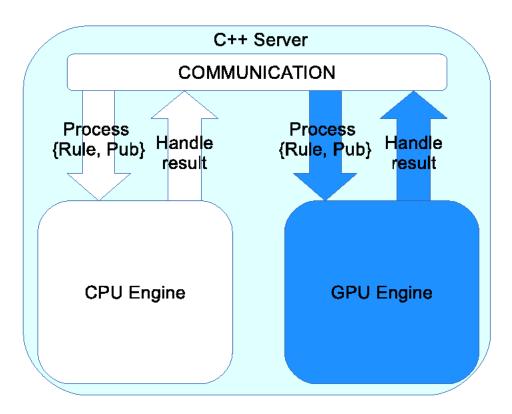

### 3.2 The new server

In the first place it is important to say that this project involved only the engine component of the middleware. In fact the new CUDA powered engine can be installed in the middleware without any modification to the rest of the system, excluding of course some code to actually activate and take advantage of it. So the communication, queue control and management components of the system are exactly as they were before. Using the new engine is as simple as declaring a new GPU Engine and pass to it the rules and event notifications, exactly in the same way done with the CPU engine. Figure 3.1 depicts the new server, where two independent engines are created: one is the old plain CPU engine, the other is the one developed in this thesis. The interface and the interaction between the two engines and the rest of the middleware is exactly the same for both the engines. The main algorithm

Figure 3.1: Overview of the new TRex Server.

employed by this GPU engine is the CDP introduced in CHAPTER 2.

## 3.3 CPU code

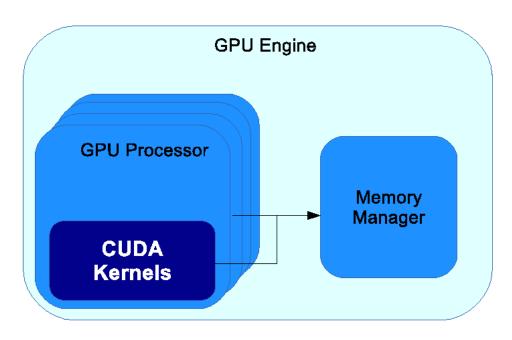

The GPU engine itself is modularized, as shown in FIGURE 3.2: there is a GPUEngine class that is instantiated only once during the initialization of the server of the middleware. The engine then initializes the memory manager; this is also a unique component, that is created once during the initialization of the engine and controls all the GPU memory requested by the program. Then, for each rules installed in the engine, a GPUProcessor is created: it takes care of the management part, that is coordinating the kernels executed on the GPU with rest of the work to be done to make everything work. The GPUProcessor also creates its CudaKernel, that is a class compiled by the NVIDIA CUDA compiler that actually holds the CUDA kernel code and launches computation when requested by the GPUProcessor. When an event notification is received, the GPUEngine passes it to all

Figure 3.2: Overview of the GPU Engine.

its processors, that eventually store it, in case it is relevant for its rule. If the event is a terminator, the real computation that creates new valid sequences is triggered.

The main idea is the one described in algorithm 3.3.1. Note that this code actually runs on the CPU, and only the functions labelled with <> are invocations of GPU kernels.

The computation begins with a single partial sequence containing one event: the terminator. Then the program loops through all the states of the deployed rule (line 2); at each step a new state of the sequence is analyzed to look for new potential events to be added to the partial sequences constructed up to that moment. The switch at line 7 is used to determine the best path to take for the specifications of the state that will be analyzed: the selection policy, the presence of negations and even the size of the kernel to be launched determine which kernel will be used. Moreover the information needed to set up the GPU computation are set by the prepareForNextLoop function. This must be called for the first time before the first round of the loop (line 1), but it is then computed on the CPU while the GPU is busy at line 23 for the following states. Indeed an explicit synchronization with the GPU is requested at line 25, so that, if the CPU ends its part before the GPU, it waits for the results on this blocking call. The number of valid partial sequences found during the computation of a state is read back from the GPU memory at each step (line 24): if it is 0 the computation can be stopped since there won't be any valid complete sequence in any case. There is the risk that the computation performed at line 23 is then thrown away when the GPU returns 0 results (line 27), but since the job is done in parallel this doesn't have consequences on the performance. The partial sequences eventually returned at each loop will be one event longer than those given as input at the beginning of the loop.

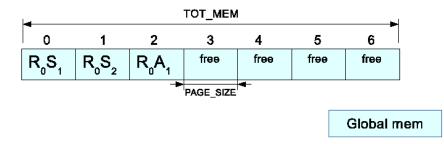

From the algorithm there are also many other aspects worth noting. One interesting aspect is that there is already the usage of the MemoryManager that will be introduced later in this chapter: it is identified by the *mm* pointer, and offers wrappers for memory operations to the GPUProcessors and CudaKernels. In order to identify the calling rule, the *mmToken* is created when one GPUProcessor subscribes to the memory manager, during the initialization phase, and is assigned to the GPUProcessors, that, then, must use it when calling a memory manager method.

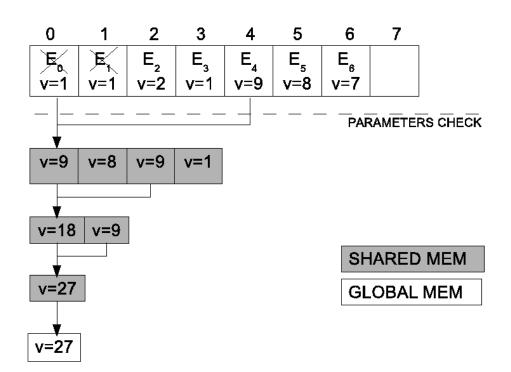

If at the end of the loop resultsSize is a positive number, partialSequences are copied back to the host memory and analyzed to compute their aggregate functions and create the resulting complex events. These resulting sequences are processed sequentially and in order by the CPU, but the aggregate computation is performed by an efficient CUDA reduction kernel, described in SECTION 3.5.3. The creation of complex events instead is left to the CPU, but it is a very easy and light task, and it's also partially overlapped with the GPU execution.

## 3.4 CDP on CUDA

The CDP [seen in SECTION 1.4.2] is the only algorithm that can be efficiently adapted to the CUDA environment, because of its simple data structures and its delayed and parallelizable computation that can be handled by the GPU. The first thing to take care of, though, is that it would be very unefficient to stick with columns of pointers as happened in the CPU implementation. In fact that would cause a memory fragmentation leading to terrible performance on th GPU. As a result in this implementation the

| A         | gorithm 3.3.1: Overview of the handling code        |

|-----------|-----------------------------------------------------|

| 1 l       | oopKind = prepareForNextLoop();                     |

| 2 (       | lescribed foreach state in states do                |

| 3         | cudaMemsetAsync(mm->getResultsSizePtr(mmToken), 0); |

| 4         | if $size = 0$ then                                  |

| 5         | resultsSize $= 0;$                                  |

| 6         | return;                                             |

| 7         | switch loopKind do                                  |

| 8         | case MULTIPLE                                       |

| 9         | computeComplexEventsMultiple()<>;                   |

| 10        | case SINGLE                                         |

| 11        | computeComplexEventsSingle()<>;                     |

| 12        | case MULTIPLENEG                                    |

| 13        | prepareNegationsInfo();                             |

| 14        | computeComplexEventsMultipleWithNegations()<>;      |

| 15        | case SINGLEGLOBAL // SINGLENEG                      |

| 16        | cudaMemsetAsync(mm-                                 |

|           | >getCurrentResultsPtr(mmToken), 0);                 |

| 17        | prepareNegationsInfo();                             |

| 18        | computeComplexEventsSingleG()<>;                    |

| 19        | mm->swapPointers(mmToken);                          |

| 20        | reduceFinal()<>;                                    |

| <b>21</b> | mm->swapPointers(mmToken);                          |

| 22        | if $state > 0$ then                                 |

| 23        | loopKind = prepareForNextLoop();                    |

| <b>24</b> | e = cudaMemcpyAsync(resultsSize,                    |

|           | mm->getResultsSizePtr(mmToken));                    |

| <b>25</b> | cudaDeviceSynchronize();                            |

| <b>26</b> | if $resultsSize == 0$ then                          |

| 27        | return;                                             |

| 28        | else if $resultsSize>0$ then                        |

| 29        | mm->swapPointers(mmToken);                          |

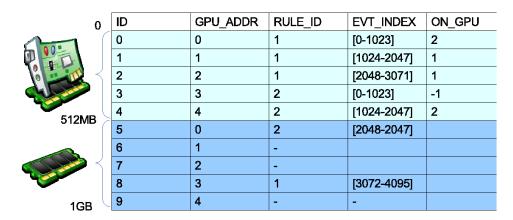

columns hold copies of the events, with their attributes and timestamps. On the other hand the CPU still has to delete old events and set parameters for the CUDA kernels, so the timestamps of the events must be kept also in the host memory. For the sake of simplicity from now on when talking about events on the host memory I am indeed referring to their timestamps, that is the only information actually stored.

When a non terminator event enters the engine the algorithm is similar to the standard version: it still adds the event to the related columns, that are resident on the GPU global memory. When a terminator arrives the program deletes old events analyzing the timestamps on the CPU memory and starts the computation. This is where the CUDA kernels are launched and the main computation takes place. Informations about deleted events, as well as any other information needed to complete the computation, is passed to the CUDA kernel with specific parameters.

As example. remembering the history of events presented in the table 1.1, at time 12 the computation is started; the first two events, with a timestamp lower or equal to 2, are deleted, while the other events are copied to the device memory. At this point the appropriate kernel for the specifications of the given state is launched to analyze the events and find new partial sequences.

Algorithm 3.4.1 shows a simplified kernel for the computation of a multiple selection state without negations.

| Algorithm 3.4.1: CDP Algorithm on GPU, Multiple Selection                                                |

|----------------------------------------------------------------------------------------------------------|

| 1 x = blockIdx.x*blockDim.x+threadIdx.x;                                                                 |

| <b>2</b> y = blockIdx.y;                                                                                 |

| <b>3</b> timestamp = stack[x].timestamp;                                                                 |

| ${\tt 4} \hspace{0.1 cm} {\rm previousTimestamp} = {\rm prevResults[y].infos[referredState].timestamp;}$ |

| 5 valid = (timestamp < previousTimestamp && timestamp >                                                  |

| previousTimestamp-win);                                                                                  |

| 6 if $checkParameters(x, y) == 0$ then                                                                   |

| <b>7</b> valid = 0;                                                                                      |

| s if valid!=0 then                                                                                       |

| 9 writeIndex = atomicAdd(currentIndex, 1);                                                               |

| 10  currentResult[writeIndex].infos[state] = stack[x];                                                   |

| 11 copyPreviousEvents(writeIndex);                                                                       |

| This is the most general form of the algorithm. It doesn't compute                                       |

|                                                                                                          |

negations and it has some simplifications, but the basic idea is there. A 2D grid of CUDA thread blocks is launched, and within each block there is an array of threads. So each thread will have a unique (x,y) pair: x identifies the new primitive event that will be analyzed from the thread, while y identifies the partial sequence found so far that will be checked against the primitive event. The thread performs a check on the timestamps at line 5, on the parameters at line 6, and, if everything matches, it writes the new partial sequence: this will be like the one that the thread used as input with the addition of the primitive event x. The write is done in a dedicated memory area called currentResult, at lines 10-11 of the algorithm.

To do this it uses a special function called atomicAdd (line 9): since all the lines of code are executed in parallel by all the threads within a block, in order to be able to write an ordered output sequence without memory conflicts, some kind of synchronization is needed between threads. This is where atomicAdd comes useful: it increments the variable pointed by the first argument by a quantity specified by the second argument, and it does it so that no other thread can interfere during the operation. Finally it returns the new value, as it is after the addition. This means that, thanks to this function, each thread will have a unique incremental writeIndex used to write without conflicts to the output array.

At the end of the computation the CPU code swaps currentResult and prevResults as seen before, so that the output sequence of a step becomes the input of the next one.

This is the most general form of the algorithm: different code paths have been written in practice, to optimize as much as possible the code produced by the CUDA compiler.

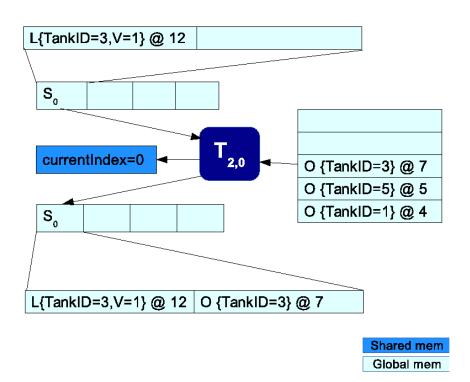

FIGURE 3.3 is an overview of the algorithm and its data structures with the events from table 1.1 at the beginning of the computation at time 12. In the input array of partial sequences there is only the terminator event received, L. In the column for the current state, instead, there are the 3 O events that haven't been deleted. In this case 1 block with 3 threads is launched. These threads will have indexes (0,0), (1,0) and (2,0), where the first number is their index within their block and second number indicates the block in which they reside. Thread (0,0) and thread (1,0) terminate their execution when checking the parameters of the events, since they don't match

Figure 3.3: Algorithm execution example, Multiple Selection.

the TankID attribute of the terminator received. Thread (2,0), instead, will succeed. At this point it will increment the currentIndex variable, reading at the same time the value 0; finally it will write the new valid partial sequence found in position 0 in the output array. If, for example, 2 threads survived the parameters checks and had to write the new partial sequence, one of the two would have found the value 1 in currentIndex and would have written its partial sequence in position 1 in the output array and so on.

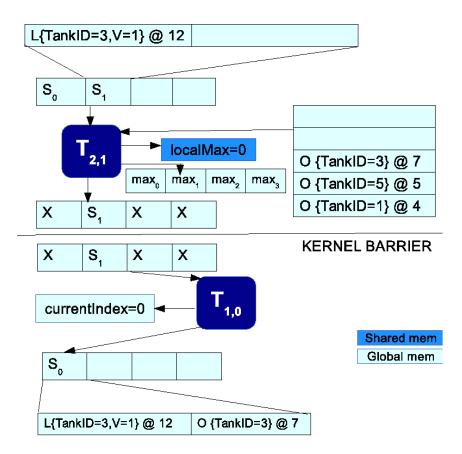

In case of a single selection operator, instead, it is a bit more tricky, as shown in algorithms 3.4.2 and 3.4.3.

The first part of the algorithm is identical to that of the multiple selection case; the differences are all in the code that handles the write of the result to the global memory. Indeed when the single selection policy is used, 1 input partial sequence can be combined with at most 1 simple event from the column; thus many threads will have to compete so that only one, that with the oldest or the newest event from the column, survives and writes its result to the global memory. One important aspect in this version is that the results are not correctly written in an ordered array ready to be copied

| Algorithm 3.4.2: CDP Algorithm on GPU, Single Selection, last-                                                 | -                                                                    |  |  |  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| within                                                                                                         |                                                                      |  |  |  |

| 1 x = blockIdx.x*blockDim.x+threadIdx.x;                                                                       |                                                                      |  |  |  |

| $2 \mathbf{y} = \mathrm{blockIdx.y};$                                                                          |                                                                      |  |  |  |

| <b>3</b> timestamp = stack[x].timestamp;                                                                       |                                                                      |  |  |  |

| 4 previousTimestamp = prevResults[y].infos[referredState].timestamp;                                           | 4 previousTimestamp = prevResults[y].infos[referredState].timestamp; |  |  |  |

| <b>5</b> valid = (timestamp < previousTimestamp && timestamp >                                                 |                                                                      |  |  |  |

| previousTimestamp-win);                                                                                        |                                                                      |  |  |  |

| 6 if $checkParameters(x, y) == 0$ then                                                                         |                                                                      |  |  |  |

| <b>7</b> valid = 0;                                                                                            |                                                                      |  |  |  |

| s if $valid!=0$ then                                                                                           |                                                                      |  |  |  |

| 9 $\operatorname{oldMax} = \operatorname{atomicMax}((\operatorname{int}^*) \& \operatorname{maxIdxlocal}, x);$ |                                                                      |  |  |  |

| 10 if $x < maxIdxlocal$ then                                                                                   |                                                                      |  |  |  |

| 11 return;                                                                                                     |                                                                      |  |  |  |

| 12 $\operatorname{oldMax} = \operatorname{atomicMax}((\operatorname{int} *)\&(\operatorname{maxTS}[y]), x);$   |                                                                      |  |  |  |

| 13threadfence();                                                                                               |                                                                      |  |  |  |

| 14 if $maxTS[y] == x$ then                                                                                     |                                                                      |  |  |  |

| 15 $\operatorname{currentResult}[y].\operatorname{infos}[\operatorname{state}] = \operatorname{stack}[x];$     |                                                                      |  |  |  |

| 16   copyPreviousEvents(writeIndex);                                                                           |                                                                      |  |  |  |

on the host memory as happened in the multiple selection case with a simple atomic instruction. Indeed the atomicMax function is provided by CUDA, but simply using that with the single selection case, when more than one computional block is launched, would lead to wrong results. This is caused by the scheduling of the NVIDIA driver: different blocks don't run in parallel for sure, it depends on many aspects like the physical availability of resources on the GPU chip.

So, using an approach similar to that used in the multiple selection case, it may happen that more than 1 result is considered valid. As example one event could be the last at a certain point of the computation, thus it may be written to the output sequence; but, in a block that still hadn't reached that point of the computation, there may be another event with a greater timestamp: this would be again considered last and written to the output sequence.