## POLITECNICO DI MILANO

## Facoltà di ingegneria dell'Informazione

Corso di Laurea Magistrale in Ingegneria Informatica

Sincronizzazione low-power per reti di sensori wireless tramite controllo lineare decentralizzato: il protocollo FLOPSYNC

RELATORE Chiar.mo Prof. Alberto LEVA

CORRELATORE Ing. Federico TERRANEO

> TESI DI LAUREA DI Luigi RINALDI Matr. 783404

Anno Accademico 2012/2013

#### IERI TI HO GUARDATO

Per la prima volta ieri ti ho guardato con gli occhi del mio tempo più sereno. Eri davanti a me, non t'ho sognato. E la tua voce quasi, la sentivo « tranquillo Enri'... che io non t'ho lasciato». Sentivo così forte il tuo pensiero ed eri dentro me così presente, che col pensiero tuo io c'ho parlato. Papà, oggi la pietà che m'hai insegnato mi rende più leggera la tua assenza e nel frattempo un tempo nuovo nasce: la cognizione di quello che sei stato. L'immensa tenerezza in mi ti vivo e il nuovo padre che sei diventato. Oggi ricordarti non mi affliqqe più. E col tuo aiuto invento la mia vita, a volte mi diverto e faccio divertire. A volte è un vuoto che non so riempire. Io col tuo aiuto canto la mia vita, dove ogni giorno vivi pure tu. E col tuo aiuto capisco un po' di più. Capisco che il tuo ricordo è amore e la memoria la pago col dolore. La lezione del tempo mi è servita, oggi ho capito perché... la vera vita finisce sempre e non è mai finita

Enrico Brignano

## Ringraziamenti

In primo luogo desidero ringraziare il Prof. Alberto Leva per aver reso possibile lo sviluppo di questo lavoro e per avermi fatto crescere professionalmente.

Poi, ringrazio sentitamente l'Ing. Federico Terraneo correlatore di questo lavoro nonché meno amico, sempre pronto a dissipare i miei dubbi.

Ringrazio tutti gli amici di sempre, Christian, Elena, Nazario, Matteo, Lidia, Fabio con cui ho condiviso mille avventure e disavventure durante questi anni in quel di Milano e per essermi sempre stati vicini in ogni momento ed aver riposto in me la loro fiducia.

Un pensiero va anche a tutti i compagni conosciuti in questi anni di università, in particolare Giorgio, per l'aiuto e supporto nell'ultimo periodo.

Per ultima, ma non per questo meno importante, desidero ringraziare le persone che più di altre avrebbero meritato che questo lavoro fosse loro dedicato, la mia famiglia. In particolare ringrazio di cuore mia mamma, mio fratello Francesco, mia sorella Carmela e le mie due grandi gioie: il piccolo Gabriele e l'ultimo arrivato, Samuele. Ad essi va tutta la mia stima, il rispetto e la riconoscenza infinita, nonostante gli screzi e le incomprensioni che inevitabilmente si sono presentati nel corso degli anni. Impossibile poi dimenticarsi degli zii Antonio e Angela, i quali hanno avuto un importante ruolo nella mia educazione e crescita prodigandosi in ogni modo e maniera in loro possesso. Un ringraziamento va inoltre ai miei cugini Francesco e Giuseppe.

## Sommario

La sincronizzazione temporale è importante per il corretto funzionamento di molte applicazioni per reti di sensori wireless (WSN). Per esempio, applicazioni transazionali hanno bisogno di nodi con clock monotoni per evitare che eventi subiscano inversioni temporali, sistemi di gestione del power saving richiedono un overhead minimo di sincronizzazione per consentire il funzionamento a basso duty-cycle, applicazioni che affrontano ambienti estremi devono essere in grado di mantenere la precisione anche in presenza di variazioni termiche impreviste, e così via.

In questa tesi si propone uno schema di sincronizzazione del clock con compensazione di skew/drift per affrontare tutte le questioni sopra accennate. In concreto, la proposta consiste in un protocollo decentralizzato, indipendente dall'hardware, configurabile off-line, in grado di rigettare i disturbi termici, capace di mantenere la monotonia del clock locale ed allo stesso tempo dal basso impatto sulle risorse. Tutto questo è FLOPSYNC, acronimo di Fedback LOw Power SYNChronization, ideato seguendo una metodologia innovativa di progetto che vede la consolidata teoria del controllo applicata ai sistemi informatici.

Si propongono inoltre alcuni studi basati su esperimenti, allo scopo di mostrare la semplicità e l'efficacia del protocollo proposto.

## Indice

| 1        | Intr            | oduzio  | one                                                          | 1  |  |

|----------|-----------------|---------|--------------------------------------------------------------|----|--|

|          | 1.1             | Defini  | zione di una WSN                                             | 2  |  |

|          | 1.2             | Scena   | ri applicativi                                               | 2  |  |

|          | 1.3             | La sin  | cronizzazione nel dominio WSN                                | 4  |  |

|          | 1.4             | Obiet   | tivi e contenuto                                             | 5  |  |

| <b>2</b> | Stato dell'arte |         |                                                              |    |  |

|          | 2.1             | Oscilla | atore al quarzo                                              | 7  |  |

|          |                 | 2.1.1   | Terminologia tecnica                                         | 7  |  |

|          |                 | 2.1.2   | Frequenza di oscillazione                                    | 11 |  |

|          | 2.2             | Notaz   | ione e terminologia                                          | 14 |  |

|          | 2.3             | Tasson  | nomia degli schemi di sincronizzazione                       | 16 |  |

|          | 2.4             | Rasse   | gna della letteratura                                        | 20 |  |

|          |                 | 2.4.1   | Reference Broadcast Synchronization: RBS                     | 20 |  |

|          |                 | 2.4.2   | Timing-sync Protocol for Sensor Network: TPSN                | 21 |  |

|          |                 | 2.4.3   | Delay Measurement Time Synchronization for WSNs: DMTS        | 21 |  |

|          |                 | 2.4.4   | Flooding Synchronization Time Protocol: FTSP                 | 21 |  |

|          |                 | 2.4.5   | Lightweight Tree-based Synchronization: LTS                  | 22 |  |

|          |                 | 2.4.6   | Tiny-Sync e Mini-Sync (TS/MS)                                | 23 |  |

|          |                 | 2.4.7   | Scalable Lightweight Time Synchronization Protocol for WSNs: |    |  |

|          |                 |         | SLTP                                                         | 24 |  |

|          |                 | 2.4.8   | Reference Based, Tree Structured Time Synchronization: TSRT  |    |  |

|          |                 |         | 25                                                           |    |  |

|          |                 | 2.4.9   | Feedback Based Synchonization: FBS                           | 25 |  |

|          | 2.5             | Valuta  | azione dei protocolli di sincronizzazione                    | 26 |  |

|          |                 | 2.5.1   | Valutazione hardware-dependent                               | 27 |  |

|          |                 | 2.5.2   | Valutazione hardware-independent                             | 28 |  |

|          | 2.6             | Motiv   | aziono dolla ricorca                                         | 20 |  |

| 7 | Conclusioni e punti aperti |                                         |                                                                      |           |

|---|----------------------------|-----------------------------------------|----------------------------------------------------------------------|-----------|

| 6 | Mo                         | dello d                                 | lel consumo di potenza                                               | 83        |

|   |                            | 5.3.2                                   | Efficacia del tool di configurazione FLOPSYNC                        | 81        |

|   |                            | 5.3.1                                   | Comparazione tra FLOPSYNC, FTSP e FBS                                |           |

|   | 5.3                        | Comp                                    | ortamento sotto variazioni di temperatura                            | 79        |

|   |                            | 5.2.2                                   | Distribuzione statistica dell'errore di sincronizzazione $\ .\ .\ .$ | 77        |

|   |                            | 5.2.1                                   | Boot del nodo                                                        | 76        |

|   | 5.2                        | Valuta                                  | azione delle performance di FLOPSYNC                                 | 76        |

|   | 5.1                        | Quant                                   | tificazione del jitter indotto dall'hardware                         | 73        |

| 5 | Ris                        | ultati s                                | sperimentali                                                         | <b>73</b> |

|   | 4.6                        | Cenni implementativi del controllore    |                                                                      |           |

|   | 4.5                        | r · · · · · · · · · · · · · · · · · · · |                                                                      | 68        |

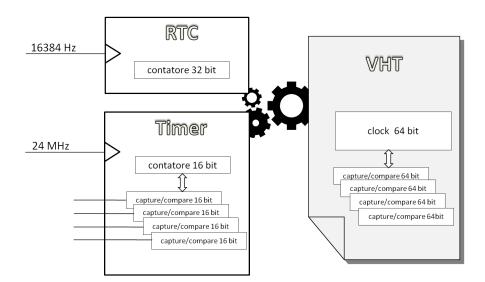

|   |                            | 4.4.3                                   | Il Virtual High resolution Time                                      |           |

|   |                            | 4.4.2                                   | Il Real Time Clock                                                   | 65        |

|   |                            | 4.4.1                                   | Timer: definizione ed uso nei microcontrollori                       | 64        |

|   | 4.4                        | Un'eff                                  | iciente implementazione di timer assoluto                            | 63        |

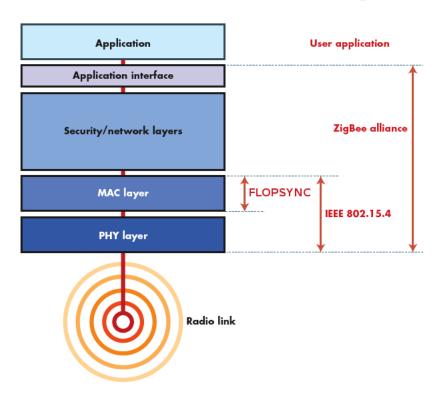

|   | 4.3                        | Il live                                 | llo MAC dello stack radio                                            | 62        |

|   | 4.2                        | Archit                                  | tettura hardware-software di un mote                                 | 58        |

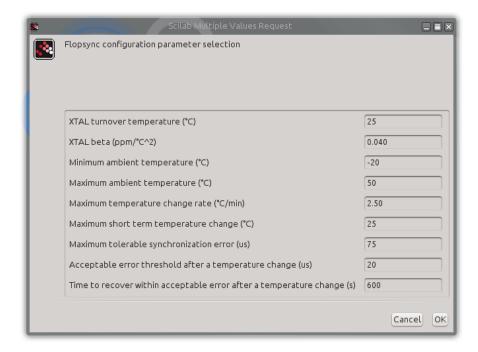

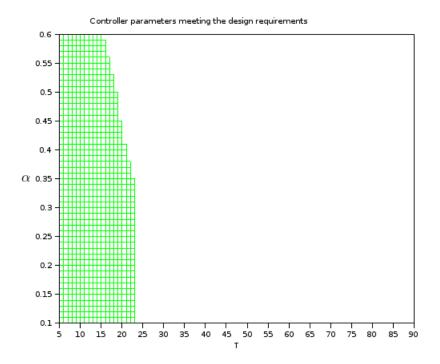

|   | 4.1                        | Tool o                                  | li configurazione per FLOPSYNC                                       | 57        |

| 4 | Imp                        | olemen                                  | tazione                                                              | <b>57</b> |

|   |                            | 3.4.4                                   | Schema di re-sincronizzazione                                        | 55        |

|   |                            | 3.4.3                                   | Clock virtuale                                                       |           |

|   |                            | 3.4.2                                   | Controllore                                                          |           |

|   |                            | 3.4.1                                   | Schema di flooding                                                   |           |

|   | 3.4                        |                                         | tocollo di sincronizzazione FLOPSYNC                                 |           |

|   | 2.4                        | 3.3.1                                   | Un clock virtuale monotono                                           |           |

|   | 3.3                        | -                                       | roblema di controllo allo schema di sincronizzazione                 |           |

|   |                            | 3.2.5                                   | Limitazione dell'errore e taratura del controllore                   |           |

|   |                            | 3.2.4                                   | Criticità dei disturbi di origine termica                            |           |

|   |                            | 3.2.3                                   | Sintesi del controllore                                              |           |

|   |                            | 3.2.2                                   | Analisi del disturbo e modellazione                                  |           |

|   |                            | 3.2.1                                   | Modello del sistema da controllare                                   |           |

|   | 3.2                        | La sin                                  | acronizzazione come problema di controllo                            |           |

|   | 3.1                        | Appro                                   | occio proposto                                                       | 31        |

| 3 | FLO                        | OPSYI                                   | NC                                                                   | 31        |

Bibliografia 91

# Elenco delle figure

| 2.1.1 Orientamento degli assi in un cristallo di quarzo                               | 8  |

|---------------------------------------------------------------------------------------|----|

| 2.1.2 Tipologie di tagli di un quarzo                                                 | 9  |

| 2.1.3 Modalità di vibrazione                                                          | 10 |

| 2.1.4 Circuito elettrico equivalente per un oscillatore al quarzo                     | 10 |

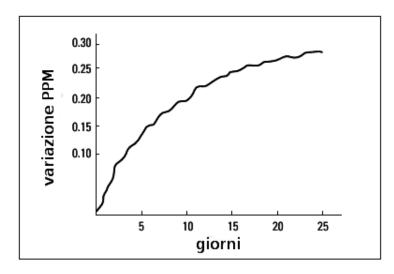

| 2.1.5 Variazioni di frequenza di lungo periodo                                        | 12 |

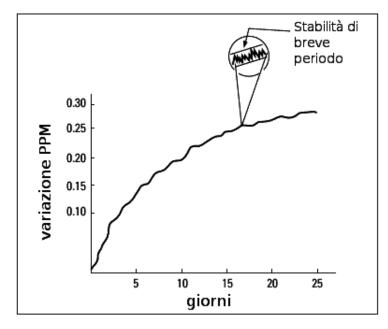

| 2.1.6 Variazione di frequenza di breve periodo                                        | 12 |

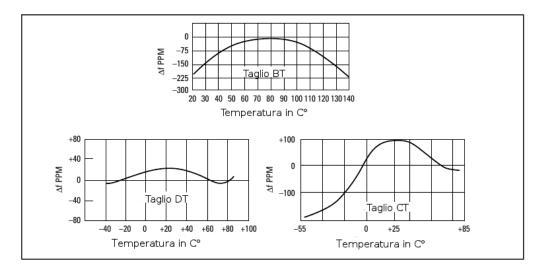

| 2.1.7 Caratteristica frequenza-temperatura al variare dei tagli                       | 13 |

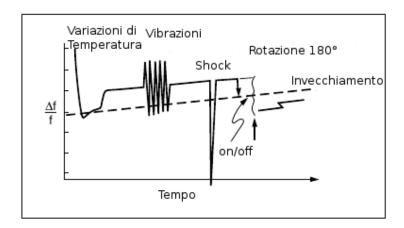

| 2.1.8 Variazioni di breve periodo legate a condizioni ambientali                      | 14 |

| 2.3.1 Tassonomia degli schemi di sincronizzazione in sintesi                          | 19 |

| 2.4.1 Dipendenze lineari e vincoli imposti ad $a_{12}$ e $b_{12}$ con tre data point. | 24 |

| 2.6.1 Errore di sincronizzazione in assenza di meccanismo di compensazione.           | 30 |

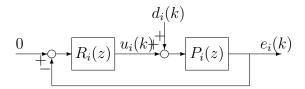

| 3.2.1 Sistema da controllare nel problema base                                        | 33 |

| -                                                                                     | 37 |

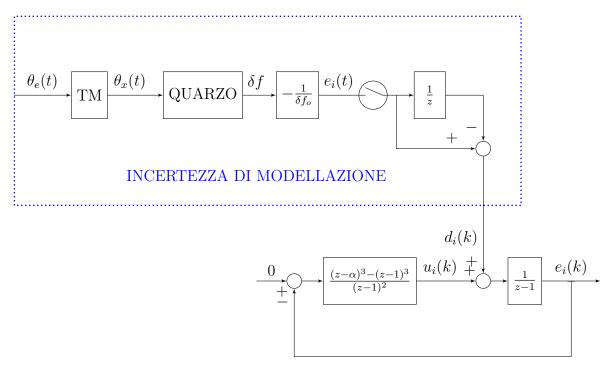

| 3.2.3 Azione della componente termica del disturbo sul controllo. $TM$ in-            | 01 |

| dica il modello termico di equazioni $3.2.27$ , mentre il blocco $QUAR$ -             |    |

|                                                                                       | 41 |

| 1 1                                                                                   | 44 |

|                                                                                       | 44 |

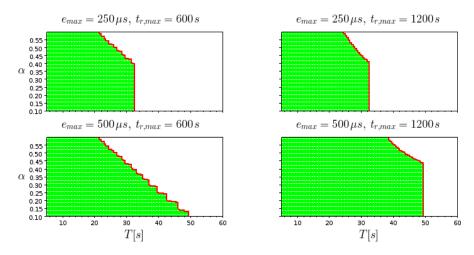

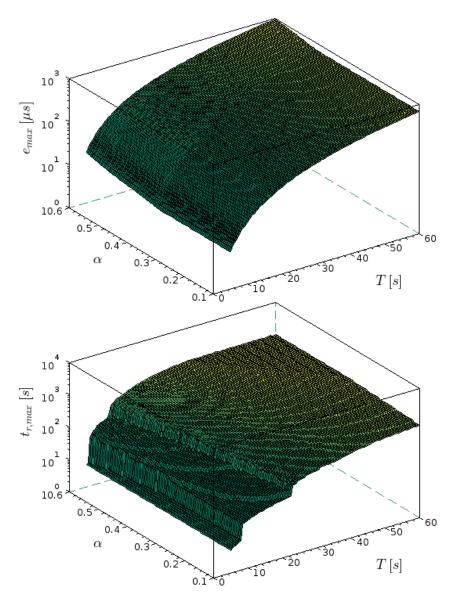

| 3.2.4 Caso 1: errore di picco (sopra) e tempo di recovery (sotto) come                |    |

|                                                                                       | 45 |

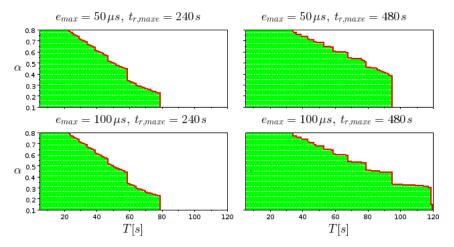

| 3.2.5 Caso 2: errore di picco (sopra) e tempo di recovery (sotto) come                |    |

|                                                                                       | 46 |

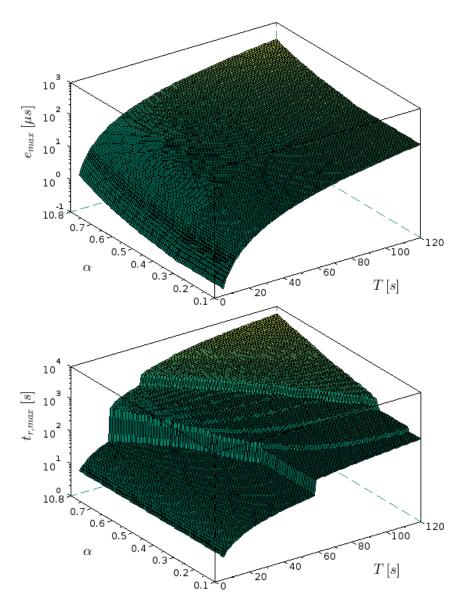

| 3.3.1 Struttura del controllo decentralizzato; $j_i^f(k)$ rappresenta il jitter       |    |

| che ha origine dallo schema di flooding, mentre $XTAL$ e $SW$ rap-                    |    |

| presentano quelli introdotti dal quarzo e dal software                                | 47 |

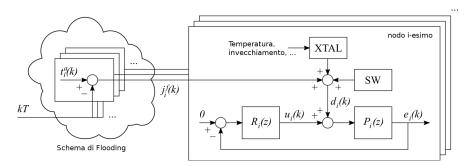

| 3.3.2 Traslazione tra tempo locale e tempo globale con clock virtuale                 |    |

|                                                                                       | 50 |

|                                                                                       | 52 |

|                                                                                       | 53 |

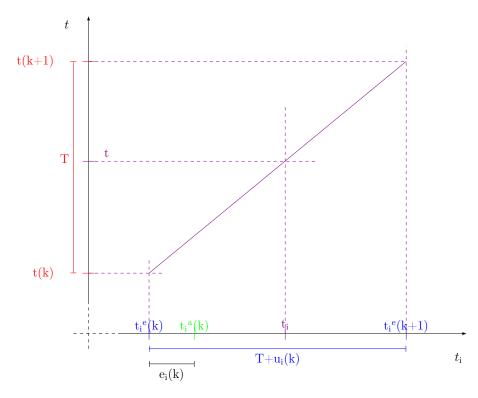

| 4.1.1 | Tool di configurazione per il controllore.                                           | 58 |

|-------|--------------------------------------------------------------------------------------|----|

| 4.1.2 | Output del tool di configurazione riferito alla figura 4.1.1 per la                  |    |

|       | scelta $T$ , $\alpha$                                                                | 59 |

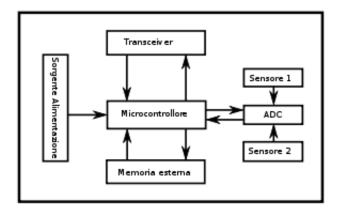

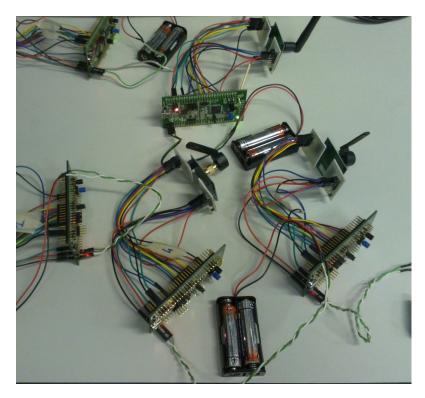

| 4.2.1 | Architettura di un mote                                                              | 59 |

| 4.2.2 | Alcuni mote usati per gli esperimenti.                                               | 61 |

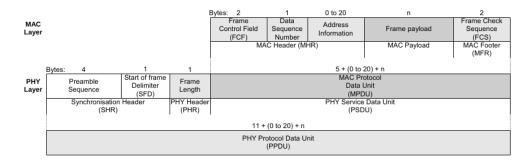

| 4.3.1 | Vista schematizzata del formato del frame IEEE 802.15.4 [1] $\ \ldots \ \ldots$      | 62 |

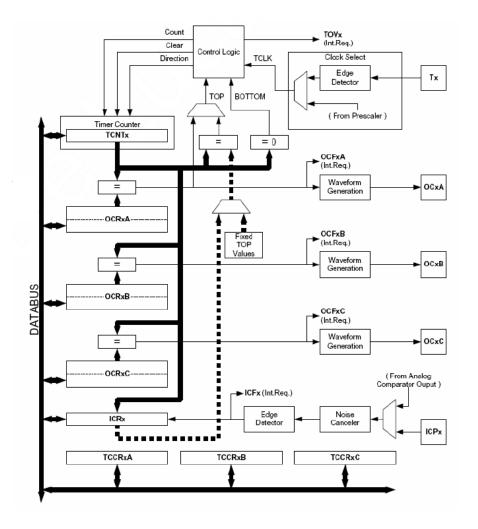

| 4.4.1 | Schema a blocchi di un comune timer da microcontrollore                              | 64 |

| 4.4.2 | Modello del timer                                                                    | 67 |

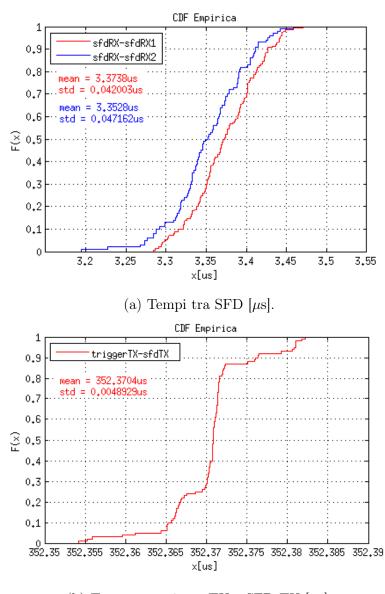

| 5.1.1 | Distribuzioni empiriche cumulative tra i tempi di interrupt del trans-               |    |

|       | ceiver CC2520                                                                        | 75 |

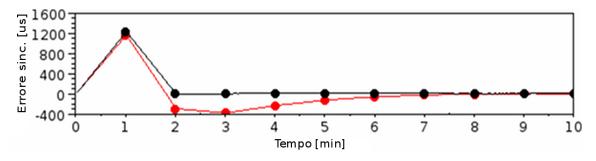

| 5.2.1 | Errore di sincronizzazione durante la fase di boot di FLOPSYNC,                      |    |

|       | con il controllore deadbet (in nero) e senza in (rosso)                              | 76 |

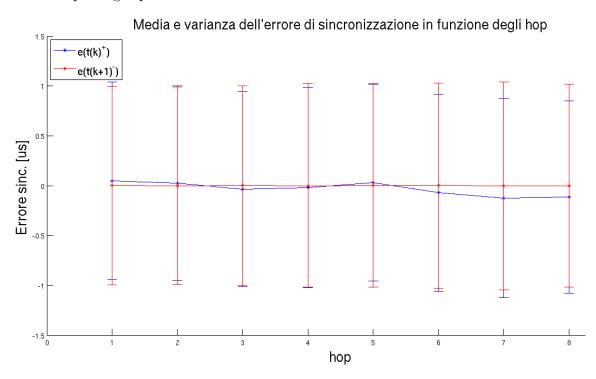

| 5.2.2 | Media e varianza per l'errore un istante prima ed un istante dopo la                 |    |

|       | sincronizzazione, in funzione degli hop                                              | 78 |

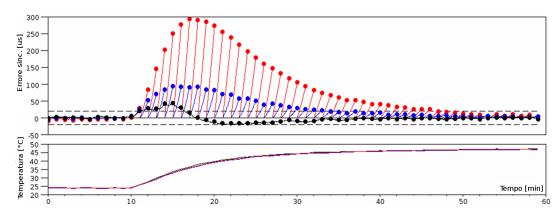

| 5.3.1 | Comparazione tra FLOPSYNC (in nero), FTSP (rosso) e FBS (blu)                        |    |

|       | in una transizione ombra-sole. I punti evidenziano l'errore ad $e_i(t(k+$            |    |

|       | 1) <sup>-</sup> ), mentre le linee mostrano l'errore di sincronizzazione all'interno |    |

|       | di un periodo di sincronizzazione. La linea orizzontale tratteggiata                 |    |

|       | delimita l'area dove l'errore è all'interno di $20\mu s$ . I nodi sono esposti       |    |

|       | al sole al minuto 10                                                                 | 80 |

| 5.3.2 | Errore di sincronizzazione durante una variazione di temperatura                     | 81 |

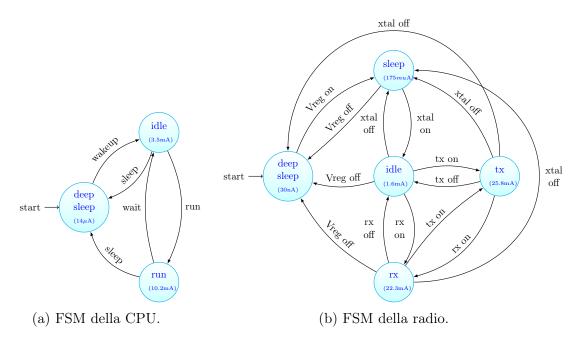

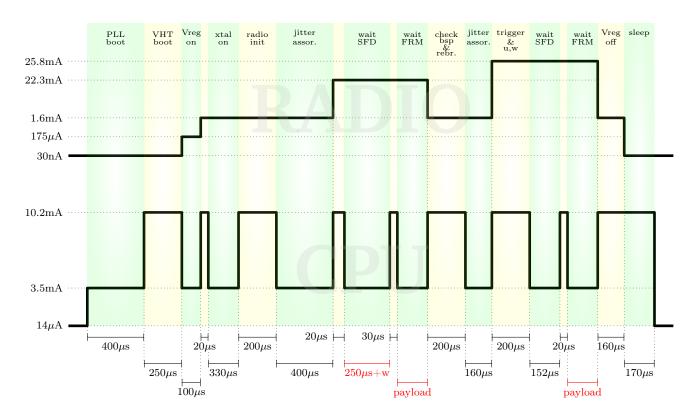

| 6.0.1 | Stati operativi della CPU e della radio                                              | 84 |

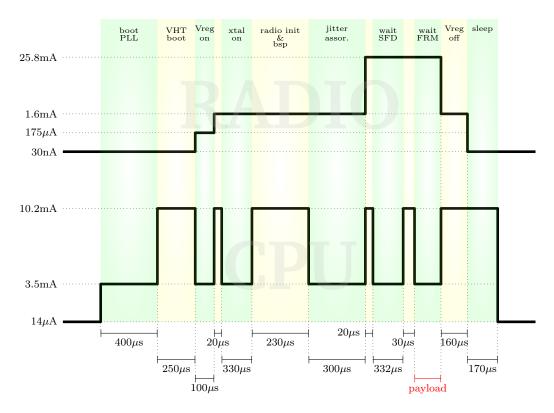

| 6.0.2 | Consumo di corrente tracciato per il nodo reference (non in scala),                  |    |

|       | radio (in alto) e CPU (in basso)                                                     | 85 |

| 6.0.3 | Consumo di corrente tracciato per il nodo non-reference (non in                      |    |

|       | scala), radio (in alto) e CPU (in basso).                                            | 86 |

## Elenco delle tabelle

| 2.1 | Classificazione degli schemi di sincronizzazione                                                                                      | 26 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Comparazione delle performance degli schemi di sincronizzazione.                                                                      |    |

|     | Per la complessità, $n$ indica il numero di nodi, $m$ il numero di sin-                                                               |    |

|     | cronizzazioni, C il numero di cluster head [2], $v$ il numero di vicini                                                               |    |

|     | dati dall'algoritmo spanning-tree e $k$ è una costante che indica il                                                                  |    |

|     | numero di campioni memorizzati per la regressione lineare                                                                             | 29 |

| 3.1 | Specifiche di progetto per il caso 1 ed il caso 2                                                                                     | 44 |

| 4.1 | Comparazione STM32vldiscovery-Telosb                                                                                                  | 60 |

| 5.1 | Media e deviazione standard dell'errore e della finestra di sincronizzazione per un esperimento multi-hop con periodo di 60s e durata |    |

|     | di 6 giorni                                                                                                                           | 77 |

## Capitolo 1

## Introduzione

Il mondo in cui si vive è pieno di sensori. Gli edifici in cui si lavora sono dotati di sensori che monitorano la temperatura, rilevano la presenza di persone, fumo e fuoco e controllano la sicurezza. Le auto contengono dozzine, se non centinaia, di sensori che controllano le prestazioni del motore, i freni, i dispositivi di sicurezza per i passeggeri, solo per citarne alcuni. Negli ultimi decenni i sensori sono diventati molto più piccoli, costano e consumano meno, in parte anche grazie alla legge di Moore e alla rivoluzione dei MEMS<sup>1</sup>. Il costo per la posa dei cavi necessari per l'alimentazione e la trasmissione dei dati è quasi sempre di gran lunga superiore a quello del sensore stesso e non sempre è praticabile.

A partire dagli anni '90, grazie ai notevoli passi in avanti fatti nel campo dei sistemi embedded e alla conseguente diminuzione dei costi dei dispositivi elettronici, è nato e progressivamente cresciuto l'interesse per le reti di sensori wireless (dall'inglese Wireless Sensor Networks WSN). In questi ultimi anni le WSN hanno aperto scenari di utilizzo decisamente innovativi che spaziano dal monitoraggio ambientale alla salute della persona, dalla domotica all'agricoltura e chissà quali e quanti altri utilizzi ci potranno essere in un futuro che si prospetta sempre più "interconnesso". La crescita spasmodica e l'utilizzo piuttosto trasversale e dissimile, rende alquanto appetitoso per la comunità scientifica lo studio delle problematiche inerenti le reti di sensori. Uno tra questi riguarda la sincronizzazione degli orologi in ambito distribuito.

<sup>&</sup>lt;sup>1</sup>La sigla MEMS sta per Micro Electro-Mechanical Systems ed indica quello che la tecnologia del microscopico ha prodotto (si intende quindi che la dimensione media degli oggetti considerati sia di un micrometro), consentendo di rendere la nanotecnologia una realtà.

#### 1.1 Definizione di una WSN

Una WSN è una rete formata da dispositivi piuttosto "semplici", perfettamente autonomi che cooperano nell'esecuzione di una qualche applicazione di raccolta informazioni di un determinato fenomeno fisico. Il termine sensore sta ad indicare un dispositivo che è in grado di tradurre una grandezza fisica in un segnale di natura diversa (tipicamente elettrico) più facilmente misurabile o memorizzabile. Solitamente il segnale originale viene tradotto in una grandezza di tensione o corrente che ne permette l'acquisizione e l'eventuale elaborazione in formato digitale.

Le reti di sensori sono costituite da un insieme di nodi. Ciascun nodo della rete è dotato di uno o più sensori, di un trasmettitore radio (o altro tipo di dispositivo di trasmissione wireless), di un piccolo microcontrollore (che permette l'elaborazione delle informazioni) e infine di una sorgente di energia (tipicamente una batteria). I nodi di una WSN sono spesso impropriamente chiamati sensori, ciò ne evidenzia il fine principale: la rilevazione delle condizioni ambientali dello spazio in cui operano.

Lo sviluppo delle WSN fu originariamente motivato dalle possibili applicazioni in campo militare, come ad esempio la sorveglianza di un campo di battaglia. Tuttavia le reti di sensori hanno trovato ampio spazio in molte applicazioni civili, come monitoraggio di ambienti e abitazioni, applicazioni healthcare, automazione e controllo del traffico. La vasta varietà di sistemi ed applicazioni in cui trovano impiego le WSN, rende difficoltoso discutere su applicazioni specifiche e direzione della ricerca in questo ambito [3].

Le WSN sono caratterizzate da alcuni aspetti chiave come, per esempio, i vincoli di potenza elaborativa, la durata limitata della batteria, un basso dutycycle e connessioni molti-a-uno che creano delle sfide progettuali nell'ambito delle telecomunicazioni.

Il costo di una rete di sensori è variabile. Dipende dal numero di nodi, dalle dimensioni di questi (generalmente più piccoli sono più costano) e dal tipo di sensori montati su ciascun nodo. Altri vincoli legati alla dimensione ed al costo del nodo corrispondono alle quantità di risorse che il nodo dispone, come ad esempio l'energia, la memoria, capacità computazionale e la banda di trasmissione.

## 1.2 Scenari applicativi

Sebbene storicamente il principale utilizzo delle reti di sensori wireless sia stato in campo militare riconducibile alla guerra fredda, oggigiorno è possibile individuare una più vasta area applicativa per questa tecnologia. La principale suddivisione, in termini applicativi delle WSN, dipende dalla presenza di una qualche forma

di retroazione o controllo sull'ambiente stesso, permettendo quindi di distinguere tra applicazioni di monitoraggio ed applicazioni di controllo. Ogni volta che una WSN si occupa della sola raccolta dati, parleremo di applicazione di monitoraggio. Si parlerà invece di controllo quando la rete stessa avrà il compito di interagire in maniera attiva con il fenomeno fisico che stiamo analizzando. Gli utilizzi più diffusi di applicazioni WSN sono:

#### • Ambito militare

- monitoraggio forze nemiche

- monitoraggio forze alleate ed equipaggiamenti

- sorveglianza di campi di battaglia

- tracking di obiettivi

- stima dei danni

- rilevazione di attacchi nucleari e biochimici

#### • Ambito ambientale

- rilevamento di catastrofi naturali

- monitoraggio di microclimi

- agricoltura di precisione

#### • Ambito biomedico:

- monitoraggio a distanza di parametri fisiologici

- tracking di medici e pazienti all'interno di un ospedale

- gestione dei medicinali

#### • Ambito domestico:

- Home Automation

- lettura contatori (Smart Metering)

- sorveglianza

#### • Ambito industriale:

- controllo ambientale in costruzioni industriali ed uffici

- controllo dell'inventario

- tracking di veicoli

- monitoraggio della supplychain

- Ambito dei trasporti:

- monitoraggio del traffico

- sensori intraveicolo

- Ambito automotive

- controllo del veicolo

- infotainment

#### 1.3 La sincronizzazione nel dominio WSN

La sincronizzazione temporale è un elemento critico ed importante per ogni sistema distribuito. Il concetto di tempo deriva da quello più generale che riguarda l'ordine in cui avvengono gli eventi. Per questo, gran parte dei dati raccolti da una rete di sensori non porta alcuna informazione se non accompagnata da un riferimento temporale omogeneo. Molte applicazioni per reti di sensori richiedono che l'orologio locale di ciascun nodo sensore sia sincronizzato secondo vari gradi di precisione.

Le proprietà intrinseche di una rete di sensori come risorse di energia, calcolo, memoria, banda limitata combinate con le alte densità dei nodi della rete rendono i metodi tradizionali di sincronizzazione inadeguati. Gli esistenti metodi di sincronizzazioni necessitano di essere estesi per soddisfare le nuove richieste. Tutto ciò porta ad una continua ricerca di algoritmi specifici di sincronizzazione per reti di sensori.

Da una temporizzazione accurata dipendono applicazioni critiche o servizi della rete stessa, un esempio su tutti il TDMA<sup>2</sup> schedules. Quando l'accesso al mezzo trasmissivo, piuttosto che il meccanismo di power saving sono regolati con la tecnica del TDMA, disporre di un algoritmo di sincronizzazione efficiente diventa il punto cardine per l'ottimizzazione delle risorse del nodo.

Altre applicazioni che richiedono un'elevata accuratezza di sincronizzazione sono quelle di geo-localizzazione. Sebbene il GPS (Global Positioning System) sia un accurato sistema di stima della posizione, purtroppo non si può utilizzare in ambienti indoor poiché usa segnali provenienti da satelliti GPS. Diventa chiaro

$<sup>^2</sup>$ Time Division Multiple Access è una tecnica di multiplazione numerica in cui la condivisione del canale è realizzata mediante ripartizione del tempo di accesso allo stesso.

quindi come una localizzazione accurata e a basso costo sia un requisito critico per un corretto funzionamento di una rete di sensori wireless in ambienti chiusi. Alcune tecniche di localizzazione time based stimano la distanza tra due stazioni misurando il tempo di propagazione del segnale. Per avere un sistema in grado di assicurare una precisione dell'ordine del centimetro occorre essere in grado di rilevare intervalli di tempo dell'ordine delle decine di picosecondi. Oltretutto, è evidente la necessità di una perfetta sincronizzazione tra i dispositivi della rete.

#### 1.4 Obiettivi e contenuto

Nel corso degli anni diverse soluzioni sono state proposte dalla comunità scientifica internazionale al problema della sincronizzazione con i loro pregi e difetti. In questo lavoro viene presentato uno schema innovativo di sincronizzazione per WSN basato su una prospettiva di progettazione avveniristica, denominato FLOPSYNC acronimo di Feedback LOw Power SYNChronization. Si tratta di uno schema significativamente semplice rispetto a quelli ad oggi esistenti, garantisce alta precisione ed un consumo di potenza estremamente ridotto. Con FLOPSYNC viene anche introdotto il concetto di monotonicità temporale, fino ad oggi problematica non solo irrisolta ma addirittura mai menzionata prima d'ora.

Le fasi seguite, al fine di perseguire gli obbiettivi sintetizzati col termine FLOP-SYNC, sono state riprese nell'ordine in cui è stato strutturato l'elaborato di tesi. Pertanto nel capitolo 2 viene proposto al lettore dapprima una rassegna nozionistica sul quarzo, utile a comprendere i fattori che causano l'assenza di sincronia in una WSN, poi viene definita la notazione adottata per il resto del lavoro e infine vengono presentati i lavori più significativi in questo contesto e le motivazioni che hanno portato alla nascita di FLOPSYNC.

Il capitolo 3 è la parte centrale di questa trattazione e ripercorre quelle fasi che potremmo definire studio del problema, modellazione e progettazione.

Nel capitolo 4 dopo una breve presentazione dell'architettura hardware/software su cui FLOPSYNC è stato implementato, si proporranno al lettore brevi frammenti di interessanti soluzioni implementative.

Il capitolo 5 è il frutto dei risultati sperimentali ottenuti dalla valutazione di FLOPSYNC. Verranno ripresi alcuni dei protocolli presentati nello stato dell'arte per la comparazione, a dimostrazione delle migliorie introdotte.

Il capitolo 6 racchiude in se uno dei risultati più importanti raggiunti con questo lavoro: si tratta del consumo di potenza. FLOPSYNC aggiunge un overhead di consumo da essere ritenuto irrisorio.

Infine il capitolo 7 commenta brevemente tutto il lavoro e propone alcuni interessati spunti per il futuro.

## Capitolo 2

## Stato dell'arte

Questo capitolo pone le fondamenta per la comprensione dell'intero lavoro. Verranno illustrate le caratteristiche primarie del quarzo ed i protocolli più significativi ad oggi esistenti. Il lettore in possesso di queste conoscenze è comunque invitato alla lettura delle sezioni seguenti in quanto viene definita la terminologia usata nel resto del presente lavoro. Inoltre viene accennato un confronto tra FLOPSYNC e gli altri protocolli i cui aspetti risulteranno chiari col prosieguo della lettura dei capitoli successivi.

### 2.1 Oscillatore al quarzo

Un oscillatore al quarzo è un circuito elettronico che usa la risonanza meccanica di un cristallo piezoelettrico vibrante per ottenere un segnale elettrico caratterizzato da una frequenza molto precisa. Tipicamente il cristallo utilizzato è il quarzo.

### 2.1.1 Terminologia tecnica

#### Piezoelettricità

La proprietà principale di un cristallo che lo rende usabile come un risonatore prende il nome di piezoelettricità. Il funzionamento di un cristallo piezoelettrico è abbastanza semplice: quando viene applicata una pressione (o decompressione) esterna, si posizionano, sulle facce opposte, cariche di segno opposto. Quindi il cristallo si comporta come un condensatore al quale è stata applicata una differenza di potenziale. Se le due facce vengono collegate ad un circuito esterno, viene generata una corrente elettrica detta corrente piezoelettrica. Al contrario, quando si applica una differenza di potenziale al cristallo, esso si espande o si contrae.

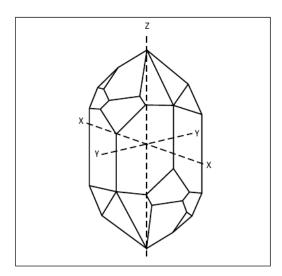

Figura 2.1.1: Orientamento degli assi in un cristallo di quarzo.

#### Struttura del quarzo

Il cristallo di quarzo è formato da silicio e ossigeno (SiO<sub>2</sub>). La sua forma caratteristica è il risultato delle celle unitarie con cui il cristallo cresce. Queste celle unitarie sono identiche e sono costituite da atomi disposti in un disegno geometrico ripetitivo. I cristalli di quarzo hanno un corpo geometrico tridimensionale. La maggior parte delle proprietà fisiche di un cristallo sono anisotropiche (dipendenti dalla direzione), perciò vi saranno imperfezioni nelle fasi di compressione e decompressione del cristallo legate all'anisotropia. Una variazione del coefficiente piezoelettrico, per esempio, crea un confine attraverso il quale il segno della carica differisce quando viene applicata tensione. Questo fenomeno meglio conosciuto come twin boundary, impedisce al pezzo di cristallo di risonare e lo rende inadatto per un oscillatore. Poiché una notevole quantità di lavoro è spesa per fare un buon risonatore al quarzo, questi difetti devono essere rilevati in fase di costruzione. L'orientamento cristallino piuttosto che la presenza di difetti come il twin boundary o fratture vengono rilevati attraverso l'uso di luce polarizzata, raggi X e attacco chimico.

L'asse di maggior crescita del quarzo è chiamato asse ottico. Questo asse non è anisotropo alla luce, quindi la luce passa facilmente. Ai fini del taglio di pezzi di quarzo per agire come risonatori, l'asse ottico è etichettato come l'asse Z in un sistema ortogonale di coordinate X, Y, Z. Un cristallo di quarzo con 6 lati ha tre assi X distinti, tre assi Y definiti attorno all'asse Z distanziati tra loro di circa 120°. Gli assi Y sono perpendicolari alle facce del prisma, mentre gli assi X intersecano gli angoli adiacenti alle facce del prisma (figura 2.1.1).

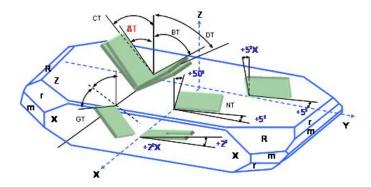

Figura 2.1.2: Tipologie di tagli di un quarzo.

#### Tagli del quarzo

Un opportuno frammento di quarzo viene ottenuto tagliando il cristallo secondo assi ed angoli specifici. La scelta di asse ed angoli determina i parametri fisici ed elettrici per il risonatore. Numerosi tagli possono essere fatti semplicemente cambiando l'angolo e l'asse di riferimento, come mostra la figura 2.1.2.

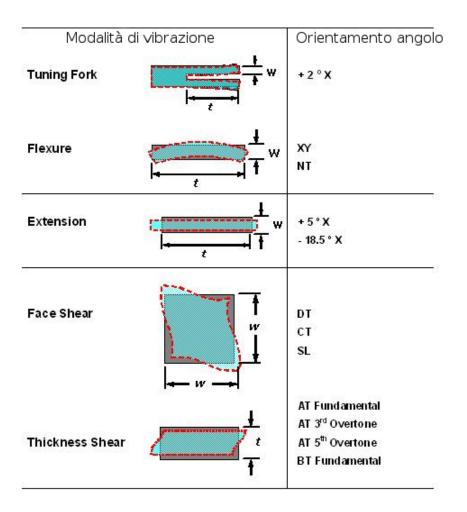

#### Modalità di vibrazione

Quando un cristallo è sottoposto a tensione questo inizia a vibrare. La modalità di vibrazione dipende dal modo in cui il cristallo è stato tagliato e dallo spessore. Varie modalità di vibrazione sono riportate in figura 2.1.3.

#### Montaggio del quarzo

La struttura portante ed i modi utilizzati per ottenere i contatti elettrici sono dettati dalla modalità di vibrazione. Al fine di evitare l'errata vibrazione del cristallo, una cura scrupolosa deve essere esercitata nel montaggio; il sostegno non deve diventare una parte del risonatore poiché potrebbe assorbire energia.

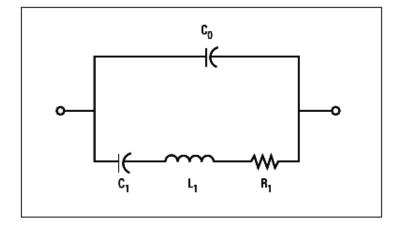

#### Circuito equivalente

Il circuito equivalente di figura 2.1.4 fornisce il collegamento tra le proprietà fisiche di un quarzo e l'area di applicazione, l'oscillatore. Le costanti fisiche del quarzo determinano il valore di  $C_0$ ,  $C_1$ ,  $L_1$ ,  $R_1$ . Un oscillatore al quarzo ha l'ulteriore vantaggio che le sue costanti elastiche e la sua dimensione variano in maniera molto meno sensibile rispetto ad un circuito elettronico.

Figura 2.1.3: Modalità di vibrazione

Figura 2.1.4: Circuito elettrico equivalente per un oscillatore al quarzo.

#### 2.1.2 Frequenza di oscillazione

Il risultato desiderato dal quarzo e dal suo circuito oscillatore associato è la generazione di una frequenza precisa. La frequenza del quarzo, tuttavia, è determinata dallo spessore, densità, elasticità, cambiamenti molecolari, e dalla zona di risonanza su cui la piastra di quarzo è in funzione. Poiché questi fattori sono influenzati da variazioni di temperatura, tempo, energia ed altre condizioni ambientali, è ragionevole aspettarsi che la frequenza di oscillazione del quarzo vari nel tempo.

Un modo utile per caratterizzare la stabilità di un oscillatore è esprimendo la variazione di frequenza rispetto al tempo. La stabilità è generalmente espressa come la quantita di frequenza che cambia nel corso di un periodo di tempo (espressa in parti per milione) e si è soliti distinguere variazioni di lungo periodo e variazioni di breve periodo.

#### Variazioni di lungo periodo

La graduale variazione di frequenza per giorni o mesi è nota come invecchiamento. Questo si verifica per vari motivi, ad esempio, le proprietà fisiche del materiale su cui è montato il cristallo possono cambiare. Il coefficiente di elasticità del cristallo si modifica quando è sottoposto a stress, o quando vi è fuga dei gas intrappolati, o quando contaminazioni attaccano o lasciano la superficie del cristallo. L'invecchiamento si verifica ad un tasso relativamente costante per decade per ogni cristallo (figura 2.1.5). Pertanto, per mantenere una frequenza precisa, periodiche regolazioni devono essere effettuate. Generalmente, la frequenza di un oscillatore può essere variata di qualche ciclo per mezzo di un condensatore regolabile posto in retroazione. Un oscillatore a 10MHz con un campo di regolazione di 20Hz può essere corretto per 75.000 ore (circa 9 o 10 anni) di invecchiamento al tasso di  $5 \times 10^{-10}Hz$  al giorno.

#### Variazioni di breve periodo

Le variazioni di frequenza di breve periodo sono una misura della frequenza o rumore di fase. Questa viene specificata come deviazione standard delle fluttuazioni di frequenza per un tempo medio specifico. Queste piccole variazioni di frequenza sono essenzialmente sovrapposte sulla curva di invecchiamento (figura 2.1.6).

Il maggior responsabile delle variazioni di breve periodo è il range di temperatura al quale il quarzo opera. Un oscillatore posto esattamente alla temperatura di 25°C ed una variazione di frequenza di 5 parti per milione (ppm) per grado Celsius, potrebbe subire uno spostamento di frequenza di 25ppm con l'aumento di soli 5°C di temperatura. La variazione di frequenza è dovuta al coefficiente di

Figura 2.1.5: Variazioni di frequenza di lungo periodo

Figura 2.1.6: Variazione di frequenza di breve periodo

Figura 2.1.7: Caratteristica frequenza-temperatura al variare dei tagli.

temperatura del quarzo e quindi dipende dal taglio del quarzo. Grafici di temperatura rapportati alla variazione di frequenza per vari tagli, sono riportati nella figura 2.1.7. Ovviamente, non è possibile evitare completamente queste variazioni di frequenza se il cristallo deve essere utilizzato in un ampio intervallo di temperatura. Pertanto altre tecniche devono essere utilizzate per ridurre questo effetto, ad esempio tecniche di compensazione.

Oltre che dalla temperatura le variazioni di breve periodo sono influenzate, se pur in misura nettamente inferiore, da:

- variazioni di energia applicata al quarzo,

- orientamento del quarzo sottoposto alla forza gravitazionale,

- interferenze elettromagnetiche,

- esposizione del quarzo a vibrazioni meccaniche,

- shock che provocano uno stress improvviso sul quarzo e ne deformano temporaneamente la struttura di montaggio,

- on/off dell'oscillatore genera un ritmo non constante di invecchiamento.

La figura 2.1.8 riassume i fenomeni ambientali che provocano variazioni di breve periodo.

Figura 2.1.8: Variazioni di breve periodo legate a condizioni ambientali.

## 2.2 Notazione e terminologia

In questa sezione verranno definite le principali notazioni che d'ora in avanti saranno utilizzate per definire e studiare gli aspetti legati alla sincronizzazione.

Denotiamo con t il tempo universale espresso in secondi. Si definisce offset la differenza di tempo espressa in secondi esistente tra due clock ad un dato istante  $(C_A(t) - C_B(t))$  [4]. Per clock si intende un orologio atto a contare il tempo, più precisamente un dispositivo elettronico che conta le oscillazioni di un quarzo che lavora ad una frequenza ben precisa. Il clock di un apparecchio elettronico fondamentalmente è un timer che conta le oscillazioni del quarzo per mezzo di un registro contatore.

Si definisce skew la differenza di frequenza tra due clock, ossia la derivata prima rispetto al tempo dell'offset  $(\dot{C}_{\rm A}(t) - \dot{C}_{\rm B}(t))$ . Clock reali mostrano anche variazioni dello skew rispetto al tempo che pertanto chiameremo drift, ossia la derivata seconda rispetto al tempo dell'offset  $(\ddot{C}_{\rm A}(t) - \ddot{C}_{\rm B}(t))$  [5]. In aggiunta, in questo lavoro occorrerà tener conto delle variazioni di frequenza di breve periodo che chiameremo jitter.

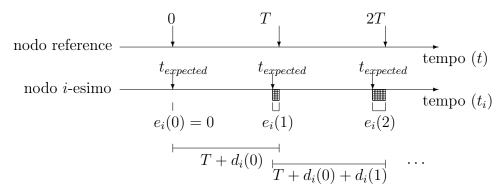

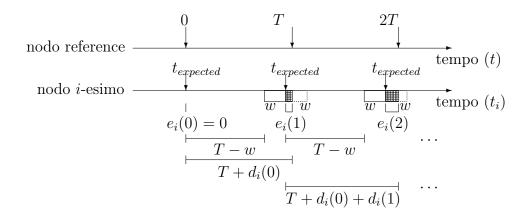

Chiameremo nodo reference il nodo il cui clock sarà da intendersi esatto e costante che definisce il tempo t universale, a cui tutti gli altri nodi i-esimi dovranno sincronizzarsi. Sia poi  $f_o$  la frequenza di targa del clock del nodo reference tipicamente espressa nel datasheet del suo oscillatore al quarzo misurata in Hertz, ed  $f_i(t)$  quella relativa al nodo i-esimo al tempo t. Infine indichiamo con  $t_i(t)$  il tempo locale del nodo i-esimo ed  $o_i(t)$  l'offset del nodo i-esimo, entrambi riferiti all'istante t. Per comodità useremo un indice k da intendersi come multiplo intero di un intervallo di tempo T, dove T rappresenta il periodo di tempo che trascorre tra una sincronizzazione e la precedente. Raggruppiamo ora  $s_i(t)$  e  $j_i(t)$  in un singolo disturbo in frequenza in questo modo:  $\delta_f(t) = s_i(t) + j_i(t)$  cosicché da esprimere l'errore tra clock locale e clock globale al nodo i - esimo come  $e_i(t) = t_i(t) - t$  per cui abbiamo

$$e_i(t) = o_i + \int_0^t \frac{\delta_f(\tau)}{f_o} d\tau \tag{2.2.1}$$

Assumiamo che ad un certo istante t(k) del tempo universale venga eseguito un algoritmo di sincronizzazione per ridurre istantaneamente l'errore  $e_i(t(k)^+)$ , dove il simbolo "+" indica l'errore calcolato un istante dopo la sincronizzazione. Utilizzando la medesima notazione, possiamo calcolare l'errore un istante prima della sincronizzazione come:

$$e_i(t(k+1)^-) = e_i(t(k)^+) + \int_{t(k)}^{t(k+1)} \frac{\delta_f(\tau)}{f_o} d\tau,$$

(2.2.2)

e tale meccanismo che riduce l'errore al tempo  $t(k+1)^-$  sarà chiamato compensazione skew/drift.

Tradizionalmente, la sincronizzazione di clock è realizzata trasmettendo un timestamp dal nodo reference verso tutti gli altri. Tramite un opportuno schema di flooding<sup>1</sup>, si garantisce che i nodi non-reference ricevono il timestamp. Una volta ricevuto il timestamp, i nodi lo impiegano per ricalcolare il loro tempo locale sia con sovrascrittura diretta del clock che senza.

Ai fini della sincronizzazione è di fondamentale importanza considerare anche il *ritardo di trasmissione*, che possiamo definire come il tempo che intercorre tra la generazione del timestamp nel nodo reference e la ricezione del timestamp nel nodo non-reference. Il ritardo di trasmissione si può esprimere come la somma di 5 contributi differenti del segmento di comunicazione:

- 1. ELABORAZIONE DEL SEGNALE D'INVIO, è l'intervallo di tempo impiegato per percorre lo stack radio dal livello più alto di costruzione del messaggio fino a quello di richiesta del canale;

- 2. ACCESSO AL MEZZO TRASMISSIVO, si riferisce al tempo necessario prima che effettivamente il messaggio venga trasmesso. Tale tempo solitamente è dovuto alla contesa del mezzo trasmissivo oppure alla coda di messaggi in attesa di trasmissione:

<sup>&</sup>lt;sup>1</sup>Il flooding è una tecnica comune usata per la ricerca di cammini e per la disseminazione delle informazioni nelle reti ad hoc wireless e wired. Il flooding usa un approccio reattivo dove ogni nodo che riceve un pacchetto di controllo lo rinvia a tutti i suoi vicini.

- 3. TRASMISSIONE DATI, è il tempo necessario per trasmette un pacchetto e può essere facilmente ottenuto dalla conoscenza della lunghezza del messaggio da trasmettere e dal data rate di trasmissione;

- 4. PROPAGAZIONE RADIO, indica il tempo di volo di un messaggio tra due nodi;

- 5. ELABORAZIONE DEL SEGNALE DI RICEZIONE, coincide con il tempo di risalita dello stack architetturale del messaggio, dall'arrivo nel livello fisico al livello più alto.

Indipendentemente dall'efficienza dello schema di flooding utilizzato, piuttosto che dalla precisione con cui viene generato il timestamp [6], il ritardo di trasmissione può essere solo stimato con un certo grado d'incertezza, sia che si usi una rete cablata per la trasmissione sia che si usi una wireless.

Definiamo monotonicità del clock la proprietà di uno schema di sincronizzazione atta a mantenere l'ordinamento tra tempo locale e tempo globale.

Nel resto di questa trattazione l'uso dei termini *schema* e *protocollo* potrebbero apparire agli occhi del lettore come sinonimi, in realtà si vuole indicare con il primo termine solo gli elementi essenziali di un modello di sincronizzazione mentre col secondo l'insieme di regole che governano l'intera sincronizzazione.

## 2.3 Tassonomia degli schemi di sincronizzazione

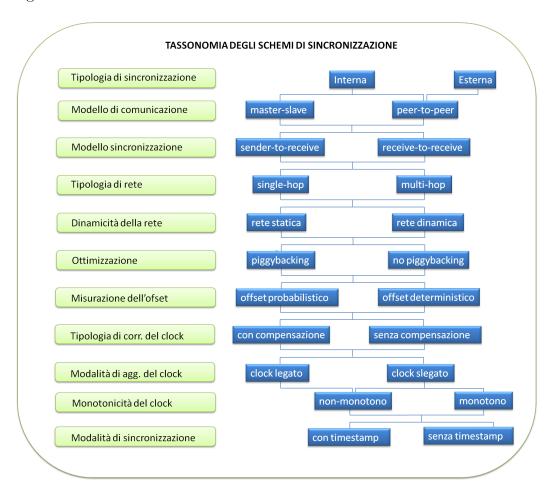

Gli schemi di sincronizzazione per WSN fino ad oggi proposti, possono essere classificati in base ai seguenti criteri [7]:

#### Modello di comunicazione

- master-slave (M-S): un nodo viene definito come master e gli altri come slave. Il clock del nodo master, chiamato anche nodo reference, viene assunto come globale.

- peer-to-peer (P-P): ogni nodo può comunicare direttamente con gli altri nodi presenti nella rete eliminando in questo modo i rischi legati alla caduta del nodo master. Sicuramente più flessibile ma molto più difficile da controllare.

#### Tipologia di sincronizzazione

• interna (I): ha come obbiettivo quello di minimizzare la differenza massima tra il clock dei vari nodi. Può essere fatta sia in master-slave che peer-to-peer.

• esterna (E): esiste una sorgente esterna che fornisce un clock estremamente preciso del mondo reale di riferimento a cui tutti gli altri nodi dovranno sincronizzarsi. Esclude pertanto un modello di comunicazione peer-to-peer.

#### Modello di sincronizzazione

- sender to receiver (S-R): il nodo sender manda periodicamente un messaggio al nodo receiver; quest'ultimo si sincronizza con il nodo sender usando il messaggio ricevuto. Lo svantaggio di questo approccio è l'inconsistenza dei ritardi di trasmissione tra sender e receiver.

- receiver to receiver (R-R): si sfruttano le proprietà broadcast del mezzo fisico assumendo che, se due nodi ricevono lo stesso messaggio in una trasmissione, lo ricevono approssimativamente allo stesso istante. In questo modo il sender invia un messaggio a due receiver e la sincronizzazione viene effettuata considerando la differenza tra i clock locali dei due receiver. Il vantaggio di questo approccio è quello di ridurre le inconsistenze dovute ai ritardi di trasmissione.

#### Topologia di rete

- single-hop (S-H): in una rete single-hop, un nodo sensore può comunicare direttamente e scambiare messaggi con qualsiasi altro sensore nella rete. La rete è spesso troppo grande, rendendo impossibile per ogni nodo sensore scambiare direttamente messaggi con ogni altro nodo.

- multi-hop (M-H): la rete risulta composta fisicamente da più hop, pertanto i nodi possono comunicare solo con i loro "vicini".

#### Dinamicità della rete

- rete statica (RS): una volta dislocati i nodi la topologia della rete nell'ambiente non cambia più.

- rete dinamica (RD): in una rete dinamica i nodi hanno la capacità di "muoversi", e di comunicare con altri sensori solo quando entrano nel range di comunicazione di quest'ultimi. Alcuni schemi richiedono il ricalcolo topologico della rete periodico.

#### Ottimizzazione

- piggybacking (P): offre la possibilità di incapsulare altre informazioni nel pacchetto di sincronizzazione utili ad esempio per fornire informazioni e/o comandi per l'intera rete.

- no piggybaking  $(\neg P)$ : non permette di inviare null'altro che il pacchetto di sincronizzazione.

#### Misurazione dell'offset

- offset probabilistico (OP): il valore dell'offset viene calcolato statisticamente. Un approccio di questo tipo viene utilizzato perché permette al protocollo di sincronizzazione di inviare pochi messaggi e di conseguenza basso utilizzo delle risorse e basso consumo.

- offset deterministico (OD): garantisce un upper bound di clock offset per mezzo di algoritmi deterministici.

#### Tipologia di correzione del clock

- senza compensazione del clock  $(C\neg C)$ : il clock viene corretto solo l'istante dopo la sincronizzazione, per cui l'errore  $e(t(k)^+)$  (ossia un'istante dopo la sincronizzazione) sarà minimo da questo punto in poi tenderà ad aumentare raggiungendo il suo massimo all'istante  $t(k+1)^-$ .

- con compensazione del clock (CC): viene fatta compensazione del clock su tutto il periodo di sincronizzazione con lo scopo di minimizzare l'errore qualsiasi istante di tempo si consideri.

#### Modalità di aggiornamento del clock

- clock legato (CL): il clock locale viene aggiornato a quello globale dopo aver eseguito il processo di sincronizzazione, per mezzo di una sovrascrittura del clock.

- clock slegato (CS): le informazioni per convertire il clock locale in quello globale vengono memorizzate senza sovrascrivere il clock locale.

#### Monotonicità del clock

- $clock\ non-monotono\ (C\neg M)$ : non viene mantenuto un ordinamento tra tempo locale e globale, per cui si potrebbe avere una non corretta collocazione di eventi.

- clock monotono (CM): mantiene l'ordinamento tra tempo locale e globale.

#### Modalità di sincronizzazione

- con timestamp (T): viene utilizzato un meccanismo di sincronizzazione basato su timestamp per eseguire la sincronizzazione tra nodi. I contro sono: maggior utilizzo delle risorse minor precisione dovuta al ritardo di trasmissione.

- $senza\ timestamp\ (\neg T)$ : sfrutta l'invio/ricezione del pacchetto per sincronizzarsi

La figura 2.3.1 riassume la tassonomia.

Figura 2.3.1: Tassonomia degli schemi di sincronizzazione in sintesi.

### 2.4 Rassegna della letteratura

La sincronizzazione temporale in ambito distribuito è una problematica molto sentita nella comunità scientifica e pertanto negli anni diverse soluzioni sono state proposte. Uno dei primi, più diffusi ed avanzati algoritmi in materia è Network Time Protocol (NTP), ideato da Mills[5, 8] nei primi anni Ottanta ed utilizzato per sincronizzare una rete di computer. In NTP i nodi della rete sono sincronizzati ad una sorgente di tempo globale, che è iniettata nella rete attraverso un sottogruppo di nodi master (chiamato "stratum-1" server). Questi nodi master sono sincronizzati direttamente ad una sorgente esterna di tempo come ad esempio un dispositivo GPS (tali dispositivi formano lo "stratum-0"). Tutta la rete è strutturata gerarchicamente a livelli.

Nel 2002 venne introdotto il protocollo IEEE 1588 meglio conosciuto come Precision Time Protocol (PTP)[9] ideato per sistemi locali che richiedono un'accuratezza superiore a quella ottenibile con NTP.

Tuttavia molte delle caratteristiche di una WSN precludono l'utilizzo delle esistenti tecniche di sincronizzazione in questo dominio, dove la problematica della sincronizzazione è resa più ardua per questioni quali la ridotta potenza computazionale dei nodi, il power, l'assenza di moduli particolari come ad esempio il gps, la dinamicità della rete ecc... .

Di seguito verranno illustrate le caratteristiche essenziali dei protocolli più rappresentativi di sincronizzazione per WSN.

### 2.4.1 Reference Broadcast Synchronization: RBS

Uno dei primi algoritmi ideati in materia è stato proposto da Elson, Girod e Estrin[10]. In RBS ogni nodo è normalmente non sincronizzato con il resto della rete. Un nodo segnalatore (beacon node) periodicamente invia in modalità broadcast dei pacchetti di riferimento detti beacon ai nodi all'interno del suo raggio di trasmissione. L'evento di ricezione del pacchetto beacon è utilizzato come riferimento di tempo per la stima di offset e skew dei nodi vicini. Quando un nodo riceve un pacchetto beacon registra il tempo di arrivo del pacchetto effettuando il timestamp in accordo al proprio clock locale. In seguito scambia il proprio timestamp con il resto dei nodi. Ogni nodo utilizza i pacchetti contenenti i timestamp e la regressione lineare per stimare gli offset e drift relativi ai nodi vicini. La cosa interessante di RBS è che registra il timestamp solo nei nodi ricevitori, infatti non interessa il tempo in cui il nodo di riferimento invia il pacchetto beacon. Per cui tutti gli errori di incertezza dal lato trasmettitore sono eliminati. Questa caratte-

ristica rende l'algoritmo particolarmente adatto a tutti quei dispositivi hardware che non forniscono un timestamp a livello MAC. Il meccanismo proposto con RBS può essere facilmente esteso a multi-hop network. Lo svantaggio principale di RBS risulta nel fatto che non si verifica direttamente una sincronizzazione tra nodo trasmettitore e ricevitore dei pacchetti beacon. Inoltre un numero elevato di scambi di messaggi è richiesto per raggiungere la sincronizzazione.

#### 2.4.2 Timing-sync Protocol for Sensor Network: TPSN

Ganeriwal et al. [11] proposero un loro protocollo di sincronizzazione con un approccio innovativo del tipo transmitter-receiver. TPSN è un algoritmo gerarchico suddiviso in due fasi: la prima chiamata level discovery phase e la seconda synchronization phase. Lo scopo della prima fase è quello di costituire una topologia gerarchica della rete, strutturata in livelli. In questa fase ad ogni nodo viene assegnato un livello. Solo ad un nodo viene assegnato il livello 0, questo nodo viene chiamato nodo radice (root node). Nella seconda fase avviene la sincronizzazione della rete secondo la seguente procedura: un nodo del livello i si sincronizza ad un nodo di livello i-1. Alla fine della fase di sincronizzazione, tutti i nodi sono sincronizzati al nodo radice ed in questo modo si raggiunge la sincronizzazione globale della rete.

## 2.4.3 Delay Measurement Time Synchronization for WSNs: DMTS

In DMTS [12] un leader è selezionato come nodo reference e trasmette il suo clock. Tutti i dispositivi che ricevono il timestamp inviato dal nodo reference, correggono il clock con il tempo appena ricevuto aggiungendoci il ritardo di trasmissione. Progettato per avere un basso overhead sulla rete e un basso consumo energetico. L'accuratezza dipende evidentemente dalla misura del ritardo di trasmissione.

## 2.4.4 Flooding Synchronization Time Protocol: FTSP

FTSP [13] può esser utilizzato per sincronizzare un'intera rete e necessita che ogni nodo venga identificato univocamente con un codice ID. Il nodo con ID più basso è eletto nodo radice e serve come sorgente di riferimento del tempo globale della rete. Se questo nodo viene a mancare, il nodo con ID più basso nella rete rimanente viene eletto nuovo nodo radice. Il nodo radice periodicamente inoltra in modalità broadcast un messaggio di sincronizzazione contenente il relativo timestamp di invio. I nodi che non hanno ancora ricevuto questo messaggio, ne registrano il

timestamp contenuto ed il tempo di arrivo in accordo con la loro stima del tempo globale. In seguito aggiornano la propria stima del tempo globale e inoltrano il messaggio ai nodi vicini. Il timestamp è realizzato a livello MAC per minimizzarne i ritardi variabili dovuti ai livelli superiori. Ciascun nodo colleziona otto coppie di timestamp, tempo di arrivo dei messaggi di sincronizzazione e utilizza la regressione lineare di questi punti per stimare la differenza di offset e skew con il nodo radice.

#### 2.4.5 Lightweight Tree-based Synchronization: LTS

LTS [14] è una variazione del protocollo TPSN [11] in cui viene sacrificata la precisione della sincronizzazione per guadagnare in consumo di potenza. Diversamente da molte altre tecniche che tendono alla massima precisione, in LTS le necessità di comunicazione e calcolo per la sincronizzazione del singolo nodo sono state significativamente ridotte traendo vantaggio dal rilassamento del vincolo di accuratezza. Lo schema proposto sacrifica l'accuratezza eseguendo le operazioni di sincronizzazione con minor frequenza e solo tra alcuni nodi. Sono proposti due algoritmi: entrambi assumono l'esistenza di almeno un nodo che abbia accesso ad una sorgente di riferimento di tempo globale.

Nel primo algoritmo si usa un approccio centralizzato multi-hop dove gli aggiornamenti periodici e la sincronizzazione sono gestiti da un nodo radice. La base dell'algoritmo è la costruzione di un albero di coperture (spanning tree)  $\mathcal{T}$  a profondità minima che comprende i nodi della rete. Il nodo radice inizia l'algoritmo sincronizzandosi con tutti i suoi figli in  $\mathcal{T}$  (single-hop) sfruttando il round-trip time² di un messaggio. Successivamente ogni figlio del nodo radice si sincronizza con i propri figli. Questo processo continua finché i nodi foglia di  $\mathcal{T}$  sono stati sincronizzati. Il tempo necessario per un ciclo completo dell'algoritmo è proporzionale alla profondità di  $\mathcal{T}$ . Un nuovo spanning-tree  $\mathcal{T}$  è costruito ogni volta che l'algoritmo viene eseguito. La frequenza di sincronizzazione è calcolata in base alla precisione richiesta, alla profondità dell'albero  $\mathcal{T}$  e al limite di deriva del clock.

Nell'algoritmo decentralizzato multi-hop si usa lo schema distribuito dove i singoli nodi sono responsabili per iniziare ad eseguire la re-sincronizzazione. Nessun tipo di spanning-tree è necessario per dirigere la comunicazioni tra nodi. Quando un nodo necessita di esser sincronizzato, spedisce un messaggio di richiesta al nodo di riferimento più vicino utilizzando un qualsiasi algoritmo di routing. La frequenza di sincronizzazione è calcolata in base all'accuratezza richiesta, alla distanza in numero di hop dal nodo di riferimento ed al drift del clock.

<sup>&</sup>lt;sup>2</sup>E' una misura del tempo impiegato da un pacchetto di dimensione trascurabile per viaggiare da un nodo della rete ad un altro e tornare indietro.

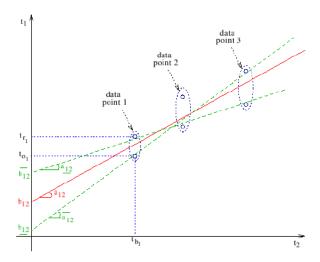

#### 2.4.6 Tiny-Sync e Mini-Sync (TS/MS)

Tiny-Sync e Mini-Sync [15] sono entrambi algoritmi di sincronizzazione che sfruttano la trasmissione di informazioni tra coppie di nodi (pairwise synchronization). Gli autori assumono che ciascun clock può essere approssimato con il seguente modello a frequenza costante:

$$t_i(t) = a_i t + b_i \tag{2.4.1}$$

dove  $a_i$  e  $b_i$  sono drift e offset del clock del nodo i. Considerando due nodi 1 e 2 con i loro rispettivi clock hardware  $t_1(t)$  e  $t_2(t)$  dalla 2.4.1 segue che  $t_1(t)$  e  $t_2(t)$  sono linearmente legati da:

$$t_1(t) = a_{12}t + b_{12} (2.4.2)$$

dove  $a_{12}$  e  $b_{12}$  rappresentano il drift relativo e l'offset relativo tra i due nodi.

Entrambi gli algoritmi usano valori di round-trip time per ottenere stime di offset e drift tra coppie di nodi. La raccolta di tali informazioni (data collection) avviene nel seguente modo: il nodo 1 manda al nodo 2 un messaggio di "probe" e registra l'istante di tale invio corrispondente al tempo  $t_0$ . Quando il nodo 2 riceve il messaggio genera il timestamp  $t_b$  in accordo col proprio clock locale e immediatamente spedisce indietro al nodo 1 un messaggio di risposta contenente tale valore. Alla ricezione della risposta del nodo 2, il nodo 1 registra il timestamp  $t_r$ . Sfruttando l'ordine degli eventi descritti (corrispondenti alla ricezione/trasmissione di un messaggio), i relativi timestamp e la relazione 2.4.2 è possibile ricavare il seguente sistema di disuguaglianze:

$$\begin{cases}

t_0 < a_{12}t_b + b_{12} \\

t_r > a_{12}t_b + b_{12}

\end{cases}$$

(2.4.3)

I tre valori dei timestamp  $(t_0, t_b, t_r)$  formano un data point. Entrambi gli algoritmi lavorano con un gruppo di data point collezionati con lo scambio precedentemente spiegato e permettono di fare un'analisi di drift e offset come rappresentato in figura 2.4.1.

Le linee tratteggiate in figura 2.4.1 soddisfano l'equazione 2.4.2 e rappresentano i vincoli imposti dai data point. Una è la retta con pendenza maggiore e offset minore  $(\overline{a_{12}} \text{ e } \underline{b_{12}})$  mentre l'altra è la retta con pendenza minore e offset maggiore  $(\underline{a_{12}} \text{ e } \overline{b_{12}})$ . Il drift relativo e l'offset relativo di una coppia di nodi sono limitati dalle seguenti disuguaglianze:

Figura 2.4.1: Dipendenze lineari e vincoli imposti ad  $a_{12}$  e  $b_{12}$  con tre data point.

$$\begin{cases} \underline{a_{12}} \le a_{12} \le \overline{a_{12}} \\ \underline{b_{12}} \le b_{12} \le \overline{b_{12}} \end{cases}$$

(2.4.4)

Possiamo dire che più vicini sono i limiti ( $[a_{12} e a_{12}] [b_{12} e b_{12}]$ ), più la stima di offset e drift è buona e la precisione della sincronizzazione è maggiore. In questo modo non possono essere determinati esattamente i valori di offset e drift, ma possono essere ben stimati, e la stima è tanto migliore quanto maggiore è il numero di data point collezionati da un nodo. Ovviamente i limiti di memoria e di computazione dei dispositivi limitano il numero di data point disponibili per nodo. Per questo TinySync e MinySync sfruttano il fatto che non tutti i data point sono utili per la stima. Come possiamo vedere in figura 2.4.1 il data point 2 non ha nessuna influenza sulla stima dei parametri delle disuguaglianze precedenti. Questa analisi è sfruttata in TinySync il quale mantiene in memoria solamente i due data point che danno i migliori bound, tuttavia la stima non è sempre la migliore possibile. MiniSync estende TinySync, infatti esso cerca la soluzione ottima con relativo aumento della complessità dell'algoritmo.

# 2.4.7 Scalable Lightweight Time Synchronization Protocol for WSNs: SLTP

SLTP [2] è orientato al power ed usa la regressione lineare su collezioni di dati per sincronizzare i nodi. E' costituito da due fasi, una prima fase di configurazione per reti statiche e dinamiche in cui viene eletto il gruppo leader e i membri. Una

seconda fase dedicata alla sincronizzazione dei membri della rete.

# 2.4.8 Reference Based, Tree Structured Time Synchronization: TSRT

TSRT [16] si pone come obbiettivo principale quello di minimizzare la complessità di sincronizzazione ponendo come vincolo l'accuratezza di sincronizzazione. Lavora in due fasi: una prima fase costruisce la struttura ad albero topologica della rete e la seconda sincronizza i clock locali e valuta lo stato della rete. Prevede la presenza di un nodo reference (oppure multipli) che periodicamente trasmette un beacon ai sui vicini. A differenza di altri protocolli questo approccio sfrutta la comunicazione multicanale per migliorare la precisione e minimizzare l'overhead di comunicazione e di conseguenza il consumo di energia. In sostanza per evitare collisioni con i nodi vicini (ossia allo stesso hop) nodi dello stesso hop comunicano su canali differenti. Di base utilizza la regressione lineare per la correzione dei clock locali.

#### 2.4.9 Feedback Based Synchonization: FBS

FBS [17] è uno schema di sincronizzazione che si differenzia dai precedenti per l'approccio basato sulla teoria del controllo. A differenza dei precedenti schemi menzionati che eseguono generalmente una compensazione della variazione del clock sul breve periodo modellando il clock come lineare, FBS considera le perturbazioni del clock causate da variazioni di lungo periodo che generalmente gli altri schemi stimano con metodi statistici [10, 18, 19]. Questi solitamente richiedono una grande quantità di dati e potenza computazionale, riflettendosi su consumo di tempo, memoria e risorse che potrebbero andare ben oltre le capacità di un nodo sensore. L'idea che c'è alla base è quella di usare un controllore proporzionale integrale (PI) in anello chiuso per compensare offset/skew del clock locale. Può essere usato anche in multi-hop, in questo caso è necessaria una prima fase, dove viene costruito un albero di coperture (spanning tree)  $\mathcal{T}$  a profondità minima che comprende i nodi della rete.

Concludiamo questa sezione riepilogando con la tabella 2.1 le caratteristiche dei protocolli appena presentati. Si fa presente che pur non avendo ancora descritto FLOPSYNC essso è presente in tabbella, in quanto si vuol dare al lettore un'idea della tipologia di schema proposto in relazioni a quelli esistenti.

|            |        | P-P  | S-R | S-H   | RS   | P vs | OP   | CC         | CS   | С¬М  | Т        |

|------------|--------|------|-----|-------|------|------|------|------------|------|------|----------|

|            | I vs E | vs   | vs  | vs    | vs   | ¬P   | vs   | vs         | vs   | vs   | vs       |

|            |        | M-S  | R-R | М-Н   | RD   | ¬P   | OD   | $C \neg C$ | CL   | CM   | $\neg T$ |

| RBS ('02)  | ~      | P-P  | R-R | S-H   | RS   | ¬P   | OD   | CC         | CS   | С¬М  | Т        |

| TPSN ('03) | ~      | M-S  | S-R | M-H   | RS   | ¬P   | OP   | C¬C        | CL   | C¬M  | т        |

| DMTS ('03) | ~      | M-S  | S-R | M-H   | RS   | Р    | OD   | C¬C        | CL   | C¬M  | т        |

| FTSP ('04) | ~      | M-S  | S-R | M-H   | RD   | P    | OP   | CC         | CL   | C¬M  | Т        |

| LTS ('03)  | ~      | M-S  | S-R | M-H   | RD   | ¬P   | OD   | C¬C        | CL   | C¬M  | Т        |

| TS/MS      | ī      | D.D. | a p |       | D.C. | ¬P   | O.D. | aa         | GT.  | G 14 | т        |

| ('03)      | 1      | P-P  | S-R | M-H   | RS   | ¬₽   | OP   | CC         | CL   | C¬M  | 1        |

| SLTP ('07) | ~      | M-S  | S-R | M-H   | RD   | ¬P   | OP   | CC         | CL   | C¬M  | Т        |

| TSRT ('11) | ~      | M-S  | S-R | M-H   | RD   | ¬P   | OD   | CC         | CL   | C¬M  | Т        |

| FBS ('10)  | E      | M-S  | S-R | M-H   | RD   | ¬P   | OP   | CC         | CL   | C¬M  | т        |

| FLOPSYNC   | E      | MC   | G D | N. 11 | , DD | P    | OP   | - CC       | - CC | CM   |          |

| ('13)      | E      | M-S  | S-R | M-H   | RD   | Р    | OP   | CC         | CS   | CM   | $\neg T$ |

Tabella 2.1: Classificazione degli schemi di sincronizzazione

## 2.5 Valutazione dei protocolli di sincronizzazione

Non è possibile affermare in modo assoluto che uno schema sia nettamente migliore di un altro in ogni possibile applicazione di reti wireless. Piuttosto, è molto probabile che la scelta di un protocollo sarà guidata dalle caratteristiche ed esigenze d'impiego. Per esempio, un protocollo a bassa precisione potrebbe essere appropriato per molte applicazioni di monitoraggio ambientale. Tuttavia, lo stesso protocollo potrebbe essere inusabile in applicazioni come data fusion<sup>3</sup>, TDMA<sup>4</sup> schedules, ecc....

Valutare la bontà di uno schema di sincronizzazione per WSN è un compito piuttosto arduo. Un esempio è rappresentato da quanto accaduto in passato agli autori di TPSN [11] implementando l'algoritmo proposto da RBS [10] per operare un confronto con il loro. Incredibilmente lo stesso algoritmo implementato sulla stessa piattaforma dagli autori TPSN ha raggiunto un errore medio nel caso di single hop di  $29.1\mu s$  contro gli  $11\mu s$  dichiarati da RBS. TPSN pur avendo un errore di  $16.9\mu s$  vinceva il confronto in questa valutazione.

Questo piccolo aneddoto mostra la necessità di definire delle metriche oggettive per la valutazione dei protocolli di sincronizzazione per WSN. Per motivi di chiarezza si dividono i criteri in due classi: hardware-dependent ed hardwareindependent. I primi includono precisione di sincronizzazione e consumo energe-

<sup>&</sup>lt;sup>3</sup>E' il processo di integrazione di molteplici dati e conoscenze che rappresentano lo stesso oggetto del mondo reale in una rappresentazione coerente, precisa e utile.

<sup>&</sup>lt;sup>4</sup>Time Division Multiple Access è una tecnica di multiplazione numerica in cui la condivisione del canale è realizzata mediante ripartizione del tempo di accesso allo stesso.

tico. I restanti comprendono complessità computazionale, tempo di convergenza, scalabilità e tolleranza ai guasti. Nel loro insieme, queste misure forniscono una buona caratterizzazione dell'applicabilità e le prestazioni di ciascun protocollo.

#### 2.5.1 Valutazione hardware-dependent

Questi criteri di valutazione sono fortemente legati all'hardware su cui si decide di implementare lo schema di sincronizzazione, pertanto non è semplice valutare quantitativamente schemi implementati su hardware differenti.

Accuratezza di sincronizzazione: è un valore strettamente legato all'errore di sincronizzazione. Mentre l'errore di sincronizzazione è una funzione del tempo t e si riferisce a ciascun nodo, la precisione della sincronizzazione è un parametro globale riferito a tutta la rete di nodi definito come valore massimo oppure valore medio della precisione istantanea in un intervallo di tempo. Possiamo definire la precisione istantanea p(t), altrimenti nominata come dispersione di gruppo (o group dispersion) in [10], come l'errore massimo di fase tra una qualsiasi coppia di nodi nel seguente modo:

$$p(t) = \max_{ij} \{t_i - t_j\}$$

(2.5.1)

Se per la sincronizzazione ci si riferisce ad una sorgente di riferimento, come può esserlo il nodo reference, allora la precisione di sincronizzazione è data da:

$$p(t) = \max_{i} \{t_i\} \tag{2.5.2}$$

Efficienza energetica: è tra le metriche che hanno più peso nella maggior parte delle applicazioni di reti di sensori. Le ragioni che inducono a richiedere un basso consumo energetico sono legate essenzialmente alla concezione di nodo sensore ed al suo utilizzo. Si ricorda che nella gran parte delle applicazioni ogni sensore ha una riserva d'energia limitata e non rinnovabile e una volta messo in opera, deve lavorare autonomamente; per questo motivo tali dispositivi devono mantenere costantemente i consumi molto bassi in modo da avere un maggior ciclo di vita. In condizioni di lavoro realistiche infatti, è impensabile sostituire le pile di un nodo sensore, sia per motivi di costo che di accessibilità dei nodi stessi, in quanto potenzialmente disposti in ambienti ostili e difficilmente accessibili. La ricarica in loco, sfruttando l'energia presente nell'ambiente, solitamente permette solo bassi livelli di potenza e non è sempre praticabile.

#### 2.5.2 Valutazione hardware-independent

Le seguenti metriche sono facilmente confrontabili tra vari schemi di sincronizzazione indipendentemente dall'hardware su cui sono state implementate.

- Complessità computazionale: esprime la quantità di risorse di calcolo (spazio e tempo) necessarie per eseguire lo schema di sincronizzazione e il numero di messaggi scambiati dal protocollo per eseguire la sincronizzazione.

- Tempo di convergenza: è il tempo necessario per sincronizzare una rete. Un protocollo che richiede lo scambio di un gran numero di messaggi per la sincronizzazione si tradurrà in un tempo di convergenza più lungo. Pertanto ridurre la complessità del messaggio è di vitale importanza per il rapporto costo-efficienza di un protocollo di sincronizzazione per WSN.

- Scalabilità: è intesa come capacità dello schema di adattarsi alle variazioni, sia nel numero di nodi che nella posizione geografica.

- Tolleranza ai guasti: gioca un ruolo importante in quanto il canale wireless è piuttosto soggetto ad errori. La scarsa affidabilità della consegna del messaggio in un mezzo wireless può avere effetti devastanti sul protocollo di sincronizzazione perché essa richiede scambi di più messaggi. Sono comprese in questa metrica anche le questioni riguardanti il guasto del nodo reference in tutti quei protocolli che basano lo schema di sincronizzazione su quest'ultimo.

La tabella 2.2 compara i protocolli finora presentati con i criteri appena stabiliti. Nella colonna della complessità i simboli hanno il seguente significato:

- n, il numero di nodi della rete;

- m, il numero di sincronizzazioni del nodo;

- k è una costante che rappresenta il numero di campioni utilizzati nella regressione lineare per la stima dell'errore futuro;

- v, indica il numero di nodi considerati vicini per un dato nodo dove i vicini vengono definiti utilizzando l'algoritmo di spanning tree.

Come si può notare dalla comparazione, FLOPSYNC ha delle ottime performance rispetto agli altri e le motivazioni verranno spiegate nel corso di questo lavoro. Si noti anche come tutti i protocolli, eccetto FBS e FLOPSYN, che privilegiano la complessità trascurano l'accuratezza. Inoltre quando si parla di accuratezza è bene considerare sia quella un'istante dopo l'evento di sincronizzazione che quella un'istante prima, altrimenti l'informazione potrebbe essere forviante.

|                | Accuratezza |              | Eff.          | Complessità |           |        | Tempo          |                | Toll.  |

|----------------|-------------|--------------|---------------|-------------|-----------|--------|----------------|----------------|--------|

|                | $t(k)^+$    | $t(k+1)^{-}$ | ener.         | Spaziale    | Temporale | Canale | Conv.          | Scal.          | guasti |

| RBS ('02)      | alta        | alta         | alta          | O(n)        | $O(mn^2)$ | m + mn | molto<br>alto  | molto<br>bassa | n/a    |

| TPSN ('03)     | alta        | bassa        | alta          | O(1)        | 4m(n-1)   | m + mn | n/a            | bassa          | n/a    |

| DMTS ('03)     | alta        | bassa        | molto<br>alta | O(1)        | O(1)      | O(m)   | alto           | bassa          | n/a    |

| FTSP ('04)     | alta        | alta         | alta          | O(k)        | 2mn       | O(mn)  | basso          | media          | media  |

| LTS ('03)      | media       | bassa        | bassa         | O(1)        | 4n-2      | 4v     | molto<br>alto  | media          | media  |

| TS ('03)       | alta        | alta         | alta          | O(k)        | 4m(n-1)   | m + mn | alto           | bassa          | n/a    |

| SLTP ('07)     | alta        | alta         | alta          | O(k)        | O(m)      | Cm     | medio          | alta           | alta   |

| TSRT ('11)     | alta        | alta         | bassa         | O(k)        | O(m)      | O(mn)  | alto           | media          | buona  |

| FBS ('10)      | molto alta  | molto alta   | molto<br>alta | O(1)        | O(1)      | O(m)   | basso          | media          | media  |

| FLOPSYNC ('13) | molto alta  | molto alta   | molto<br>alta | O(1)        | O(1)      | O(m)   | molto<br>basso | alta           | buona  |

Tabella 2.2: Comparazione delle performance degli schemi di sincronizzazione. Per la complessità, n indica il numero di nodi, m il numero di sincronizzazioni, C il numero di cluster head [2], v il numero di vicini dati dall'algoritmo spanning-tree e k è una costante che indica il numero di campioni memorizzati per la regressione lineare.

### 2.6 Motivazione della ricerca

Tutti gli schemi di sincronizzazione esistenti ad oggi per WSN (lo si può notare anche dai più esemplificativi presentati in questo capitolo) sfruttano l'invio di timestamp per sincronizzare i clock, ma è abbastanza evidente che il suo utilizzo, eccetto nella fase di boot, è del tutto inutile. La sua informazione è intrinsecamente contenuta nell'arrivo del pacchetto di sincronizzazione, pertanto si potrebbe pensare di rimuovere il timestamp da uno schema di sincronizzazione. La rimozione del timestamp porta con se diversi benefici, si pensi ad esempio a come questo cambiamento si riflette sul ritardo di trasmissione piuttosto che sul power.

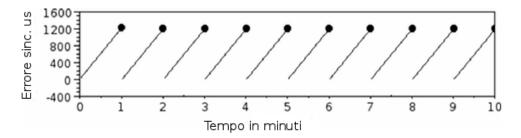

Un'altra questione importante riguarda la necessità di un meccanismo di compensazione skew/drift.

La figura 2.6.1 riporta il risultato di un test fatto su un hardware reale (descritto nel Capitolo 4) che consiste nel tenere sincronizzato il clock di due nodi di una WSN solo tramite sincronizzazione del clock, questo significa inoltrando ogni minuto il timestamp del nodo reference. L'istante successivo alla sincronizzazione, ad esempio  $e_1(t(k)^+)$ , l'errore è ridotto a circa  $1\mu s$ . E' noto che la frequenza degli oscillatori dell'esperimento differisce di circa 20ppm, e infatti come si può notare

Figura 2.6.1: Errore di sincronizzazione in assenza di meccanismo di compensazione.

dalla figura 2.2.1 l'errore un'istante prima della sincronizzazione (rappresentato dai punti,  $e_1(t(k+1)^-)$ ) è di circa 1.82ms. Sebbene sia possibile ridurre questo errore attraverso una sincronizzazione più frequente, l'unico modo per tenerlo il più possibile vicino ad  $e_1(t(k)^+)$  è quello di applicare un meccanismo di compensazione dello skew. Per quanto riguarda la monotonia, le correzioni di clock eseguite possono causare salti all'indietro nel tempo locale, con un'entità nel caso peggiore di 1.182ms ogni minuto.

Si noti che, sebbene la compensazione dello skew riduca l'entità dei salti del clock, questi sono ancora presenti. Ad esempio, drift causati da variazioni di temperatura, o jitter causati da instabilità di frequenza di breve periodo e la non linearità dell'oscillatore [17], possono causare una differenza tra skew atteso e skew attuale, ed il risultato è ancora il manifestarsi di un salto con la sincronizzazione successiva. Quindi, l'unica soluzione robusta è quella di escogitare uno schema di sincronizzazione e di compensazione che garantisca tempi locali monotoni per progettazione.