# POLITECNICO DI MILANO

Scuola di Ingegneria Industriale e dell'Informazione Corso di Laurea Magistrale in Ingegneria Informatica

# Floorplanning Exploration for Partially-Reconfigurable FPGA Systems

Relatore: Prof. Marco Domenico SANTAMBROGIO Correlatore: Dott. Ing. Riccardo CATTANEO

> Tesi di Laurea di: Marco RABOZZI Matricola n. 796810

Anno Accademico 2013–2014

To my family

#### ACKNOWLEDGEMENTS

Several people made this work possible, they gave me inspiration, suggestions, support, precious time, guidance, help and patience.

First of all I want to thank my advisor, Marco Domenico Santambrogio, who encouraged me and stimulated my interest and passion on our work. Without his guidance this thesis would not have been possible. Advice and comments given by Prof. John Lillis, my advisor at UIC, has been a great help in enhancing the work and showing me the right direction to follow.

A thank you also to Fabrizio Spada, Riccardo Cattaneo and Gianluca Durelli for the support and precious help they gave me.

Thank you also to all the people in the NECSTLab at Politecnico di Milano, with whom I spend the working time in a stimulating atmosphere sharing useful suggestions and knowledge.

A thank you to the PoliMi-UIC students of Fall 2013, who shared with me such a great new experience.

Thank you also to Giovanni Riso and Alessandro Riva for all the study hours spent together at Politecnico di Milano.

Last but not least, I would like to express my gratitude to my family and Emilia Maulini for the encouragement they gave me and their patience.

# TABLE OF CONTENTS

#### CHAPTER

## PAGE

| 1        | INTROD                | OUCTION AND MOTIVATIONS             | 1  |  |  |

|----------|-----------------------|-------------------------------------|----|--|--|

|          | 1.1                   | Reconfigurable computing            | 1  |  |  |

|          | 1.2                   | FPGA Technology                     | 4  |  |  |

|          | 1.2.1                 | FPGA overview                       | 4  |  |  |

|          | 1.2.2                 | Reconfiguration characterization    | 6  |  |  |

|          | 1.3                   | Partial dynamic design flow         | 8  |  |  |

|          | 1.0                   |                                     | 0  |  |  |

| <b>2</b> | FLOORPLANNING PROBLEM |                                     |    |  |  |

|          | 2.1                   | Problem description                 | 13 |  |  |

|          | 2.2                   | Complexity                          | 15 |  |  |

|          | 2.2.1                 | VLSI floorplanning problem          | 15 |  |  |

|          | 2.2.2                 | FPGA floorplanning problem          | 16 |  |  |

|          |                       |                                     |    |  |  |

| 3        | STATE C               | OF THE ART                          | 26 |  |  |

|          | 3.1                   | Floorplan representation            | 26 |  |  |

|          | 3.1.1                 | Sequence pair representation        | 30 |  |  |

|          | 3.2                   | Related work                        | 34 |  |  |

|          | 3.2.1                 | Static floorplanners                | 34 |  |  |

|          | 3.2.2                 | Reconfiguration-aware floorplanners | 35 |  |  |

|          | 3.2.3                 | Architecture-aware floorplanners    | 36 |  |  |

|          | 3.3                   | Limits of current approaches        | 38 |  |  |

|          |                       |                                     |    |  |  |

| <b>4</b> | PROPOS                | SED FLOORPLANNER                    | 41 |  |  |

|          | 4.1                   | Device characterization             | 42 |  |  |

|          | 4.1.1                 | Matrix reduction                    | 42 |  |  |

|          | 4.1.2                 | Problem linearization               | 42 |  |  |

|          | 4.1.3                 | FPGA partitioning                   | 43 |  |  |

|          | 4.2                   | MILP model                          | 45 |  |  |

|          | 4.2.1                 | Constants definition                | 46 |  |  |

|          | 4.2.2                 | Variables identification            | 47 |  |  |

|          | 4.2.3                 | Semantic constraints                | 49 |  |  |

|          | 4.2.4                 | Problem constraints                 | 53 |  |  |

|          | 4.2.5                 | Objective function                  | 54 |  |  |

|          | 4.3                   | Formulation refinement              | 58 |  |  |

|          | 4.3.1                 | Resource cuts                       | 59 |  |  |

|          | 4.3.2                 | Geometrical cuts                    | 61 |  |  |

|          | 4.4                   | Model remarks                       | 67 |  |  |

| 5 F | LOORPI               | LANNER EXTENSIONS                                 |  |  |  |

|-----|----------------------|---------------------------------------------------|--|--|--|

| 5.  | 1                    | Support for bitstream relocation                  |  |  |  |

| 5.  | 1.1                  | Problem definition                                |  |  |  |

| 5.  | 1.1.1                | Tile type redefinition                            |  |  |  |

| 5.  | 1.1.2                | Definition of bitstream relocation                |  |  |  |

| 5.  | 1.1.3                | On how to consider bitstream relocation           |  |  |  |

| 5.  | 1.1.4                | Model simplification                              |  |  |  |

| 5.  | 1.1.5                | Revised FPGA partitioning procedure               |  |  |  |

| 5.  | 1.2                  | Relocation as a constraint                        |  |  |  |

| 5.  | 1.2.1                | Constants definition                              |  |  |  |

| 5.  | 1.2.2                | Variables identification and semantic constraints |  |  |  |

| 5.  | 1.2.3                | Bitstream relocation constraints                  |  |  |  |

| 5.  | 1.3                  | Relocation as a metrics                           |  |  |  |

| 5.  | 2                    | Thermal-aware floorplanning                       |  |  |  |

| 5.  | 2.1                  | Problem description and thermal model             |  |  |  |

| 5.  | 2.2                  | MILP extension                                    |  |  |  |

| 5.  | 2.2.1                | Parameters and variables                          |  |  |  |

| 5.  | 2.2.2                | Model constraints                                 |  |  |  |

| 5.  | 2.2.3                | Objective function                                |  |  |  |

| 5.  | 2.3                  | Heuristic approach                                |  |  |  |

| 6 E | EXPERIMENTAL RESULTS |                                                   |  |  |  |

| 6.  | 1                    | Experimental environment                          |  |  |  |

| 6.  | 2                    | Pseudo-random benchmark                           |  |  |  |

| 6.  | 2.1                  | Problems generation and setup                     |  |  |  |

| 6.  | 2.2                  | Results analysis                                  |  |  |  |

| 6.  | 2.3                  | Cost benefit analysis                             |  |  |  |

| 6.  | 3                    | Software defined radio case study                 |  |  |  |

| 6.  | 3.1                  | System design                                     |  |  |  |

| 6.  | 3.2                  | Floorplanner settings                             |  |  |  |

| 6.  | 3.3                  | Results comparison                                |  |  |  |

| 6.  | 3.4                  | Bitstream relocation analysis                     |  |  |  |

| 6.  | 4                    | Evaluation of thermal-aware floorplanning         |  |  |  |

| 6.  | 4.1                  | Tests generation and objective function settings  |  |  |  |

| 6.  | 4.2                  | Results evaluation                                |  |  |  |

| с с | CONCLUSIONS          |                                                   |  |  |  |

| 7.  |                      | SIONS                                             |  |  |  |

| 7.  |                      | Future work                                       |  |  |  |

|     |                      |                                                   |  |  |  |

| С   | ITED LI              | TERATURE                                          |  |  |  |

# LIST OF FIGURES

# FIGURE

# PAGE

| 1  | System reconfiguration                                | 2   |

|----|-------------------------------------------------------|-----|

| 2  | Homogeneous FPGA structure                            | 5   |

| 3  | Heterogeneous FPGA structure and tiles locations      | 9   |

| 4  | Partial reconfiguration design flow                   | 10  |

| 5  | FPGA matrix                                           | 14  |

| 6  | Valid (a) and invalid (b) floorplans                  | 18  |

| 7  | From TSP to floorplanning problem instance            | 21  |

| 8  | Wirelength of different floorplans                    | 23  |

| 9  | Examples of floorplan types                           | 28  |

| 10 | From a floorplan to its sequence pair representation  | 31  |

| 11 | Constraints graphs derived from a sequence pair       | 33  |

| 12 | Variables values of a region placed within the device | 43  |

| 13 | Partitioning of the FPGA into portions                | 45  |

| 14 | Computation of covered resources                      | 48  |

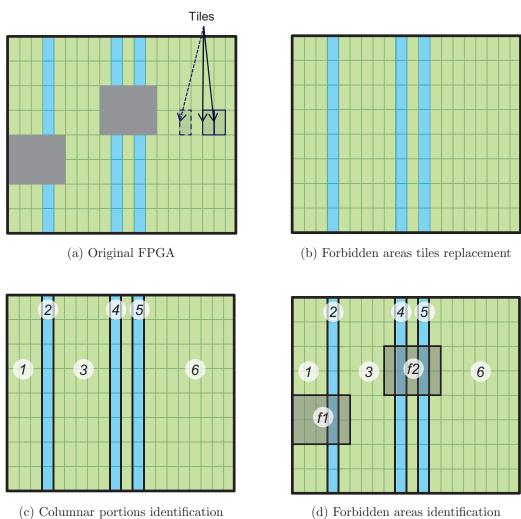

| 15 | Width-height cuts                                     | 65  |

| 16 | Example of compatible and non-compatible areas        | 73  |

| 17 | Columnar partitioning example                         | 79  |

| 18 | Columnar portions offset example                      | 83  |

| 19 | Floorplans comparison on 10 reconfigurable regions    | 105 |

| 20 | Normalized improvement over time overhead             | 106 |

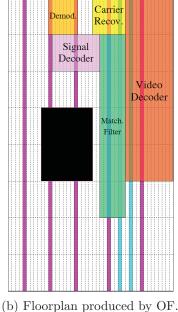

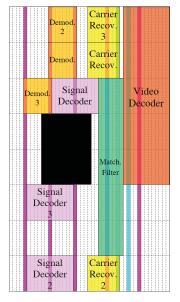

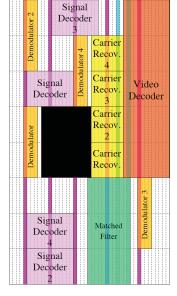

| 21 | Floorplans comparison on the SDR design               | 110 |

| 22 | Bitstream relocation on the SDR design                | 111 |

# LIST OF TABLES

## TABLE

# PAGE

| Ι   | COMPARISON OF STATE-OF-THE-ART FLOORPLANNERS  | 40  |

|-----|-----------------------------------------------|-----|

| II  | RESULTS WITH DIFFERENT NUMBERS OF REGIONS     | 103 |

| III | RESULTS WITH DIFFERENT DEVICE OCCUPANCY       | 104 |

| IV  | RESOURCE REQUIREMENTS FOR THE SDR DESIGN      | 108 |

| V   | THERMAL RESULTS WITH DIFFERENT COST FUNCTIONS | 114 |

| VI  | THF IMPROVEMENT OVER INITIAL SOLUTION AND TOF | 114 |

| VII | FLOORPLANNERS FEATURES                        | 117 |

#### LIST OF ABBREVIATIONS

- 3D-subTCG 3-Dimensional Transitive Closure sub-Graph. ix, 35

- **ASIC** Application-Specific Integrated Circuit. ix, 2, 4

- **BRAM** Block RAM. ix, 5, 13, 34, 38, 44, 107–109

- **CLB** Configurable Logic Block. ix, 4–6, 9, 13, 14, 34, 44, 46, 59, 61, 89, 107–109, 113

- $\mathbf{CMP}$  Chip-MultiProcessor. ix, xi

- CRC Cyclic Redundancy Check. ix, 71

- **DSP** Digital Signal Processor. ix, 5, 13, 34, 38, 44, 46, 59, 107–109

- FDM Finite Difference Method. ix, 90

- **FPGA** Field Programmable Gate Array. ix, xi–xiv, 1–18, 20, 24–26, 29, 30, 33, 34, 37–39, 42–46, 59–64, 70–72, 75, 76, 78–80, 82, 83, 88–90, 107, 109, 113, 115, 116

- **GPP** General-Purpose Processor. ix, 2

- HDL Hardware Description Language. ix, 3, 4, 8, 10

- HOF Heuristic-Optimal Flooplanner. ix, 41, 42, 45, 47, 49, 53, 68, 70, 75, 77, 87, 88, 97, 98, 100–106, 112, 115–118

- HPWL Half-Perimeter Wirelength. ix, 15, 17, 22, 54

- IC Integrated Circuit. ix, 4

- ICAP Internal Configuration Access Port. ix, 3, 12

- IO Input/Output. ix, 2, 40, 54–57, 102, 105, 117

- **IOB** Input/Output Block. ix, 4–6

- ${\bf LCS}$  Longest Common Subsequence. ix, 33

- LP Linear Programming. ix, 59, 69, 75, 101

- ${\bf LUT}$  Look-Up Table. ix, 6

- MILP Mixed-Integer Linear Programming. ix, xii, xiv, 25, 39, 41, 42, 45, 49, 53, 58, 59, 61,

68, 71, 75, 77, 80-82, 88, 91-94, 97, 98, 100-102, 107-109, 112, 113, 115-118

- **OF** Optimal Flooplanner. ix, 41, 42, 45, 47, 49, 53, 54, 67, 68, 70, 75, 77, 87, 88, 91, 93, 96, 97, 99–106, 109, 110, 115–118

- **PR** Partial Reconfiguration. ix, 8, 12, 14, 34–40, 42, 64, 115–117

- **SA** Simulated Annealing. ix, 97–99, 112

- **SDR** Software Defined Radio. ix, 25, 107, 109, 110

- $\mathbf{TCG}$  Transitive Closure subGraph. ix, 35

- THF Thermal Heuristic Flooplanner. ix, 88, 97, 99, 112–114, 116

- **TOF** Thermal Optimal Flooplanner. ix, 88, 91, 97, 112–114, 116

- **TSP** Travelling Salesman Problem. ix, 18–20, 22–24

- VLSI Very Large Scale Integration. ix, 15, 16, 26, 29

#### SUMMARY

The exponential performance improvement achieved by single processors, starting from the early 80s, has slowed down during the last decade. On one hand the power wall was faced, it was no more possible to obtain faster processors simply by augmenting the clock frequency, indeed the power consumption would be too high and cooling with air not feasible. On the other hand the gap between the time needed to access the main memory and the time required by the processor to complete an instruction has steadily increased in the last years.

These issues have led to the advent of Chip-MultiProcessor (CMP) architectures on one side and on a renewed interest in reconfigurable computing on the other. The trends is moving towards heterogeneous architectures in which CMPs and reconfigurable devices such as Field Programmable Gate Array (FPGA) cooperate to achieve effective solutions in terms of both performance and power consumption.

The development of applications able to exploit the capabilities of such heterogeneous systems requires a completely different design flow. The programmer has to deal with a bigger solution space in which hybrid software/hardware solutions can be devised. New challenges arise when some of the tasks of the application are executed in hardware. each task should be mapped to a semantically equivalent circuit, scheduled and floorplanned on the device ensuring the reconfiguration constraints.

This work aims at optimizing the floorplanning on partially-reconfigurable FPGAs taking into account a set of different metrics whose weights can be specified by the designer. We propose a Mixed-Integer Linear Programming (MILP) formulation to solve the problem. Our approach is able to find an optimal floorplan, with respect to the specified set of metrics, while considering the complex structure and heterogeneous resources of modern FPGAs.

The thesis is organized as follows:

- In Chapter 1 we provide a view on reconfigurable computing and describe the design flow for partially-reconfigurable FPGAs;

- In Chapter 2 we present a more detailed description of the floorplanning on FPGAs problem together with a NP-completeness proof;

- Chapter 3 discusses the most important floorplan representations and the state-of-the-art floorplanners;

- Chapter 4 shows the proposed floorplanner and describes its implementation;

- Chapter 5 extends the floorplanner to take into account bitstream relocation and thermal distribution;

- Chapter 6 reports the results obtained with our methodology on a set of problem instances and a real case study;

- In Chapter 7 we discuss the contributions of our approach together with its limits and possible future developments.

#### AMPIO ESTRATTO

La crescita esponenziale delle prestazioni dei processori single core, iniziata nei primi anni 80, ha rallentato durante l'ultimo decennio. Da un lato, sono stati incontrati problemi termici: a causa dei limiti fisici del raffreddamento ad aria non è stato più possibile ottenere processori computazionalmente più veloci aumentando semplicemente la frequenza di clock. Dall'altro lato, il divario tra il tempo necessario per accedere alla memoria centrale ed il tempo richiesto dal processore per completare l'esecuzione di un'istruzione è cresciuto costantemente negli ultimi anni.

Questi problemi hanno portato all'avvento dei processori multi core da un lato e ad un rinnovato interesse per l'hardware riconfigurabile dall'altro. La tendenza è rivolta verso architetture riconfigurabili in cui processori multi core e dispositivi riconfigurabili come le FPGA cooperano per ottenere soluzioni efficaci sia in termini di performance sia in termini di consumo di potenza.

Lo sviluppo di applicazioni in grado di sfruttare le caratteristiche di questi sistemi eterogenei richiede un flusso di progettazione specifico. Il programmatore deve tenere in considerazione un ampio spazio di progetto in cui soluzioni ibride di tipo software/hardware possono essere implementate. Quando alcune delle funzionalità vengono eseguite in hardware sorgono nuove sfide: tali funzionalità devono essere mappate su un circuito semanticamente equivalente, la loro esecuzione deve essere organizzata nel tempo e la loro posizione sul dispositivo deve essere pianificata (floorplanning). Questo lavoro mira ad ottimizzare il floorplanning su FPGA parzialmente riconfigurabili tenendo in considerazione metriche personalizzabili la cui rilevanza può essere definita dal progettista. Viene proposta una formulazione di programmazione lineare mista intera (MILP) per risolvere il problema. Questo approccio consente di pianificare un piazzamento ottimo, rispetto alle metriche specificate, considerando allo stesso tempo la complessa struttura e l'eterogeneità delle risorse delle FPGA più recenti.

La tesi è organizzata come segue:

- Il Capitolo 1 fornisce una breve introduzione sull'hardware riconfigurabile e descrive il flusso di progettazione su FPGA parzialmente riconfigurabili;

- Nel Capitolo 2 viene presentata una descrizione più dettagliata del floorplanning su FPGA insieme ad una dimostrazione di NP-completezza per il problema;

- Il Capitolo 3 discute le più importanti rappresentazioni ed algoritmi utilizzati per il floorplanning nello stato dell'arte;

- Il Capitolo 4 mostra l'approccio proposto in questo lavoro e ne descrive l'implementazione;

- Il Capitolo 5 estende la metodologia per tenere in considerazione il supporto per la rilocazione del bitstream e la distribuzione termica;

- Il Capitolo 6 riporta i risultati ottenuti su diverse istanze sintetiche e su un caso di studio reale;

- Nel Capitolo 7 sono discussi i contributi della metodologia proposta insieme ai sui limiti e possibili sviluppi futuri.

#### CHAPTER 1

#### INTRODUCTION AND MOTIVATIONS

In this chapter we present the context in which our work is developed. Section 1.1 introduces reconfigurable computing and architectures motivating the use of Field Programmable Gate Arrays (FPGAs). Section 1.2 describes the FPGA technology and reconfigurations features of modern devices. The chapter is concluded with Section 1.3 that presents the steps needed to perform partial dynamic reconfiguration on FPGAs, underlining the lack of an automated floorplanner to help the designer in defining the area constraints.

#### 1.1 Reconfigurable computing

The concept of reconfigurable computing is not new, a first proposal of a reconfigurable system was given by Estrin [1] in 1960. The basic scheme of the proposed architecture was a fixed standard processor coupled with an array of reconfigurable hardware, corresponding to the variable part of the system. The idea was to configure the variable part of the architecture to address more effectively the specific type of computation required and, once the computation was performed, to reconfigure the system to solve new tasks. The concept of reconfiguration can be intuitively associated to a change of functionality of a system, however, to be more precise, we report here an interesting formal definition taken from [2]:

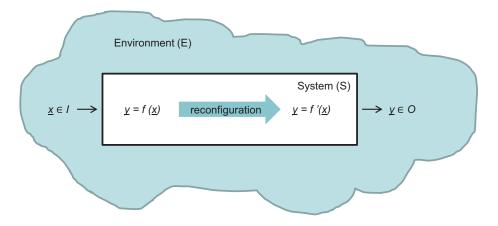

**Definition 1.1.** (Reconfiguration) Given a System S able to interact with the environment E by means of an input set I and an output set O, reconfiguration means changing the current

Figure 1: System reconfiguration

behaviour or functionality  $f: I \to O$  of S to a new functionality  $f': I \to O$  on the same input and output sets.

A simple representation of the given definition is shown in Figure 1.

FPGAs are well suited for reconfigurable systems, since they can be configured on the field after the manufacturing process to achieve the desired hardware functionality. Several reconfigurable architectures are possible exploiting these devices, among which we can have systems consisting of General-Purpose Processors (GPPs) coupled with FPGAs and systemson-chip entirely developed on FPGAs connected through the Input/Output (IO) with only few physical components [2]. Reconfigurable computing combines the features of both software and hardware solutions, it gives the possibility to achieve higher performance than systems entirely based on GPPs, while allowing higher flexibility than Application-Specific Integrated Circuits (ASICs). To better classify different models of reconfiguration, we consider, from [3], the following characterizing features:

- who controls the reconfiguration;

- *when* the configuration is generated;

- what is the level of reconfiguration granularity.

The first subdivision (*who*) distinguishes from systems that completely control and perform the reconfiguration internally to systems in which the reconfiguration is initiated and managed by an external source. When the reconfiguration is controlled and executed within the FPGA boundaries, there must be a specific part of the device that is configured to communicate with an internal reconfiguration interface, such as the Internal Configuration Access Port (ICAP) for Xilinx [4] devices.

The generation of the configurations (*when*) ranges from completely static techniques to fully dynamic ones. Currently, support is given to the creation of configurations at design time, in which all the possible implementations and relative positions of the modules are considered. Once generated, the configurations can be subsequently loaded to reconfigure, even partially [5], the device. Other possibilities rely on adapting or completely generating the configurations dynamically. However, the last approach is currently not feasible due to the high amount of time required to synthesize modules from Hardware Description Languages (HDLs).

The level at which reconfiguration takes place (what) can vary a lot. We can basically distinguish between two different approaches referred as *smallbits* and *module based* [6]. *small*-

*bits* consists in manipulating the single configuration bits of a Configurable Logic Block (CLB) or in modifying the parameters of an Input/Output Block (IOB) within the device. On the other hand, the *module based* technique involves the modification of larger FPGA areas into which different modules or functionalities can be loaded. In the context of this work we are going to consider reconfiguration at module level, following the latest guidelines for partial reconfiguration provided by Xilinx [5].

#### 1.2 FPGA Technology

Within this section, we describe the FPGA technology referring specifically to Xilinx [4] devices, even though the underlining concepts also hold for other vendors such as Altera [7]. In Subsection 1.2.1 we give an overall description of the device structure, while in Subsection 1.2.2 we characterize the device according to the types of allowed reconfiguration.

#### 1.2.1 FPGA overview

An FPGA device is a particular type of Integrated Circuit (IC) whose hardware can be configured to execute a desired functionality. The main property of these devices, is their possibility of being reconfigured an infinite number of times, so that they can adapt to the specific task to solve [8]. The reconfiguration process of the FPGA is conceptually equivalent to realize a new piece of hardware whose specification can be given using a HDL, as done for ASIC.

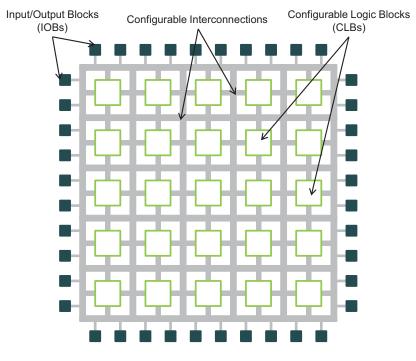

The FPGA architecture can be seen as matrix in which each cell contains a resource. We refer to resources as the basic blocks that can be used to realize our circuit on the device. Depending on the FPGA model there can be different resources and their collocation within the device may differ from one family to another. At least three types of resources are present within the device, namely: CLBs, IOBs and interconnections. An FPGA containing only these types of resources is called homogeneous, while a device containing other resources such as Digital Signal Processors (DSPs), Block RAMs (BRAMs) or multipliers, is defined as heterogeneous. In figure 2 the structure of a homogeneous FPGA is represented.

Figure 2: Homogeneous FPGA structure

CLBs are the main components of the FPGA and are subdivided into slices [9]. Each slice in turn, contains different components, among which we usually have Look-Up Tables (LUTs), latches and multiplexers. LUTs are used to implement custom combinatorial functions and, depending on the device, a LUT can have 4 inputs and 1 output or also have 6 inputs and 2 outputs. The key property of a LUT is that its output values can be configured for each combination of the inputs.

IOBs are usually located at the boundary of the chip and they are needed to perform input/output communications from and to the other peripherals connected to the FPGA. IOBs can be configured to select the desired operating voltage and the direction of the communication, while the interconnections can be configured to route the signals among CLBs and to connect them to the IOBs.

#### 1.2.2 Reconfiguration characterization

In order to configure the desired interconnections and functionalities, a configuration memory integrated into the FPGA is used. A bit contained within a specified address in the memory is in a one-to-one correspondence to the underlining resource being configured, while the file that contains the configuration data that is loaded into the configuration memory is called *bitstream*. The configuration memory is organized into frames, that are the minimal configuration units that can be addressed [5]. With respect to the matrix organization of CLBs resources, each frame can span multiple CLBs height, while multiple frames are needed on the horizontal direction to fully configure a CLB. Depending on the FPGA technology different types of reconfiguration are possible [8], a simple taxonomy is obtained using the following two different features:

- execution requirements;

- reconfiguration size.

With execution requirements we mean the prerequisites to perform a reconfiguration with respect to the current execution status of the device. If we must interrupt the current FPGA execution and reboot the device to load a new bitstream in the configuration memory, the reconfiguration is called *static*. On the other hand, if there are no temporal requirements and we are allowed the load a bitstream even when the FPGA is executing a task, we have *dynamic* reconfiguration. The reconfiguration size refers to the least amount of area that can be reconfigured at once. If the reconfiguration process requires to load a bitstream characterizing the overall FPGA device, the reconfiguration is called *complete*. Whereas, if we are allowed to reconfigure a subset of the configuration memory, we have *partial* reconfiguration and a portion of the device can be reconfigured using a partial bitstream.

In case of partial reconfiguration, we can have a further classification based on the dimension at which reconfiguration is performed [8]. If complete columns of the device must be reconfigured, the reconfiguration is 1D-partial, because we only have a degree of freedom on the horizontal direction. Otherwise, if we are also allowed to reconfigure parts of the columns and describe rectangular regions, the reconfiguration is 2D-partial thanks to the added degree of freedom on the vertical direction. The work developed in this thesis addresses the most general type of reconfiguration: 2D-partial dynamic reconfiguration for FPGAs with heterogeneous resources. Partial dynamic reconfiguration has the great benefit of giving the designer the possibility to change part of the functionalities of the FPGA without interrupting and compromising the execution of other tasks.

#### 1.3 Partial dynamic design flow

In this section we describe, within the context of Xilinx devices, a simplified version of the design flow for FPGAs supporting partial dynamic reconfiguration [5].

The description of a design targeted for FPGAs is suitably given with an HDL such as VHDL or Verilog together with a set of constraints defining the prerequisites for the project. When Partial Reconfiguration (PR) is considered, the designer has to specify the description of each of the modules that has to be reconfigured onto the device. In a PR design it is possible to identify two types of logic, namely: *static logic* and *reconfigurable logic*. Static logic refers to the logic on the device that, once configured, is never changed, whereas the reconfigurable logic can be modified across different reconfigurable logic must lie in different separated areas of the device [5]. The reconfigurable logic in turns can be divided into several reconfigurable regions, while each reconfigurable region can host a specific set of tasks that are reconfigured one at a time by loading the corresponding partial bitstream on the FPGA. Xilinx also strongly recommends to define rectangular reconfigurable regions that include complete tiles to avoid performance degradation when the overall system is deployed. A tile consists of several adjacent configurable frames containing complete resources and is referred as a reconfigurable frame or minimal reconfigurable unit within [5]. To clarify the notion of tiles, we underline them in Figure 3 where an heterogeneous FPGA having frames spanning 4 CLBs height is considered.

Figure 3: Heterogeneous FPGA structure and tiles locations

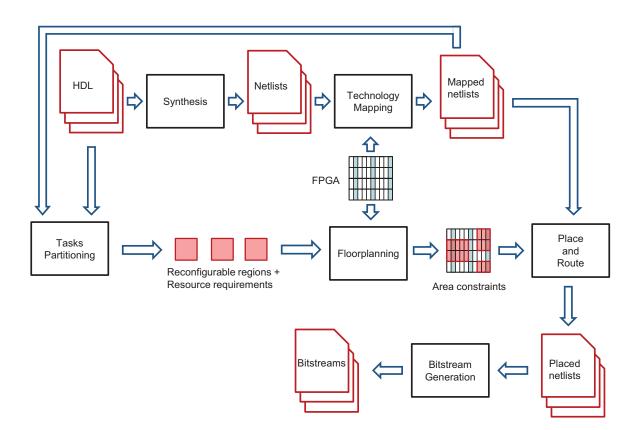

The overall design flow intended for partially-reconfigurable FPGA devices is represented in Figure 4. As a first step, the designer is required to provide a functional description of all

Figure 4: Partial reconfiguration design flow

the tasks or modules by means of HDL, that is subsequently synthesized to produce a set of netlists. The synthesis translates the functional description of the system into a set of basic components, such as logic ports and flip-flops, among which interconnections are established.

A further refinement of the netlists is performed during technology mapping, here the basic components involved in the netlists are logically mapped to the resources available on the target FPGA and we are provided with the numbers of device resources required by each netlist. Exploiting this last information, the designer can decide how to partition the tasks into reconfigurable regions, so that eventually each reconfigurable region is characterized by the resource requirements of the tasks assigned to it.

The area constraints for the design are derived from the floorplanning step that is manually performed by the user. The reconfigurable regions must cover enough resources to meet the requirements of the tasks being reconfigured over time. Since the shape of a reconfigurable region cannot be modified during the execution of the system, the area of the region must be chosen large enough to accommodate the maximum number of resources used by the assigned tasks.

At this point, both the area constraints and the mapped netlists can be given as input to the place and route phase. Here each mapped netlist is placed onto the FPGA and signals among different components are routed. This step is aware of the definition of the reconfigurable regions, thus the placement is performed so that the area constraints are not violated. The final step of the flow produces the partial bitstreams associated to the reconfigurable regions and a complete bitstream for the configuration of the static logic and tasks initially present within the reconfigurable regions. The communication between reconfigurable regions and static logic is guaranteed by the insertion of proxy logic that is automatically generated by the tools within the design flow. Proxy logic remains fixed during the reconfiguration of the regions and all the tasks implemented in the same region must have the same connections to the proxy logic to avoid dangling wires. Once the bitstreams are obtained, they can be loaded onto the FPGA by means of the JTAG port and possibly using ICAP for subsequent partial reconfigurations. The ICAP has to be inserted in the static logic of the system and allows the chip to reconfigure itself. On the other hand, the JTAG port can be accessed externally to reconfigure parts of the system and it is more suitable for debugging.

Notice that the overall design flow presented here is not meant to be followed sequentially, indeed during each step of the flow, the designer is warned about possible not satisfied project constraints such as timing closures. Thus, the design can be interrupted at any point and previous phases may be re-executed taking into account the feedbacks received. Further, during synthesis, technology mapping, place and route phases several optimization parameters can be set to drive the deployment of the system.

Floorplanning is a critical step of the design flow, since the designer as to take into account several constraints while trying to achieve a good device area subdivision manually. In our work, we propose a fully automated floorplanner, able to take into account the PR constraints, while searching for optimal solutions with respect to a customizable objective function. A first version of our work has been published as a full paper for the 22nd IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM) conference [10], while the thermal-aware extension presented in Section 5.2 has been accepted as an interactive presentation for the Design, Automation and Test in Europe (DATE) 2015 conference [11].

#### CHAPTER 2

#### FLOORPLANNING PROBLEM

In this chapter we present a detailed description of the floorplanning problem and prove its complexity class. First, in Section 2.1, we specifically consider and describe floorplanning for partially-reconfigurable FPGAs having heterogeneous resources. Then, within Section 2.2, we compare it to other related problems whose complexity classes are already known and we conclude the chapter proving that the decisional version of the floorplanning problem is NPcomplete.

#### 2.1 Problem description

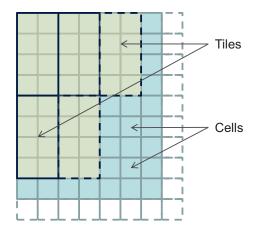

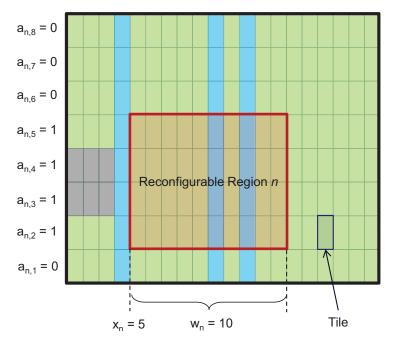

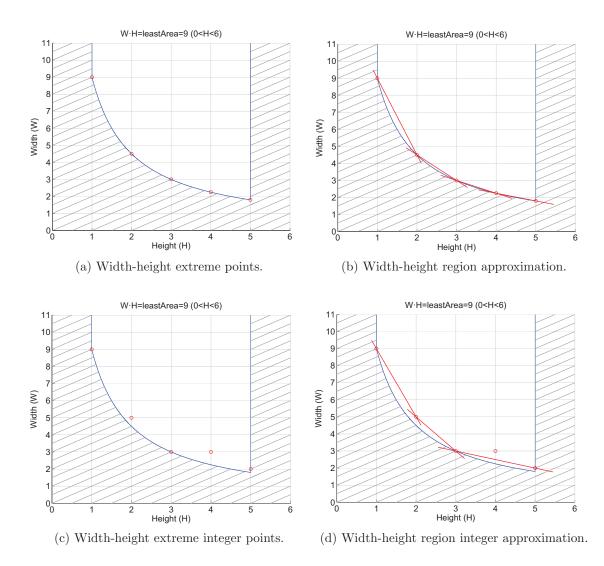

The floorplanning problem is defined by means of a set of reconfigurable regions with their resource requirements (i.e., number of DSPs, BRAMs, CLBs, ...), the desired FPGA device and the objective function that needs to be optimized. The FPGA can be seen as a matrix where each cell, described by its integer coordinates, contains one, none or more than one resource. To fix the notion of a cell, we can consider it as spanning 1 CLB resource width and 1 CLB resource height on the FPGA device. Moreover, since we are interested in reconfiguring regions of the FPGA, we also have to consider the technological constraints of the specific circuit when partial reconfiguration takes place. The reconfiguration process involves a minimal reconfiguration unit, called tile, that is a rectangle including several cells. Figure 5 shows an example of a FPGA matrix structure in terms of cells and tiles.

Figure 5: FPGA matrix

A solution to the floorplanning problem gives, for each region, the coordinates of the bottom left corner, the width and the height with respect to the device matrix. A valid solution of the problem must ensure that (i) for each region, all resource requirements are satisfied (ii) there is no overlapping between two different regions (iii) the regions are placed into rectangular areas of the FPGA that include complete tiles to ease the place and route process [5] (PR requirement). The latter constraint avoid incomplete tile boundaries, that would require extra circuitry and increased latency to modify, read and write configuration information [12]. Depending on the device, a tile has a different size in terms of CLB resources (on a Xilinx [4] Virtex-5 XC5VLX110T it spans 20 CLBs height and 1 CLB width). The width and height of a tile are respectively denoted by tileW and tileH.

#### 2.2 Complexity

Even though floorplanning for partially-reconfigurable heterogeneous FPGAs may resemble floorplanning for Very Large Scale Integration (VLSI) circuits [13], the two problems are different. We discuss how the two problems are related and prove that the decisional version of the FPGA floorplanning problem is NP-complete in the general case.

#### 2.2.1 VLSI floorplanning problem

In VLSI floorplanning we are given a set of modules described in terms of rectangles with fixed size, or having some constraints on the aspect ratio, that have to be packed optimizing the overall area occupancy and the overall wirelength. A common technique used to estimate the wirelength between two modules is to use the Half-Perimeter Wirelength (HPWL). HPWL is computed as the product of the Manhattan distance between the modules centroids multiplied by the interconnection width. If needed, it is also possible to add the constraint that the resulting modules packing cannot exceed a fixed-outline due to a fixed chip size. A simplified decision problem of the fixed-outline floorplanning can be stated as follows:

**Problem 2.1.** (VLSI fixed-outline floorplanning) Given M modules with fixed rectangular shapes, decide if it is possible to pack all the rectangles in a bounding box of height H and width W, such that no two rectangles overlap.

This problem has been shown to be NP-complete [14]. Moreover, if we remove the fixedoutline requirement we can derive a less constrained decision problem: **Problem 2.2.** (VLSI floorplanning) Given M modules with fixed rectangular shapes, decide if it is possible to pack all the rectangles in a bounding box of area A, such that no two rectangles overlap.

Murata et al. [15], show a polynomial reduction from the fixed-outline version of the problem that prove the NP-completeness of VLSI floorplanning. Allowing the modules to be rotated by ninety degrees do not change the complexity class, hence the unoriented and the oriented version of the problem are both NP-complete [16].

#### 2.2.2 FPGA floorplanning problem

We would like to derive a complexity result also for the floorplanning problem on partiallyreconfigurable FPGAs [17]. A direct polynomial reduction from the VLSI floorplanning problem, or from the make-span minimization problem [14], is not straight forward, mainly because our problem differs in three aspects:

- a reconfigurable region even though rectangular, does not have a fixed width and height but requires a certain amount of area;

- modern FPGAs have heterogeneous resources in specified positions of the chip, thus a reconfigurable region may need to cover different resources, disallowing some region placements and shapes;

- reconfigurable regions must cover complete tiles with respect to the FPGA matrix.

The objective function of the floorplanning can take into account different metrics and a tile can consist of several cells. However, for the purpose of proving the NP-completeness, we just consider a simplified decisional version of the problem where cells and tiles coincide and only overall area and wirelength are taken into account:

**Problem 2.3.** (floorplanning on heterogeneous partially-reconfigurable FPGAs) We are given a device matrix M of width W and height H and n reconfigurable regions. Each tile contained in M is characterized by an integer number of resources along with the resource type identifier. Each reconfigurable region can require different types and numbers of resources and the wirelength between regions is computed using the HPWL measure. The goal is to decide whether it is possible to assign all the reconfigurable regions to rectangles on matrix M such that: (i) no two regions overlap, (ii) all the regions cover the required number and type of resources, (iii) the number of covered tiles is not greater than  $\alpha$  (area bound) and (iv) the sum of the wirelength between regions is not greater than  $\gamma$  (wirelength bound).

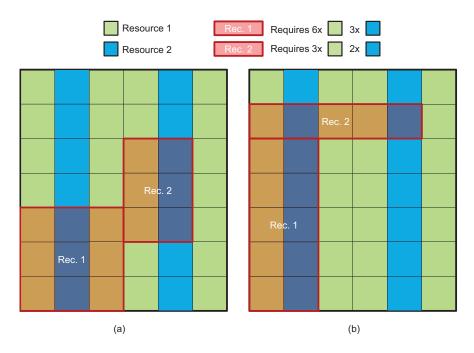

To clarify the description of the problem, we show in Figure 6 an example containing a valid and an invalid floorplan where we assume the values for  $\alpha$  and  $\gamma$  big enough to satisfy area and wirelength bounds. The device consists of two different types of resources, namely resource 1 and resource 2. In this scenario we consider one resource for each tile, hence there are 28 resources of type 1 and 14 resources of type 2. The resource requirements of the two reconfigurable regions to place on the device are shown on top of the figures. The placement 6a is valid, indeed the two regions do not overlap, are assigned device matrix rectangles containing complete tiles and cover all the required resources. On the other hand, 6b is not a valid floorplan, because even though the regions do not overlap and are assigned to rectangles covering complete tiles, we can easily see that region 1 does not meet the resource requirement for type 1 resources.

Figure 6: Valid (a) and invalid (b) floorplans

We are now ready to prove the following theorem:

# **Theorem 2.4.** The floorplanning on heterogeneous partially-reconfigurable FPGAs problem is NP-complete

*Proof.* To prove the claim we consider a polynomial reduction from the metric Travelling Salesman Problem  $(TSP)^1$  with Manhattan distance [18, p. 212], to the floorplanning on heterogeneous partially-reconfigurable FPGAs problem, from now on simply called floorplanning prob-

$<sup>^{1}</sup>$ In the metric TSP a metric is used to compute the distances between nodes, this ensures that the edges connecting them satisfy the triangular inequality.

lem. In the metric TSP with Manhattan distance we are given a complete undirected graph G(N, E) where N is the set of nodes and E the set of edges. The nodes are placed within the Cartesian plane at integer coordinates, for every node  $i \in N$  its coordinates are  $(i_x, i_y)$ . The cost of edges connecting each couple of nodes is computed using the Manhattan distance, so, for every edge  $e = \{i, j\} \in E$  its cost is  $c_e = |j_x - i_x| + |j_y - i_y|$ . The goal is to state whether there exists an Hamiltonian cycle<sup>1</sup> on graph G of cost not greater than  $\epsilon$  (cost bound). Papadimitriou proved that both Euclidean and Manhattan metric TSPs are NP-complete [19].

We now show that given any instance of the Manhattan metric TSP we can derive in polynomial time an instance of the floorplanning problem, such that the answer to the floorplanning porblem is "Yes" if and only if also the answer to the Manhattan metric TSP is so. This would imply that solving the floorplanning problem would be at least as hard as solving the Manhattan metric TSP.

Before going on in the proof, we assume, without loss of generality, that no two nodes of a Manhattan metric TSP lie on the same Cartesian coordinates. Indeed, thanks to triangular inequality, it is possible to devoid the problem instance from such multiple nodes, obtaining a new problem instance that is equivalent to the original one in terms of the least cost Hamiltonian cycle.

Consider now an instance of the Manhattan metric TSP, the construction of the corresponding floorplanning problem instance can be computed in polynomial time as follows:

<sup>&</sup>lt;sup>1</sup>An Hamiltonian cycle of an undirected graph G with |N| nodes is a cycle of G visiting all the |N| nodes exactly once. Its cost is the sum of the costs of all the edges in the cycle.

- generate a bounding box containing all the nodes of the graph, this is accomplished searching for the minimum and maximum values of the nodes coordinates: the left bottom corner and the top right corner of the bounding box are set to  $(\min_{i \in N} i_x - 0.5, \min_{i \in N} i_y - 0.5)$ and  $(\max_{i \in N} i_x + 0.5, \max_{i \in N} i_y + 0.5)$  respectively;

- consider an FPGA matrix having the same width and height of the bounding box, in which all the tiles are squares with unitary side (i.e. tileW = 1 and tileH = 1);

- move the FPGA matrix onto the bounding box, so that the matrix and the bounding box overlap exactly. This ensures that nodes within the bounding box are located in the center of tiles of the FPGA matrix;

- for each tile containing a node, assign a resource of type S (we refer to these as S tiles);

- assign to the remaining tiles an arbitrary resource different from S;

- consider n = |N| reconfigurable regions numbered from 1 to n;

- set the resource requirements for each reconfigurable region to exactly one resource of type S;

- consider the regions connected in circular order: 1 connected to 2, 2 connected to 3, ..., *n* connected to 1, where the bandwidth of each connection is unitary;

- set the area bound  $\alpha$  to n;

- set the wirelength bound  $\gamma$  to the TSP cost bound  $\epsilon$ .

The construction should appear clearer looking at Figure 7.

Figure 7: From TSP to floorplanning problem instance

An important consequence derived from our construction, is that each tile containing a resource of type S has its center in a direct correspondence to a node of the original TSP problem. Moreover, the Manhattan distance between the center of two S tiles is equal to the Manhattan distance between the corresponding nodes in the TSP problem.

Another property derived from construction regards the placement of the n reconfigurable regions. Since we have  $\gamma = n$  and each region requires exactly one resource, we cannot have regions covering more than one tile. Furthermore, the resource required by each region is of type S and since there are n S tiles, a valid floorplan must assign each region to a rectangle covering exactly an S tile not covered by other regions.

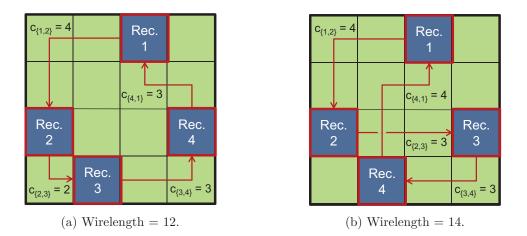

So far we have not yet considered the validity of the floorplan with respect to the wirelength. Figure 8 shows two floorplans satisfying the resource constraints and area bound but with different wirelength.

The wirelength of a link is computed with the HPWL measure, since the bandwidth have been set to 1 for all the connections, the HPWL is simply the Manhattan distance between the center of the two regions involved in the communication. Moreover, from what argued before, each region covers exactly an S tile, hence the region center corresponds to the covered S tile center. In conclusion, we have the following result:

**Property 2.5.** the wirelength between two connected regions is equal to the Manhattan distance of the two nodes in the TSP graph that correspond to the *S* tiles covered by the regions.

Figure 8: Wirelength of different floorplans

Thanks to Property 2.5 we are now able to show the equivalence of the two problem instances.

Given a florplan that satisfy the resource requirements and area bound, we can derive an Hamiltonian cycle in the TSP graph having the same cost as the wirelength of the floorplan. To achieve this, we simply label each node in the TSP graph with the number of the region that covers the S tile corresponding to the node. Then, the edges of the Hamiltonian cycle are those connecting nodes 1 and 2, nodes 2 and 3, ..., nodes n and 1. Since the connection between regions are circular we have a one to one correspondence between the connection of the regions and the edges within the Hamiltonian cycle. Thus applying Property 2.5 on each couple of connected regions, and summing up all the contributes, we have that the overall wirelength of the floorplan is equal to the Hamiltonian cycle cost.

On the other hand, given an Hamiltonian cycle in the TSP graph of cost c, we can derive a floorplan that satisfy the resource requirements and area bound with a wirelength equal to c. The first step is to convert the Hamiltonian cycle into a circuit and label the nodes from 1 to n following the arc directions. Then, we place each reconfigurable region i onto the S tile that correspond to node i. Thus, in the Hamiltonian cycle we have connections between nodes 1 and 2, nodes 2 and 3, ..., nodes n and 1 that corresponds to the same connections between regions 1 and 2, regions 2 and 3, ... regions n and 1. Again using Property 2.5 on each couple of regions, we get that the floorplan wirelength and the Hamiltonian cycle cost are the same.

The previous statements implies that an Hamiltonian cycle of cost no greater than  $\epsilon$  exists if and only if there exists a valid floorplan, that is a floorplan satisfying the resource requirements, the area bound and with a wirelength not greater than  $\gamma = \epsilon$ .

We have proven that if we can solve the floorplanning problem in polynomial time, we are also able to solve the metric TSP with Manhattan distance in polynomial time that is NPcomplete. Hence the floorplanning problem is NP-hard. It is easy to see that the floorplanning problem is also in NP. Indeed, given a floorplan solution consisting of the coordinates of the reconfigurable regions within the FPGA device, we can check in polynomial time if the solution is correct. This concludes the argument and shows that the floorplanning problem is NPcomplete.

Theorem 2.4 states that if P is different from NP it is not possible to solve the floorplanning problem in polynomial time. However, this should not prevent us from trying to develop an exact algorithm, the previous proof relies on an unbounded number of reconfigurable regions and to an arbitrary complex structure of the FPGA device. In real applications, such as the Software Defined Radio (SDR) design presented in [12] and discussed in Section 6.3, the number of reconfigurable regions is limited while the FPGA structure is quite regular. In this work we shows an exact approach based on a Mixed-Integer Linear Programming (MILP) model, that can find an optimal solution to the floorplanning problem.

# CHAPTER 3

### STATE OF THE ART

In this chapter we present the contribution of previous works regarding the floorplanning problem. Section 3.1 presents different floorplan representations that have been devised in literature for VLSI floorplanning. Then, within Subsection 3.1.1, we describe more specifically the *sequence pair* representation, that has been originally invented for VLSI design [15] and recently exploited for floorplanning on partially-reconfigurable FPGAs with heterogeneous resources [17]. In Section 3.2 we consider previous works on FPGA floorplanning, while Section 3.3 concludes the chapter underlining the limits of current methodologies and introducing our approach.

## 3.1 Floorplan representation

One of the main problems arising in VLSI floorplanning is how to characterize the solution space. Indeed modules, in principle, could be placed in the plane at any position, thus producing an infinite number of alternatives among which find a good and feasible solution. To overcome this issue, several representations on a finite space domain have been devised. We denote with  $\Pi$  the set of feasible floorplans, that is, the set of modules placements in the plane such that no two modules overlap, while we define  $\Gamma$  as the set of all the possible codes for a given representation. A representation is defined by means of two functions: the translating function  $\tau: \Pi \to \Gamma$  that maps a feasible placement to its code and a realization function  $\rho: \Gamma \to \Pi$  that, given a code, produce a feasible placement. Since the number of feasible placements is infinite while there should be a finite number of possible codes,  $\tau$  cannot be injective and  $\rho$  cannot be surjective.

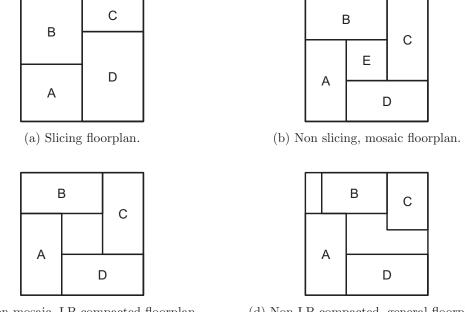

Notice that neither  $\tau$  nor  $\rho$  are required to be complete functions, they can also be partially defined<sup>1</sup>. In literature several representations have been proposed [20–30] with  $\rho$  functions defined on different  $\Delta \subseteq \Pi$ . Depending on the set of representable floorplans  $\Delta$ , we can have different type of floorplans [31]. From general to specific we have:

general floorplans: all the feasible floorplans in the space [21];

- **LB-compacted floorplans:** the feasible floorplans in the space such that no module can be moved bottom or left with respect to a containing rectangle [22];

- **mosaic floorplans:** obtained from the dissection of a rectangle in which no line crossings are allowed and such that all the dissections include exactly one module [23];

- slicing floorplans: obtained recursively dividing a rectangle using horizontal and vertical lines and such that all the divisions contain exactly one module [24].

Among the set of possible floorplans, the following strict inclusions hold:

$$slicing \subseteq mosaic \subseteq LB - compacted \subseteq general$$

(3.1)

<sup>1</sup>A function is partial, or partially defined, if not all the elements in its domain have an image.

(c) Non mosaic, LB-compacted floorplan.

(d) Non LB-compacted, general floorplan.

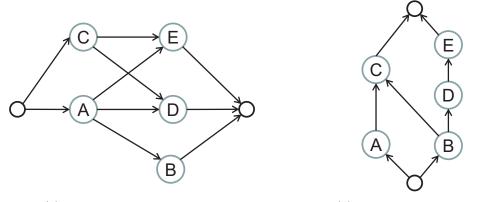

Figure 9: Examples of floorplan types

Figure 9 shows an example for each type of floorplan previously defined, the capital letters within the rectangles denote the presence of a module. Floorplan 9a is slicing since it can be obtained recursively dividing a rectangle with horizontal and vertical lines, while Figure 9b shows a mosaic floorplan having a wheel structure that cannot be represented as a slicing floorplan. Figure 9c represents a LB-compacted floorplan in which no module can be moved left or bottom, furthermore the empty area in the middle cannot be represented by a mosaic floorplan. A general floorplan is shown in figure 9d, notice that modules B and C can be moved left and bottom respectively, thus the floorplan is not LB-compacted.

Another characterization of floorplan representations is given in [15]. If we denote with  $\Omega$  the set of optimal floorplans with respect to some objective function, a representation is P-admissible if and only if it satisfies the following 4 conditions:

- 1.  $\Gamma$  is finite;

- 2.  $\rho$  is defined for all the codes in  $\Gamma$ ;

- 3.  $\rho$  can be computed in polynomial time;

- 4.  $\exists \gamma \in \Gamma \mid \rho(\gamma) \in \Omega$ .

The underlying reason of using a P-admissible representation, is that it is well suited for meta-heuristics such as simulated annealing. Indeed, thanks to property 1) 2) and 3), the algorithm converges efficiently to a feasible solution and by 4) we know that an optimal solution could be found. Much of the effort in VLSI design has been done on finding P-admissible representations trading off the type of representable floorplans  $\Delta$  to reduce the code space  $\Gamma$ . However, the flooplanning problem on FPGA devices having heterogeneous resource is quite different. First of all, the set of feasible placements  $\Pi$  is not infinite. In principle, one could enumerate all the possible placements, since the device matrix is finite and the reconfigurable regions must be placed at discrete coordinates. Secondly, and more important, the reconfigurable regions, as opposed to modules, cannot be placed at arbitrary positions in the space but have to cover specific resources at fixed positions within the FPGA. For these reasons and since, regarding FPGA floorplanning, feasibility is often an issue, it is advisable a representation that consider the overall generality of possible placements. One of the most simple and elegant P-admissible representations for general floorplans is the *sequence-pair* representation, introduced in [20] and later in [15]. In the following subsection we describe the sequence-pair representation and how it can be exploited for floorplanning on partially-reconfigurable FPGA devices with heterogeneous resources.

#### 3.1.1 Sequence pair representation

Given a set of M modules, a sequence pair is a floorplan representation defined by means of two sequences each containing a permutation of the modules. More formally, the set of codes of the representation is  $\Gamma = (pair_1, pair_2)$  where  $pair_1, pair_2$  are permutations of M. For instance, considering  $M = \{A, B, C, D\}$  a sequence pair can be  $(\langle A, B, D, C \rangle, \langle D, A, C, B \rangle)$ . In order to fully characterize the representation we also need to show how to compute  $\tau$  and  $\rho$ .

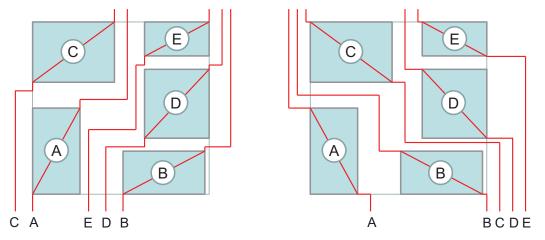

First of all, we consider the translation  $\tau$  from a general floorplan to the corresponding sequence pair, this computation is referred as *gridding* within [15]. For each module of the floorplan, we draw the so called *positive step-line* and *negative step-line*. The positive stepline of a module  $x \in M$  consists of three lines, namely: the *down-left step-line*, the principal diagonal of x and the *up-right step-line*. The up-right step-line starts at the up right corner of the module and goes up and right alternatively, while the down-left step-line is similarly defined starting from the bottom left corner of x. The positive step-line of x cannot cross other modules and other positive step-lines. Each positive step-line is identified by the name of the module that it traverses. Considering the identifiers of the positive step-lines from left to right, we obtain the first pair of the sequence. Independently from the positive step-lines, we can also draw the negative step-lines. The negative step-line of a module x consists again of three lines:

(a) positive step-lines:  $pair_1 = \langle C, A, E, D, B \rangle$  (b) negative step-lines:  $pair_2 = \langle A, B, C, D, E \rangle$

Figure 10: From a floorplan to its sequence pair representation

the *left-up step-line*, the secondary diagonal of x and the *right-down step-line*. The drawing of these lines is performed similarly but alternating left-up steps and right-down steps. Since also the negative step-lines do not cross each other, we can order them from left to right and obtain the second pair of the sequence from the lines identifiers. An example of gridding is shown in Figure 10 together with the corresponding sequence pair. Since gridding can be performed for each floorplan, the function  $\tau$  is defined for all the possible sequence pairs.

The second function that we are going to define is  $\rho$ , it maps a sequence pair to a floorplan by inducing the topological relations between the modules. The geometrical relation between modules  $x, y \in M$  depends on their relative positions, or indexes, within the two pairs of the sequence:

$$(\langle ..., x, ..., y, ... \rangle, \langle ..., x, ..., y, ... \rangle) \implies x \text{ at the left of } y$$

$$(\langle ..., x, ..., y, ... \rangle, \langle ..., y, ..., x, ... \rangle) \implies x \text{ above } y$$

$$(3.2)$$

For each couple of modules there can be only 4 possible relative orderings within the sequence pair. Two of these orders are given in Equation 3.2, while other two can be obtained by exchanging the names of the modules. Every order states a different relation between the two modules, namely: x at the left of y, x above y, y at the left of x, y above x. Regardless of the order in which the two modules appear, the sequence pair guarantees that they do not overlap. Starting from the *at the left of* relation and from the *above* relation, it is possible to construct the horizontal and vertical graphs respectively. In these graphs, the nodes are the modules, while the directed edges represent a horizontal or vertical order relation. An example of constraints graphs for the sequence pair  $(\langle C, A, E, D, B \rangle, \langle A, B, C, D, E \rangle)$  is shown in Figure 11. Transitive edges have not been drawn for simplicity, while sink and source nodes have been inserted.

Both the graphs constructed starting from the sequence pair are guaranteed to be acyclic [15], thus every sequence pair produce a feasible floorplan in terms of the geometrical relations among modules. From the constraints graphs, it is possible to compute the x and y coordinates of all the modules, using a longest path algorithm over the horizontal and vertical graphs respectively. Other more efficient approaches have been devised to generate the floorplan from

(a) Horizontal-constraint graph

(b) Vertical-constraint graph

Figure 11: Constraints graphs derived from a sequence pair

the sequence pair, such as [32] and its enhancement [33] that do not generate the constraints graphs but exploit Longest Common Subsequences (LCSs).

Regarding floorplanning on partially-reconfigurable FPGA with heterogeneous resources, it is not so straight forward to produce a feasible floorplan starting only from the sequence pair. The problem is to decide the width, height and position of the reconfigurable regions within the device in order to cover the required resources. However, with some modifications, sequence pair can still be successfully used [17]. The idea is to exploit the sequence pair to keep track of the geometrical relations between modules so that no overlaps occur. Then, new techniques must be devised to produce feasible and good floorplans starting from the sequence pair constraints. Notice that even if a fixed constraint graph is given, there still can be a lot of different floorplans on the FPGA with different costs in term of the objective function to be optimized. One of the two approaches that we are going to propose, starts from a heuristic solution given in terms of a sequence pair and find the optimal floorplan under the specified geometrical constraints.

#### 3.2 Related work

In literature, various floorplanners for FPGAs able to handle different features of commercial devices have been proposed. Subsection 3.2.1 presents floorplanners that deal with static placement without considering reconfiguration capabilities. Subsection 3.2.2 describes floorplanners that take into account also the time domain, while Subsection 3.2.3 presents floorplanners aware of the FPGA architecture considering both non homogeneous distributions of heterogeneous resources and PR constraints.

#### **3.2.1** Static floorplanners

A first class of algorithms focuses on static placement such as [34] and [35]. The solution proposed in [34] is based on the slicing tree representation [24] that is perturbed using simulated annealing to find a good floorplan. At each iteration of the annealer, a post processing step is performed trying to meet the resource requirements by modifying the rectangular shapes of the regions. The approach deals with heterogeneous resources and considers resource vectors containing CLBs, BRAMs and DSPs. Unfortunately, the proposed solution relies on a regular device structure in which even if the resources are of different types, they are organized in a repetitive pattern and are homogeneously distributed within the FPGA. Modern FPGAs are far from having such regular structures and this restrict the applicability of the approach to less recent devices. The method proposed in [35] is a two steps algorithm based on the formulation introduced in [34]. The first step exploits a fixed outline simulated annealing, augmented with a penalty term in the objective function to address the violation of resource requirements. The second step, by means of a Min-Cost Max-Flow formulation, modifies the rectangular shapes of the previously placed modules to guarantee the feasibility of the solution. However, if PR is taken into account, the shapes of the reconfigurable regions cannot deviate from rectangular shapes. This prevent [34] from using the post processing step, while regarding [35], their final solution unlikely meets the PR constraints as required by [5].

### 3.2.2 Reconfiguration-aware floorplanners

Another class of approaches introduces reconfiguration and takes into account the time domain. One of the most important contributions in this area is [36]. The algorithm relies on an extension of the Transitive Closure subGraph (TCG) representation [27] to deal with the temporal dimension. A 3-Dimensional Transitive Closure sub-Graph (3D-subTCG) representation is devised to take into account the reconfiguration process and the precedence relations between the modules on the device. However, the types of resources considered by this approach are restricted to logic blocks while other resources are ignored.

Other works such as [37] and [38] aim at reconfiguring the smallest amount of the system between two subsequent configurations. The work presented in [37] exploits a multi-layer sequence pair representation to solve the floorplanning problem, in which the types of resources considered are still restricted to basic blocks. On the other hand, the algorithm presented in [38] takes into account heterogeneous resources but only having a homogeneous distribution within the device. Both approaches, as stated in [17], are not compliant with the PR design flow, since they do not guarantee identical organizations in terms of number, shape and position of reconfigurable regions at different configurations.

Among the works in this category, [39] and its enhancement [40] are worth mentioning. The work proposed in [40] consists of two main steps: firstly, each task that has to be reconfigured on the device is assigned to a reconfigurable region while trying to minimize the variance of different used resources over time (temporal floorplacement). Subsequently, each reconfigurable region, defined by the maximum number of requested heterogeneous resources over time, is placed on the device. This step uses a simulated annealing based algorithm whose moves satisfy the PR constraints. However, this last step considers the different resources as homogeneously distributed within the device and does not take into account the complex structure of modern FPGAs.

#### 3.2.3 Architecture-aware floorplanners

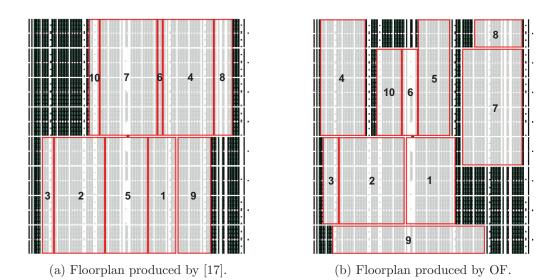

Both PR constraints and an accurate description of the heterogeneous resource distribution are considered in [17] and [12]. The algorithm [17] uses a floorplan representation whose set of codes  $\Gamma$  is defined by means of a sequence pair and a height vector. The sequence pair is needed to enforce the geometrical relations between reconfigurable regions, while the height vector sets for each reconfigurable region its height. The values of the height vector are positive integers and are selected according to the PR constraints of the device of choice. The search space  $\Gamma$  is explored with simulated annealing perturbing the floorplan representation. For each code  $\gamma \in \Gamma$ the realization function  $\rho$  producing the floorplan  $\rho(\gamma)$ , is computed in three steps: firstly,  $\rho$  obtains the vertical and horizontal constraints graphs from the sequence pair; secondly, using the vertical graph and the height vector, it computes the y coordinates of the regions and finally, greedy widens and moves the regions on the x axis to meet the resource requirements without violating the horizontal constraints graph precedences. Since not all the possible combinations of sequence pairs and height vectors lead to a feasible solution, [17] also implements a constraint violation term in the objective function, to guide the annealer in critical situations. Moreover, the algorithm is able to detect free spaces and perform smart moves to recover from solutions in which not all the resource requirements are satisfied.

The representation of a solution in [17], described by means of its sequence pair and height vector, can be, in general, mapped to a vast number of different floorplans on the device. The function  $\rho$  is computed using a fast greedy approach that does not give any guarantee on the quality of the floorplan. For this reason, the representation is not P-admissible, since it does not guarantee the existence of a code  $\gamma$  such that the floorplan  $\rho(\gamma)$  is optimal with respect to a given objective function. Thus, the annealer explores in general a sub-optimal solution space. On the other hand, computing  $\rho$  to optimality would not be convenient, since the computation has to be done at each iteration of the simulated annealing algorithm.

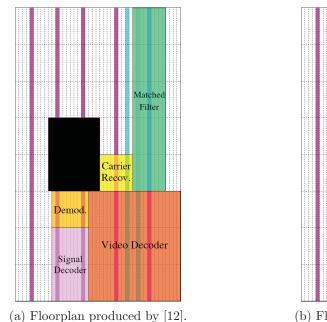

The work presented in [12], similarly to [17], produces floorplans that satisfy PR constraints and takes into account non homogeneous resource distributions. Their approach characterizes the FPGA device in terms of tiles (minimal reconfigurable units). Each tile contains a specific type and number of resources and consists of several configurable frames. Hence, the reconfigurable regions requirements are translated in terms of tiles requirements with some unavoidable resource overhead due to inexact divisions. The reconfigurable regions are assigned a priority based on the types and number of required tiles and are placed sequentially starting from those using rarer tiles such as DSP and BRAM tiles. The placing is performed by merging adjacent tiles on the same row to form kernels that contain at least some instances of the type of needed tiles. The smallest kernel in terms of configurable frames is selected and vertically extended to meet the region requirements. If other tiles, different from the rarest are required, the region is then extended horizontally trying to satisfy the region needs. The process is repeated several times using different kernels for packing. At the end of each iteration some post processing is performed on the columnar direction to locally improve the total wirelength without changing the shapes of the regions. The best outcome with respect to an objective function is then considered as the solution.

The fixed schedule of the regions and the greedy tile packing procedure may result in completely unexplored and potentially promising solutions of the search space. This issue is partially mitigated restarting the algorithm several times with different kernels, but still, there is no guarantee on the goodness of the solution found with respect to the optimal one.

#### **3.3** Limits of current approaches

Floorplanning on modern partially-reconfigurable FPGAs requires the floorplanner to meet both PR constraints and to cope with non homogeneous resource distributions. Among the works in this area, the only ones that take into account both these aspects are [17] and [12]. The approach proposed in [17] proved to give better results in terms of total wirelength with respect to [35] and [40], while [12] produced a better floorplan in terms of resource usage with respect to [40].

Although [17] and [12] give better results with respect to previous approaches, they still look for a solution in a sub-optimal or incomplete search space respectively. Furthermore, none of the algorithms give information about the quality of the solution found with respect to the optimum.

We propose two novel approaches based on a suitable MILP formulation that overcome these issues and give better results in terms of the objective function, at the cost of a generally higher execution time. Our algorithms let the designer decide to what extent optimize each term in a set of different metrics, giving also the possibility to modify and extend our models to take into account other objectives different from the ones presented in this work. The floorplans generated by our methodologies are compliant with PR design flow and can be used for FPGAs having non homogeneous resource distributions.

Table I, an update of the one presented in [17], recaps the features of state-of-the-art floorplanners.

|                             | [34]         | [35]         | [36]         | [37]         | [38]         | [39, 40]     | [12, 17]     |

|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Resource distribution-aware |              | $\checkmark$ |              |              |              |              | $\checkmark$ |

| Reconfiguration-aware       |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Compliant with PR           |              |              |              |              |              | $\checkmark$ | $\checkmark$ |

| Optimize interconnections   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| Considers IO pins           |              |              |              |              |              | $\checkmark$ | $\checkmark$ |

TABLE I: COMPARISON OF STATE-OF-THE-ART FLOORPLANNERS

# CHAPTER 4

## PROPOSED FLOORPLANNER

The first algorithm that we propose, Heuristic-Optimal Flooplanner (HOF), improves the quality of a solution produced by a heuristic such as [17] or [12]. HOF selects one or more good solutions from a heuristic, then, for each solution found, considers the sequence pair representation of the floorplan. Each sequence pair is used within a different MILP formulation to fix the geometric relations between reconfigurable regions. Finally, each instance is solved quickly using a state-of-the-art solver such as Gurobi [41], and the best outcome is considered. HOF can give good improvements of the solution with a small overhead in terms of execution time. This approach is well suited for heuristics that already consider the sequence pair representation such as [17].

The second approach that we propose, Optimal Flooplanner (OF), describes the entire problem using a MILP formulation that ensures non overlapping of reconfigurable regions without the need of a fixed sequence pair. OF is able to explore the full solution space of the problem and can in general give the optimal solution for small instances. When the solver is faced with big instances, it can be warm started using the solution achieved by HOF or from a different algorithm. If the instance is fairly hard, after a fixed amount of time the search can be stopped and the best solution found is retrieved. OF gives better results than HOF but is in general quite time consuming; hence the designer can select which of the two algorithms to adopt depending on his/her needs. The rest of the chapter is organized as follows: Section 4.1 shows a suitable representation of the FPGA device that is used within the algorithms, subsequently, Section 4.2 presents the MILP model used in OF and HOF, then, Section 4.3 introduces some additional constraints whose goal is to provide the MILP solver more information about the structure of the problem, finally, Section 4.4 concludes the chapter with some final considerations on the proposed model.

## 4.1 Device characterization

In this section we provide a characterization of the FPGA device that eases the MILP formulation, reducing as much as possible the need of integer variables that would make the problem hard to solve.

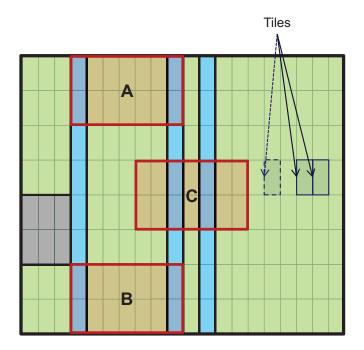

### 4.1.1 Matrix reduction

The first step toward the simplification of the problem is to reduce the device matrix granularity as done in [12]. Instead of considering the single resource on the chip, we can just take into account, without loss of generality, the tiles as the minimal area units. Using a matrix whose integer coordinates address tiles reduces both the solution space and guarantees PR constraints, since regions are placed using integer coordinates.

#### 4.1.2 Problem linearization

Floorplanning is intrinsically a non linear problem, since we have to ensure that each reconfigurable region occupies a two dimensional area large enough to include all the required resources. As a second step, to linearize the problem, we need to discretize one of the two axes. In general, the matrix obtained after the previous step is much larger on the x axis and has only a few possible values on the y axis. As an example, the Xilinx Virtex-5 XC5VLX110T can

Figure 12: Variables values of a region placed within the device

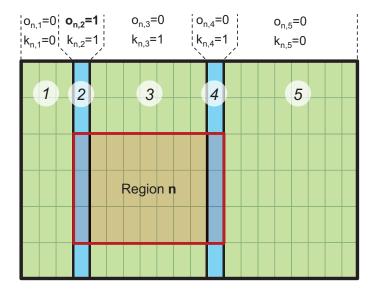

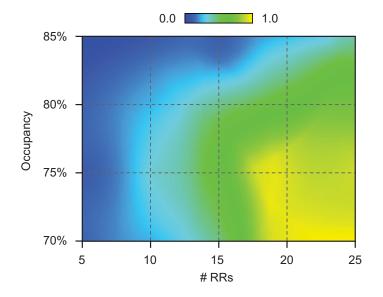

be described using a matrix of tiles with 8 rows and 62 columns. This suggests to discretize the device on the y axis. Figure 12 shows how the *linearization* process is performed: for each reconfigurable region like the one shown in the figure in red, a set of binary variables indexing the rows are used to state if the region occupies a specific row. On the x axis instead, a couple of integer variables representing the leftmost position and the width of the region suffice.

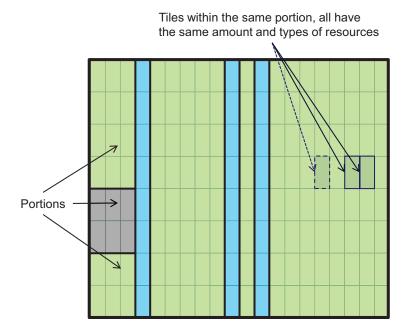

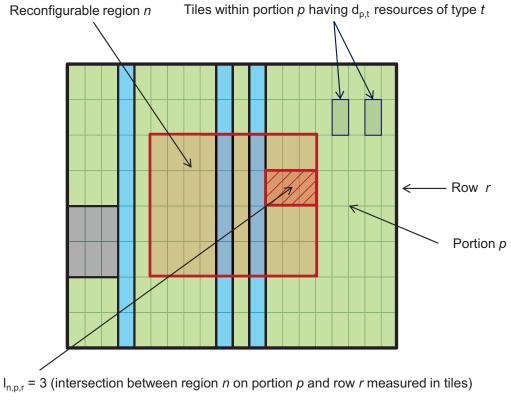

## 4.1.3 FPGA partitioning

The last step needed to fully characterize the device is to define for each tile the number and type of resources available. Fortunately, there is no need to consider all the tiles separately: even though different resources are available in different locations of the chip, the FPGA structure is quite regular and there are big areas characterized by the same *type* of tile. Two tiles are of the same *type* if they have the same amount and type of resources (e.g., two tiles having both 20 CLBs, 2 BRAMs and no other resources are of the same type). The FPGA can be partitioned into several rectangular areas named *portions*. All the tiles within a portion are required to be of the same type. A simple technique that can be used to create the FPGA partitioning is the following:

- 1. the FPGA is scanned top to bottom, left to right and the first tile that is still not part of any portion (free tile) is selected, then a new portion is created containing that tile;

- 2. the portion is extended on the right side until other free tiles of the same type are encountered;

- the portion is extended on the bottom side until all the tiles on the row below the portion are free and of the same type;

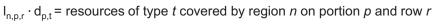

- 4. if there are still free tiles, the process is repeated from step 1 until all the tiles are part of one and only one portion.