### POLITECNICO DI MILANO

Facoltà di Ingegneria Industriale e dell'Informazione Corso di Laurea Magistrale in Ingegneria Informatica

### On how to Accelerate Iterative Stencil Loops: A Scalable Streaming-based Approach

Relatore: Prof. Marco Domenico SANTAMBROGIO

Correlatore: Dott. Ing. Riccardo CATTANEO

Tesi di Laurea di:

Giuseppe Natale

Matricola n. 803783

Carlo Sicignano Marticola n. 800774

Anno Accademico 2013–2014

This page intentionally left blank

## Contents

| 1 | Intr | roduction           |                                            | 1  |

|---|------|---------------------|--------------------------------------------|----|

|   | 1.1  | Conte               | xt                                         | 1  |

|   | 1.2  | The C               | Challenges of Exascale Computing           | 3  |

|   |      | 1.2.1               | The Energy and Power Challenge             | 4  |

|   |      | 1.2.2               | The Memory Challenge                       | 5  |

|   |      | 1.2.3               | The Concurrency and Scalability Challenge  | 7  |

|   |      | 1.2.4               | The Resiliency Challenge                   | 9  |

|   |      | 1.2.5               | The Software Challenge                     | 9  |

|   |      | 1.2.6               | Metrics                                    | 10 |

|   | 1.3  | Meeti               | ng the Challenges: Heterogeneous Systems   | 10 |

|   | 1.4  | A Cor               | ntextualized Overview of the Proposed Work | 13 |

|   | 1.5  | Thesis              | S Outline                                  | 14 |

| 2 | Bac  | uckground Knowledge |                                            | 15 |

|   | 2.1  | Polyh               | edral Framework                            | 15 |

|   |      | 2.1.1               | Polyhedral Model                           | 17 |

|   |      | 2.1.2               | Polyhedral Transformations                 | 29 |

|   | 2.2  | Stream              | ning Systems in FPGAs                      | 37 |

|   |      | 2.2.1               | Streaming Architectures                    | 38 |

|   | 2.3  | High                | Level Synthesis                            | 40 |

|   |      | 2.3.1               | What is HLS?                               | 40 |

|   |      | 2.3.2               | Advantages                                 | 41 |

|   |      | 2.3.3               | Evolution                                  | 42 |

|   | 2.4  | Iterati | ve Stencil Loops                                        | 44  |

|---|------|---------|---------------------------------------------------------|-----|

|   |      | 2.4.1   | Definition                                              | 44  |

|   |      | 2.4.2   | Main Characteristics and Implementation Challenges      | 47  |

|   |      | 2.4.3   | State of the Art                                        | 49  |

| 3 | A S  | calable | Hardware Accelerator for ISLs                           | 56  |

|   | 3.1  | The Is  | sue of Finding an Efficient Implementation              | 56  |

|   | 3.2  | Thesis  | Contribution                                            | 60  |

|   | 3.3  | The P   | roposed Solution                                        | 62  |

|   |      | 3.3.1   | Fundamental Principles                                  | 62  |

|   |      | 3.3.2   | A General Overview of the Proposed Hardware Accelerator | 65  |

|   |      | 3.3.3   | Some Considerations on the Input Code                   | 70  |

|   |      | 3.3.4   | A Comparison with Existing Works                        | 71  |

| 4 | Proj | posed I | Design Flow                                             | 77  |

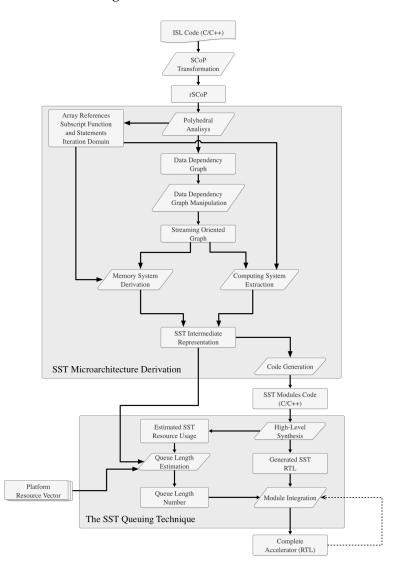

|   | 4.1  | Desig   | n Automation Flow                                       | 77  |

|   | 4.2  | Pre-pi  | rocessing Phase                                         | 80  |

|   | 4.3  | The S   | ST Microarchitecture Derivation                         | 81  |

|   |      | 4.3.1   | Streaming-oriented Graph Construction                   | 82  |

|   |      | 4.3.2   | Computing System Extraction                             | 88  |

|   |      | 4.3.3   | Memory System Derivation                                | 93  |

|   |      | 4.3.4   | SST IR and Code Generation                              | 95  |

|   |      | 4.3.5   | Pipelining the SST                                      | 98  |

|   |      | 4.3.6   | Scaling on the Problem Size                             | 100 |

|   | 4.4  | The S   | STs Queuing Technique                                   | 101 |

|   |      | 4.4.1   | Queue Length Estimation                                 | 104 |

|   |      | 4.4.2   | Handling More than One Input                            | 105 |

| 5 | Res  | ults    |                                                         | 108 |

|   | 5.1  | Exper   | imental Setup                                           | 108 |

|   | 5.2  | Test C  | ases                                                    | 110 |

|   |      | 5.2.1   | Polybench/C Jacobi 2-D                                  | 111 |

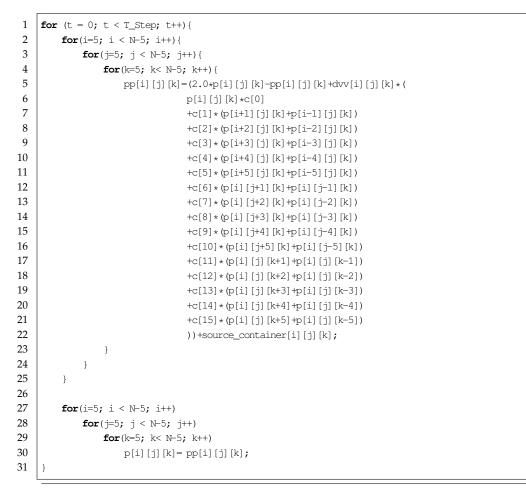

|   |      | 5.2.2   | FASTER RTM 3-D                                          | 111 |

iv

#### CONTENTS

|   | 5.3 | Exper   | imental Results    | . 113 |

|---|-----|---------|--------------------|-------|

|   |     | 5.3.1   | jacobi-2D          | . 115 |

|   |     | 5.3.2   | RTM do_step        | . 119 |

|   |     | 5.3.3   | seidel-2D          | . 123 |

|   |     |         |                    |       |

| 6 | Con | clusior | ns and Future Work | 125   |

| 6 |     |         | ns and Future Work |       |

| 6 | 6.1 | Concl   |                    | . 125 |

V

# **List of Figures**

| 1.1  | An illustration of the von Neumann Bottleneck. The graph refers                 |    |

|------|---------------------------------------------------------------------------------|----|

|      | to the evolution of canonical CPUs                                              | 6  |

| 1.2  | A simple scheme of an heterogeneous system.                                     | 11 |

| 1.3  | The general architecture of an FPGA                                             | 12 |

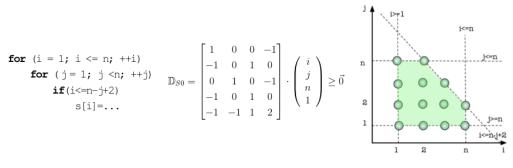

| 2.1  | Iteration Domain (ID) Example                                                   | 21 |

| 2.2  | Subscript Function Example. The three subscript functions are rel-              |    |

|      | ative to the three array accesses for s, a and x                                | 22 |

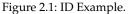

| 2.3  | An example of a dependence polyhedron. In this example the poly-                |    |

|      | hedron over the iteration vectors (one for the first statement, two             |    |

|      | for the second) and the scalar part are condensed in a single matrix            |    |

|      | (notice the 1 after the three iteration vectors). On the right there is         |    |

|      | a visual representation of the dependencies among the instances                 |    |

|      | of the two statements.                                                          | 26 |

| 2.4  | A simple schedule example. In this picture, the statement on the                |    |

|      | left has an <i>identity schedule</i> , as the statement instances are trivially |    |

|      | the points $(i, j)$ within the statement ID                                     | 27 |

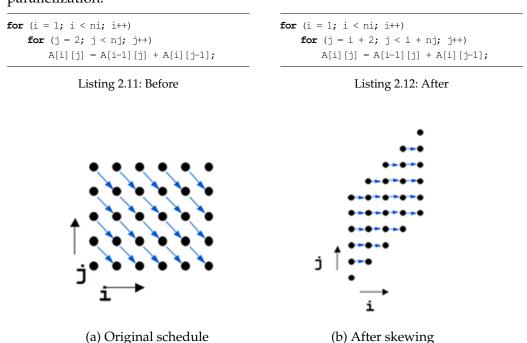

| 2.5  | Loop Skewing Example. The ID is "skewed" to allow inner loop                    |    |

|      | parallelization                                                                 | 34 |

| 2.6  | Loop Tiling Example. The ID is partitioned into the so called "tiles".          | 35 |

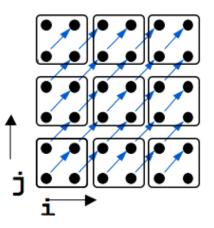

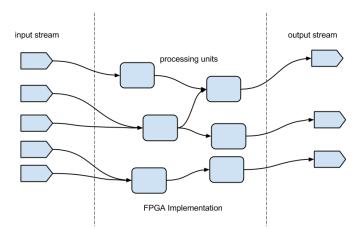

| 2.7  | Streaming Computing: A General Picture                                          | 38 |

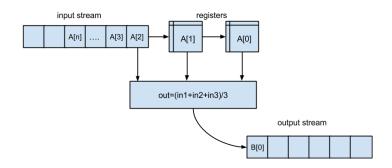

| 2.8  | Generic Streaming Architecture.                                                 | 39 |

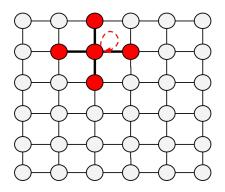

| 2.9  | An illustration of a generic 5-point 2-Dimensional ISL.                         | 45 |

| 2.10 | ISLs boundary types                                                             | 47 |

| 2.11                                          | Single Iteration Tiling.                                                                                                                                                                                                                                                                      | 50 |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

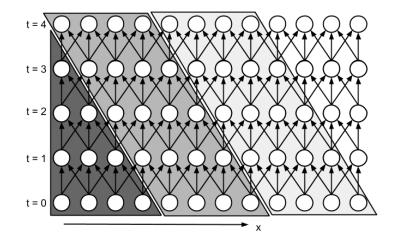

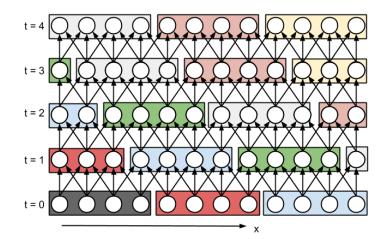

| 2.12                                          | Time Skewing                                                                                                                                                                                                                                                                                  | 51 |

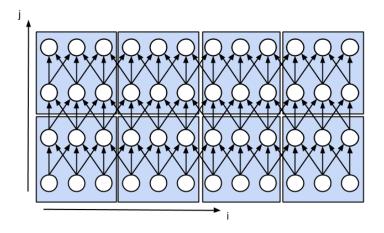

| 2.13                                          | Wavefront Parallelization                                                                                                                                                                                                                                                                     | 52 |

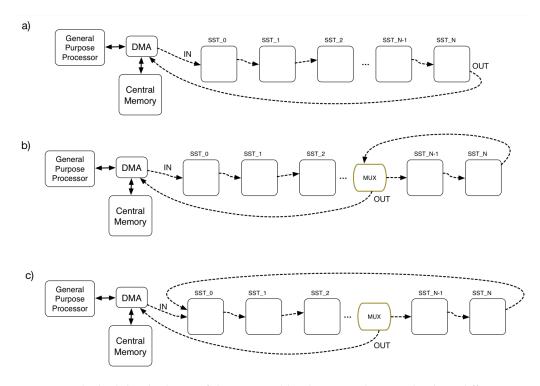

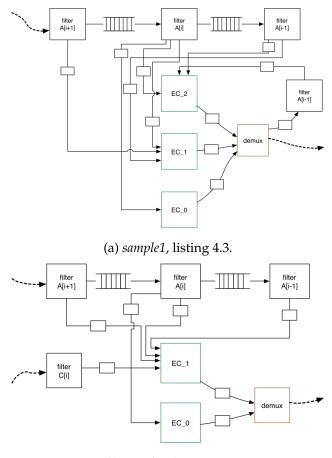

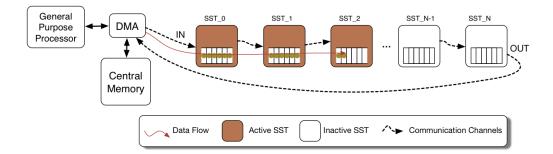

| 3.1                                           | The high level scheme of the proposed hardware accelerator. The                                                                                                                                                                                                                               |    |

|                                               | three different versions represent the three distinct described cases:                                                                                                                                                                                                                        |    |

|                                               | the first (a) is the standard case, the second (b) is the case in which                                                                                                                                                                                                                       |    |

|                                               | the queue length is not an exact divisor of the total number of ISL                                                                                                                                                                                                                           |    |

|                                               | time-steps, the third (c) is the case in which there are enough avail-                                                                                                                                                                                                                        |    |

|                                               | able resources to enable queue looping                                                                                                                                                                                                                                                        | 66 |

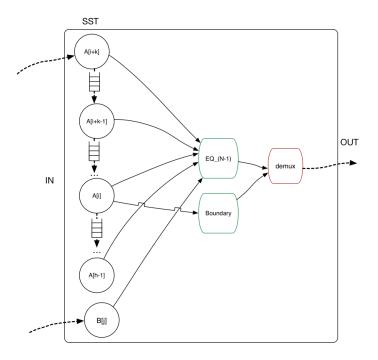

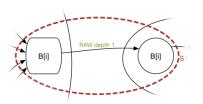

| 3.2                                           | A general scheme of an Streaming Stencil Time-step (SST) 6                                                                                                                                                                                                                                    | 67 |

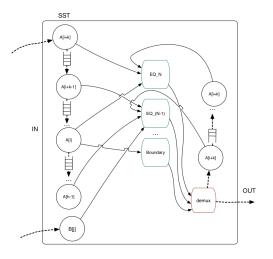

| 3.3                                           | An SST for ISLs with spatial dependencies.                                                                                                                                                                                                                                                    | 69 |

| 3.4                                           | An example of the accelerator for an ISL with multiple inputs. The                                                                                                                                                                                                                            |    |

|                                               | green arrows represents the additional streams. As described in                                                                                                                                                                                                                               |    |

|                                               | the text, the last SST has only the actual output stream. $\ldots$ $\ldots$ $\delta$                                                                                                                                                                                                          | 69 |

|                                               |                                                                                                                                                                                                                                                                                               |    |

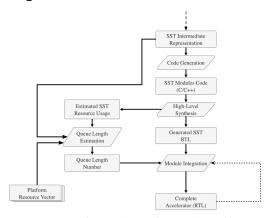

| 4.1                                           | The Proposed Design Automation Flow                                                                                                                                                                                                                                                           | 78 |

| 4.1<br>4.2                                    | The Proposed Design Automation Flow                                                                                                                                                                                                                                                           | 78 |

|                                               |                                                                                                                                                                                                                                                                                               | 78 |

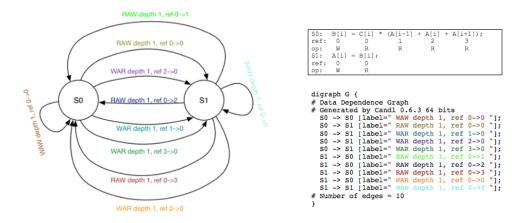

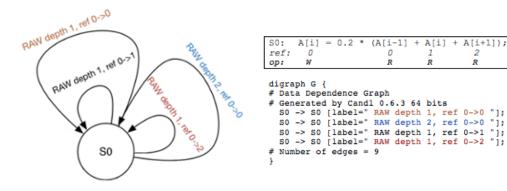

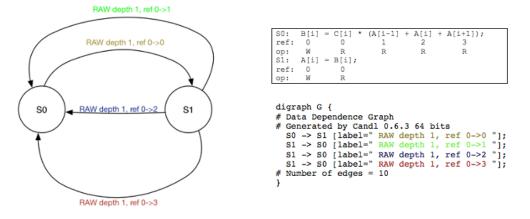

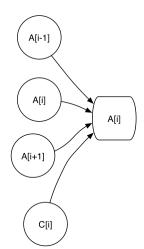

|                                               | An example of a complete Data Dependency Graph (DDG). The                                                                                                                                                                                                                                     | 78 |

|                                               | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there                                                                                                                                                            | 78 |

|                                               | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic       | 83 |

|                                               | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic       |    |

| 4.2                                           | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic form. |    |

| 4.2                                           | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic form  |    |

| 4.2                                           | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic form  | 83 |

| 4.2                                           | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic form  | 83 |

| 4.2                                           | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic form  | 83 |

| 4.2                                           | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic form  | 83 |

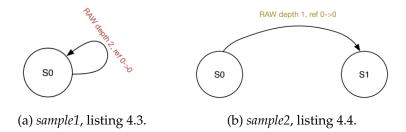

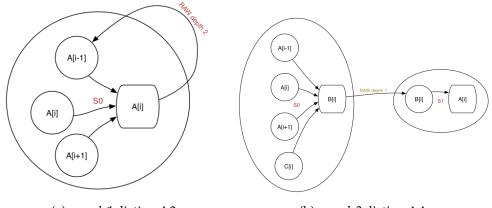

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul> | An example of a complete Data Dependency Graph (DDG). The graph is computed for <i>sample2</i> in listing 4.4. On the right, there is the output of the state of the art tool for <i>polyhedral dependency analisys Candl</i> [1], while on the left, there is the graph in its graphic form  | 83 |

| 4.6  | The dependence within the red circle is an example of the so called         |

|------|-----------------------------------------------------------------------------|

|      | "copy" dependency                                                           |

| 4.7  | The <i>Streaming-oriented Graph</i> of <i>sample2</i> , listing 4.4         |

| 4.8  | A visual representation of the instantiation of a <i>demux</i>              |

| 4.9  | An illustration of the cyclic dependencies between the output of            |

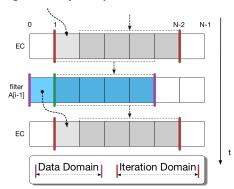

|      | the cyclic-write node and the cyclic-read node (filter) A[i-1] of sam-      |

|      | <i>ple1</i> , listing 4.3                                                   |

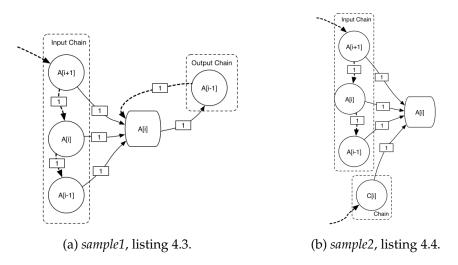

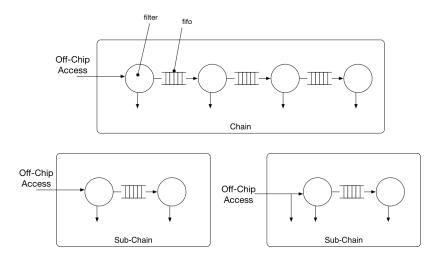

| 4.10 | The resulting chains for both samples                                       |

| 4.11 | A representation of the resulting SSTs for both samples 97                  |

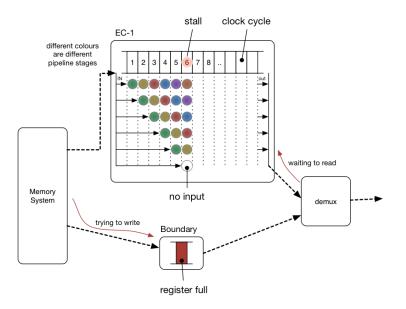

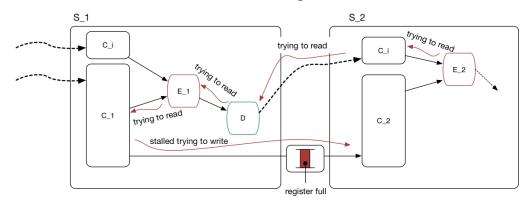

| 4.12 | A deadlock condition occurred because $EC_1$ is fully pipelined 99          |

| 4.13 | A communication channel is removed, to reduce the memory space              |

|      | requirements, and substituted with another off-chip access 100              |

| 4.14 | A visualization of the pipelined execution within the queue. $\ldots$ . 102 |

| 4.15 | The deadlock condition that can occur when queuing pipelined                |

|      | SSTs with multiple inputs                                                   |

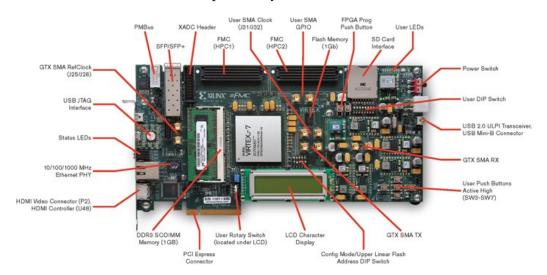

| 5.1  | The VC707 board. Image taken from the product site                          |

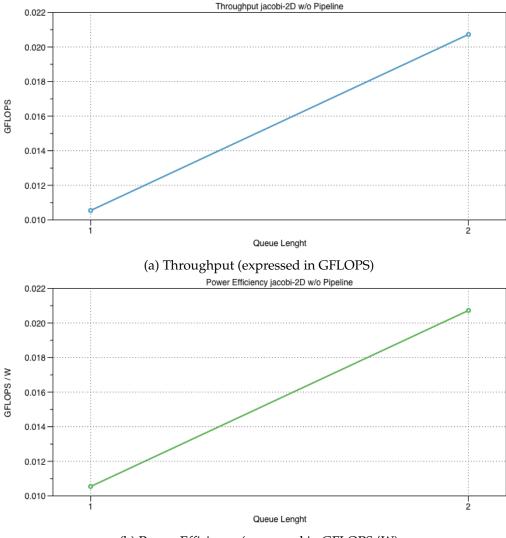

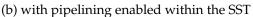

| 5.2  | Performance measurement of jacobi-2D without pipelining enabled             |

|      | within the SST                                                              |

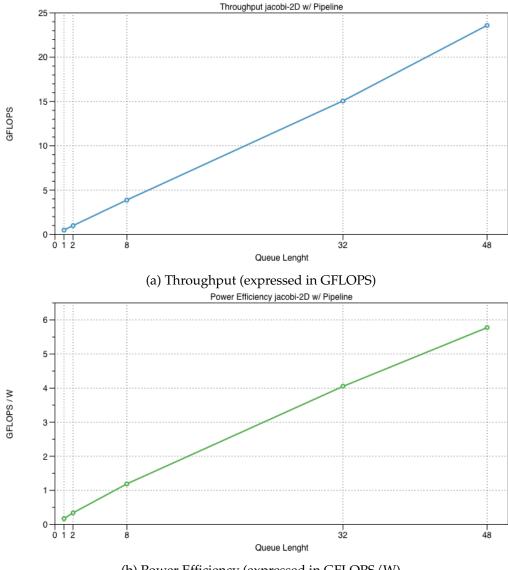

| 5.3  | Performance measurement of jacobi-2D with pipelining enabled                |

|      | within the SST                                                              |

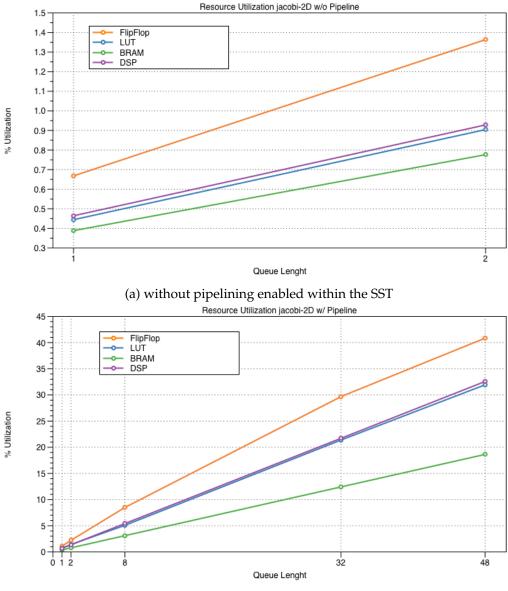

| 5.4  | Resource usage of the accelerator for the jacobi-2D benchmark 117           |

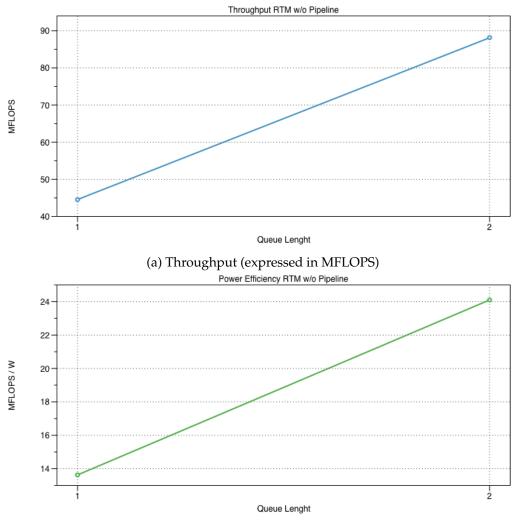

| 5.5  | Performance measurement of RTM do_step without pipelining en-               |

|      | abled within the SST                                                        |

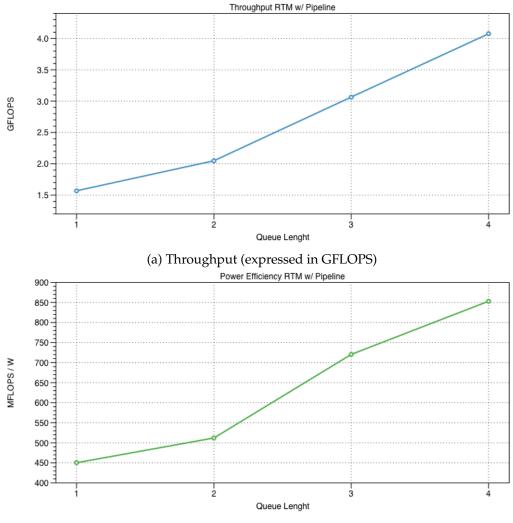

| 5.6  | Performance measurement of RTM do_step with pipelining en-                  |

|      | abled within the SST                                                        |

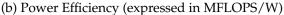

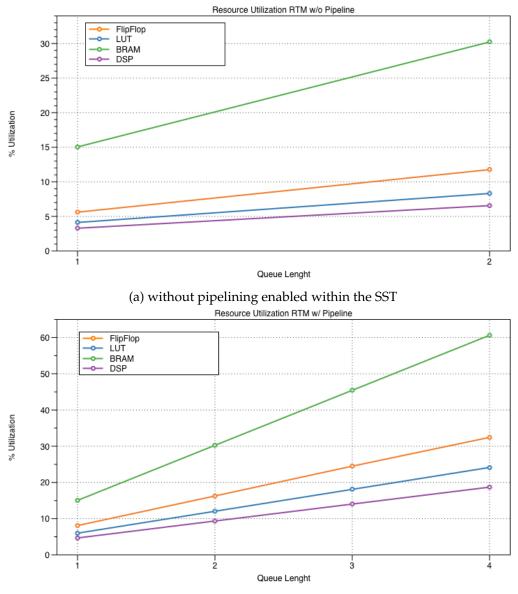

| 5.7  | Resource usage of the accelerator for the RTM do_step benchmark. 121        |

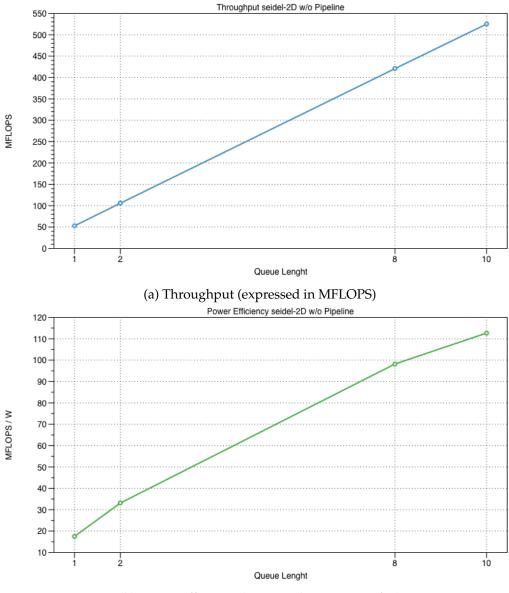

| 5.8  | Performance measurement of seidel-2D without pipelining enabled             |

|      | within the SST                                                              |

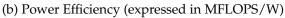

| 5.9  | Resource usage of the accelerator for the seidel-2D benchmark 124           |

## List of Tables

| 5.1 | jacobi-2D   | 18 |

|-----|-------------|----|

| 5.2 | RTM do_step | 22 |

| 5.3 | seidel-2D   | 24 |

# List of Algorithms

| 1 | DDG Construction                                           | 30 |

|---|------------------------------------------------------------|----|

| 2 | Dependence Polyhedra Construction                          | 31 |

| 3 | Generic ISL Algorithm                                      | 45 |

| 4 | Iterative Reduction of the <i>Streaming-oriented</i> graph | 87 |

| 5 | sd-Equivalence Classes Extraction                          | 92 |

# List of Abbreviations

| API  | Application Programming Interface       |

|------|-----------------------------------------|

| AST  | Abstract Syntax Tree                    |

| ASIC | Application-Specific Integrated Circuit |

| BRAM | Block RAM                               |

| CLB  | Control Logic Block                     |

| CPU  | Central Processing Unit                 |

| CV   | Computer Vision                         |

| DDG  | Data Dependency Graph                   |

| DFE  | Dataflow Engine                         |

| DMA  | Direct Memory Access                    |

| DRAM | Dynamic RAM                             |

| DSE  | Domain Space Exploration                |

| DSL  | Domain Specific Language                |

| DSP  | Digital Signal Processing               |

| FB   | Full Buffering                          |

| FIFO | First In First Out                      |

| FLOP | Floating Point Operation                |

#### LIST OF ABBREVIATIONS

| FLOPS | Floating Point Operations Per Second     |

|-------|------------------------------------------|

| FPGA  | Field Programmable Gate Array            |

| GPGPU | General Purpose Graphic Processing Unit  |

| GPL   | General Purpose Language                 |

| HDL   | Hardware Description Language            |

| HLS   | High Level Synthesis                     |

| HPC   | High Performance Computing               |

| HPRC  | High Performance Reconfigurable Computer |

| ID    | Iteration Domain                         |

| ILP   | Integer Linear Programming               |

| IOB   | Input-Output Block                       |

| IP    | Intellectual Property                    |

| IR    | Intermediate Representation              |

| ISL   | Iterative Stencil Loop                   |

| ISPS  | Instruction Set Processor Specification  |

| LUT   | Look-Up Table                            |

| MIMD  | Multiple Instruction Multiple Data       |

| MISD  | Multiple Instruction Single Data         |

| OR    | Operations Research                      |

| РВ    | Partial Buffering                        |

| PDE   | Partial Differential Equation            |

| PE    | Processing Element                       |

#### LIST OF ABBREVIATIONS

| PM    | Polyhedral Model                    |

|-------|-------------------------------------|

| PDG   | Polyhedral Dependency Graph         |

| PRDG  | Polyhedral Reduced Dependency Graph |

| RAM   | Random Access Memory                |

| RAR   | Read After Read                     |

| RAW   | Read After Write                    |

| RTL   | Register-Transfer Level             |

| RTM   | Reverse Time Migration              |

| rSCoP | Reduced Static Control Part         |

| SANLP | Static Affine Nested Loop Program   |

| SCoP  | Static Control Part                 |

| SIMD  | Single Instruction Multiple Data    |

| SISD  | Single Instruction Single Data      |

| SoC   | System-on-Chip                      |

| SRAM  | Static RAM                          |

| SST   | Streaming Stencil Time-step         |

| VHDL  | VHSIC Hardware Description Language |

| WAR   | Write After Read                    |

| WAW   | Write After Write                   |

### Summary

In *scientific computing* and in general in High Performance Computing (HPC), *stencil* computations play a crucial role as they appear in a variety of different fields of application, ranging from Partial Differential Equations (PDEs) solving, to computer simulation of particles interaction, to image processing and Computer Vision (CV), and a lot more. The computationally intensive nature of those algorithms has created the need of good solutions to efficiently implement them, in order to save both execution time, and energy consumption. This, in combination with their regular structure, has justified a wide study and the proposal of a lot of different approaches, in which virtually every kind of computing device currently available has been explored.

The work proposed in this thesis addresses Iterative Stencil Loops (ISLs) employing as enabling technology the Polyhedral Model (PM), with the aim of accelerate them using a Field Programmable Gate Array (FPGA) as target device. In particular, this research propose a *streaming-based microarchitecture* called Streaming Stencil Time-step (SST), able to achieve, thanks to an *optimal* Full Buffering (FB), a really low usage of the available resources as well as an efficient data reuse; and a technique, named SSTs *queuing*, able to effectively increase the throughput by a *pseudo-linear* factor, which exploits the characteristics of the proposed microarchitecture putting replicas of it in cascade, enabling, thanks to the streaming nature of the SSTs, a pipelined execution within the queue.

The methodology has been tested with some significant benchmarks on a *Virtex-7* using the *Xilinx Vivado* suite. Results show how the efficient usage of the on-chip memory resources realized by an SST allows to treat problem sizes

whose implementation would otherwise not be possible synthesizing directly the original code via High Level Synthesis (HLS), but also how the scalability given by the SSTs queuing ensure a pseudo-linear increase in throughput, while remaining with constant bandwidth.

### Sommario

Nel vasto scenario della *scienza computazionale* e dell'High Performance Computing (HPC) in generale, le computazioni di tipo *stencil* giocano un ruolo fondamentale in quanto appaiono sistematicamente in una pletora di campi applicativi, spaziando dalla risoluzione di equazioni differenziali alle derivate parziali, alla simulazione dell'interazione di particelle, all'image processing e alla Computer Vision (CV), e molto altro. Data la loro natura computazionalmente pesante, nel tempo si è evidenziata la necessità di soluzioni implementative efficienti, con l'obiettivo di ridurre sia il tempo di esecuzione, che il consumo energetico. Questo, in aggiunta alla loro struttura regolare, ha giustificato un esteso studio ed una varietà di approcci proposti, in cui praticamente qualsiasi dispositivo di elaborazione attualmente disponibile è stato esplorato.

Il lavoro proposto in questa tesi si focalizza sulla implementazione dei codici stencil, definiti Iterative Stencil Loops (ISLs), utilizzando come tecnologia abilitante il Polyhedral Model (PM), con l'obiettivo di accelerarli su una FPGA. In particolare, questa ricerca propone una *microarchitettura streaming* chiamata Streaming Stencil Time-step (SST), capace di ottenere, realizzando un Full Buffering (FB) *ottimo*, un basso uso delle risorse disponibili ma anche un efficace riuso dei dati; ed una tecnica, chiamata *accodamento* delle SST, in grado di aumentare il throughput di un fattore *pseudo lineare*, e che consiste nello sfruttare opportunamente le caratteristiche della microarchitettura proposta collegandone in cascata delle repliche, abilitando, grazie alla natura streaming delle SST, un'esecuzione in pipeline all'interno della coda. La metodologia è stata testata con alcuni significativi benchmark su una *Virtex-*7 utilizzando la suite *Vivado* di *Xilinx*. I risultati mostrano come l'efficiente utilizzo delle risorse di memoria on-chip realizzato da una SST consenta di trattare problemi la cui dimensione non ne consentirebbe l'implementazione sintetizzando via High Level Synthesis (HLS) direttamente il codice originale, nonché come la scalabilità data dall'accodamento delle SST garantisca un incremento pseudo lineare del throughput, pur restando a banda costante.

# Introduction

1

Anyone can build a fast CPU. The trick is to build a fast system.

- Seymour Cray

In this Chapter it is introduced the context required to motivate the work done in this thesis. Section 1.1 describes this context, namely the High Performance Computing (HPC) field and its evolution towards the Exascale era. In Section 1.2 the main challenges that arise when designing the next generation systems are presented, while Section 1.3 provides a brief description of the heterogeneous systems, with special attention on Field Programmable Gate Arrays (FPGAs), that current trends sees as a promising approach to meet the presented challenges. Finally, Section 1.4 provides a high level overview of the proposed work within the context of the transition towards Exascale computing.

#### 1.1 Context

Over 3 millions cores, clustered into 16k nodes, where each node has 88 gigabytes of memory, for a grand total of over 1 petabyte, a power consumption of 24 megawatts (accounting also cooling) and a performance of 33.86 petaflops: this is *Tianhe-2*, today's top supercomputer [10]. Although from these numbers it is clear that HPC systems can now deliver performance whose order of magnitude was simply unimaginable at the time of the first supercomputers, there are still certain classes of problems that are unmanageable with the currently available computing power. Therefore, it is time for HPC to take a step further.

In HPC, the important milestones are considered the emergence of systems whose overall performance, expressed as the number of Floating Point Operations Per Second (FLOPS) a given system is able to perform, crosses the threshold of  $10^{3k}$ , for some  $k \in \mathbb{N}$ . A first important achievement was made in 1985 where the Gigasacale ( $10^{9}$ ) was reached with the *Cray-2*. In 1997 Terascale ( $10^{12}$ ) was delivered by Intel's *ASCI Red*, and in 2008 Petascale ( $10^{15}$ ) was achieved by the IBM's *Roadrunner*. It is believed that in the near future, approximately in 2020, the systems will achieve Exascale ( $10^{18}$ ).

The need of such a technology advancement can be justified with a simple claim: some of the key computational challenges, that are faced not only by industry, or science, but civilization as a whole, can be addressed thanks to Exascale computing. There are a lot of practical problems that can benefit substantially from it: in climate modeling, it could help to adapt faster to climate changes and sea level rise thanks to a much more accurate forecasting; in medical systems it could allow a dramatic advancement in the research for preventing and curing cancer as well as the other challenging diseases of our age; in astrophysics it could finally lay bare the secrets of the formation of the universe; in the energy field the impact would be even stronger, as it could allow to better control fusion but also to effectively reduce pollution helping to design innovative cost-effective renewable energy plants. Last but not least, it is believed that Exascale is the order of processing power of the *human brain* at neural level, and because of that, an Exascale system could allow the reverse engineering of a human brain, but also - and more interestingly, though - the possibility to emulate it [9].

Current trends, however, suggest that there is the need to explore alternative solutions, or the goal of achieving Exascale computing may remain only feasible on paper. Indeed:

• Moore's Law, if interpreted *incorrectly* as the doubling of performance every 18-24 months, has hit a *power wall*, as indeed clock rates have been essentially the same since the beginning of 2000s.

- Moore's Law, if interpreted *correctly* as the doubling of the number of transistors on a chip every 18-24 months, is still valid. However, it must be stated that it is impossible to reach Exascale just by doing more of the same but bigger and faster. Indeed, current technology cannot be used to build an Exascale system, as it would probably cost more than 100 billion dollars, and require its own dedicated power plant and over 1 billion dollars per year to be powered [108].

- The attempt to hide the ever increasing memory latency wall by designing larger and more complex cache hierarchies has definitely hit its limit in terms of effectiveness on real applications.

- New parallelization strategies are needed. It is increasingly complex to extract parallelism from sequentially designed programs automatically, but also the distribution of the load onto an enormous number of Processing Elements (PEs) requires a radically different approach.

- The traditional single-domain research activities where hardware and software are explored in an isolated way cannot anymore sustain the growing demand of efficient solutions.

#### **1.2** The Challenges of Exascale Computing

While designing a new system that can be competitive with HPC modern standards requires a non negligible effort, managing to make a performance leap of orders of magnitude is infinitely more complex. There are in fact some important challenges within the HPC field that must be addressed in the proper way in order to be able to make such an accomplishment [27]. The focus of this section is to clearly define what they are, and how they impact the design of the next-generation systems.

#### **1.2.1** The Energy and Power Challenge

Power consumption is the most compelling concern, since it is absolutely critical to reduce its requirement of at least 2 orders of magnitude for future hardware and software technologies. This is because one of the main cost of operating an HPC system, *i.e.* of the operating expenditure (OpEx), is precisely power consumption. Indeed, assuming a linear scaling of the best of breed system in terms of performance, the already cited *Tianhe-2*, the power requirements for an equivalent Exascale system would still be of the order of gigawatts, with an energy cost of more than 2 billion dollars per year. Therefore new serious research challenges arise to achieve a better power efficiency, and it is believed that this will be the area in which significant improvement will be the most difficult to achieve.

The majority of the power consumed by supercomputers today is not used to handle computations, but is used to move data around the system. Indeed, we can model the power demand of the copper wires within a system as [101]:

Power

$$\approx$$

B  $\times$  I<sup>2</sup>/A

Where B is the bandwidth of a wire, A is the cross-sectional area of the wire and  $I^2$  is the length of the wire. From this model, which is a simple RC model that does not take into account all the variables that concur in the actual power consumption, it is already clear that:

- Power consumption increases proportionally to the bit-rate, so as we move to ultrahigh-bandwidth links, it can become a major concern;

- Power consumption is highly distance-dependent, as it is quadratic with the wire length.

- Making smaller-sized wires will not improve the energy efficiency or data carrying capacity.

Therefore the emerging constraints on energy consumption will effectively influence the way of designing an HPC systems, for example leading to an increase in the usage of optical technologies to perform data movements, also adding to the goals of algorithm design the power constraints as well as an efficient reduction of data movements. Designing an HPC system with lower power requirement leads to various advantages, first of all the scale down of the cooling system size which in turn involves in cutting the overall costs of the HPC system. Even if there have been substantial improvements in energy efficiency during the last years, HPC continues to be criticized for its extraordinarily high energy demand, leaving a strong need for an accelerated progress.

The U.S. Department of Energy has set the goal of 20MW as the limit of energy consumption for an Exascale system to keep its operational cost in a feasible range, whereas modern data centers typically provide that amount of power. However, the most efficient large-scale HPC system, the german *L-CSC* [5], makes us understand how distant the actual technology is from the desired goal, since it is capable of achieving only 5 GFLOPS/W. An Exascale system would need an improvement of  $10 \times$  with respect to the L-CSC's power efficiency in order to stay under the limit of 20MW.

#### 1.2.2 The Memory Challenge

The second major challenge is undoubtedly related to information storage, and is due to the lack of currently available technology to retain data at high enough capacities, but also to access it at high enough rates, still remaining within an acceptable power demand.

Memory capacity using traditional Dynamic RAM (DRAM) technology turns out to be a matter of costs. Current trends show that although the number of cores per processor is increasing, the amount of memory ratio with respect to the available computational capacity is decreasing. This is essentially due to fact that the cost of memory has not been decreasing as rapidly as the cost of floating point performance, simply because the rate of increase of memory density has never been as rapid as that of Moore's law for the number of transistors on a processor. Even though enormous progress in this sense have still been made, as the memory cost has decreased by a factor of over 10<sup>10</sup> in less than sixty years, current costs are still prohibitive when a very large amount of it is needed. Memory bandwidth is instead a structural issue rather than a cost issue. In fact, while for processors the demand has ever been for more rapid instruction execution, memory evolution has been guided by the demand of an increase in density to maximize the amount of data available to the processors, resulting in the employment of production technologies that allowed to build large capacity memories, for which, however, the latency was relatively high. This in turn resulted in an ever growing gap between the number of instructions a processor is able to execute and the number of memory transfers that can be done within the same amount of time.

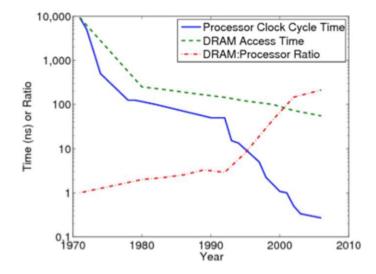

Figure 1.1: An illustration of the von Neumann Bottleneck. The graph refers to the evolution of canonical CPUs.

This problem is known as the "von Neumann bottleneck", as it can be thought as *structural*, related to how computation systems are made. Processor designers addressed this issue by designing hierarchical memories to mask the memory latency. Modern processors are in fact equipped with different levels of memory caches that can store data from DRAM so that future requests for that data are readily available. Cache memories located on-chip are typically built from Static RAM (SRAM). This type of memory is constructed from transistors and it has lower latency with respect to DRAMs, but it has very low data density and it is also more susceptible to errors that force them to be designed with error correction logic, resulting in higher costs, the reason why they are small-sized and still need to be backed by traditional DRAM. Considering this hierarchical nature of memory, it is obvious that is preferable for the processor to find the piece of required data in the cache, as it can be accessed more rapidly. Hence, when the processor needs to read or write a location in main memory, it first checks if it is available in the cache. If the data is present this is called a cache hit, if not, it is a cache miss. When the cache misses ratio is high, the impact given by the employment of a hierarchical memory system can be completely null, therefore care must be taken in order to exploit it properly.

To summarize, the memory challenge must be addressed in two different but nevertheless complementary ways:

- providing as much capacity at each level of the hierarchy, but with an acceptable request in terms of cost;

- providing the most effective methods for moving data among the levels as dictated by the needs of the various applications. This is crucial also because memory latency heavily impacts parallel cores performance, essentially due to the inherent need of synchronizations.

#### 1.2.3 The Concurrency and Scalability Challenge

The end of the increase in single compute node performance by increasing instruction level parallelism and higher clock rates has left explicit parallelism as the only mechanism to increase overall performance of a system. Mathematical models, numerical methods, and software implementations will all need new conceptual and programming paradigms to make effective use of extreme levels of concurrency. With clock rates flat at several gigahertz, systems will require more than one billion concurrent operations to achieve Exascale levels of performance and most of this increase in concurrency will be within the single compute node.

Concurrency can be measured in three ways:

• The total number of operations that are instantiated in each cycle to run the applications.

#### 1. INTRODUCTION

- The minimum number of threads that run concurrently to provide enough instructions to generate the desired operation-level concurrency.

- The overall thread-level concurrency that is needed to allow some percentage of threads to stall while performing high-latency operations, and still keep the desired dynamic thread concurrency.

A clear medium-term priority is the definition and implementation of algorithms that are scalable at very large levels of parallelism and that remain sufficiently fast varying latency and bandwidth availability; scalability should be modeled and analyzed mathematically, using abstractions that represent key architectural features.

The increased levels of concurrency in a system greatly increases the number of times that different kinds of independent activity must come together at some sort of synchronization point, increasing the potential for races, metastable states, and other difficult to detect timing problems. It will be necessary to maintain something like a billion threads of control, subdivided into a millions of processors cores to achieve an exaflop. A directly related problem will be the need to make sure that the required data is readily accessible to the computational units. Thus the data must be staged appropriately and the locality of the data must be maintained. Performance scalability of computing systems has been and will continue to be increasingly constrained by both the power required and speed available to enable data communications between memory and processor, but also by the phenomenon knows as dark silicon [45], caused by the failure of Dennard scaling [43], i.e. transistor scaling and voltage scaling are no longer in line with each other. The mere increase of the amount of cores cannot be carried out without exceeding in power density, which in turn can result in the impossibility to keep the chip temperature in the safe operating range. This limitation force to systematically power up only a fraction of the entire die, causing large idle or heavily underclocked portions of silicon area, hence the term dark silicon. This phenomenon inevitably restricts the amount of cores a chip can accommodate. The inability to go beyond a certain limit is indeed influencing also the employed parallelism paradigms, as in fact the pure many-core parallelism is being gradually replaced by forms of process-level parallelism, an example of which is *MapReduce* [42].

#### 1.2.4 The Resiliency Challenge

*Resiliency* is the property of a system to continue effective operations even in the presence of faults either in hardware or software. The vast majority of today's applications assume that the system will always operate correctly. However, an HPC system must be able to use so many components that it is unlikely that the whole system will ever be operating normally, as it is obvious that, the more the system is large, the shorter is the mean time between failures (MTBF). The common approach for resilience, which relies on automatic or application level checkpoint and restart, is not suitable for very large systems, as the time for checkpointing and restarting could even exceed the mean time to failure (MTTF), resulting into an irreversible deterioration of the integrity of the system. Also, the problem intensifies when considering that there is the need of handling the lack of resilience of not only computation, but also communication and storage.

#### 1.2.5 The Software Challenge

While large scale parallel processors have greatly increased the performance potential for HPC, they have also introduced substantial new software development problems. There are basically two schools of thought regarding the issue of properly adapting software development to the context of HPC. In the first case, the belief is that is it feasible to extract parallelism opportunities from current software, as well as enhance the available paradigms to be able to deal with the enormous amount of concurrency needed. In the second case, the belief is that a radical rethink is required, and that new methods, algorithms, and tools are needed to enable the performance leap.

The reality is however that both philosophies *must* coexists, and that the actual need is to figure out how to integrate and support existing computation paradigms while enabling new revolutionary paradigms. At the same time, it is also crucial to provide software developers with the right skills, since up to now there is a serious lack of parallel programming skills across all the degrees of experience, from entry level to very high end. An effort must be also made to raise awareness among HPC users, scientists in the first place, to understand the software challenges and train them to deal with the ever increasing complexity of the systems.

#### 1.2.6 Metrics

Different HPC systems have in general really different architectures, employ a variety of computing devices and handle data movements with different approaches. Hence, there is the need to define some standard metrics that can be used as terms of comparison. Within the HPC field, the most significant metrics are:

- Throughput, measured in FLOPS,

- Bandwidth, measured in bit/s,

- Total Power and Power Efficiency, measured respectively in watts (W), and FLOPS/W.

#### 1.3 Meeting the Challenges: Heterogeneous Systems

The majority of existing supercomputers generally achieve only a fraction of their peak performance on certain portions of some application tasks. This is because different subtasks of an application can have very different computational requirements that result in different needs for processing capabilities. An homogeneous architecture cannot satisfy all the computational requirements in certain applications equally well.

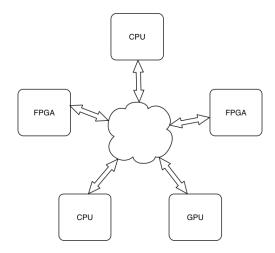

Thus, the construction of an heterogeneous computing environment is more appropriate. Employing an heterogeneous system can be the solution to properly meet all the presented challenges, as it offers the opportunity to increase the computational performance keeping low the energy requirements. Heterogeneous computing [103] refers to systems that use more than one kind of PEs, each of which is particularly efficient within a specific application domain. These PEs communicate through a system of high-performance interconnections. To take advantage of such a system, a given task is decomposed into subtasks, where each subtask is computationally homogeneous, and assigned to the PE whose characteristics are the most appropriate to its execution. One or more PEs, being canonical Central Processing Unit (CPU), are in charge of managing the offloading to the other PEs, as well as the execution of general purpose components of the computation such as operating system services.

Figure 1.2: A simple scheme of an heterogeneous system.

The rationale beyond the employment of an heterogeneous system is that CPUs are designed to handle complex control flows, but their general purpose nature makes them unfit to retain a high and cost effective throughput whit respect to other available solutions. CPUs are then coupled with other coprocessors, namely General Purpose Graphic Processing Units (GPGPUs) and FPGAs, both of which have specific characteristics that make them suitable to perform certain kinds of computation. GPGPU, being Single Instruction Multiple Data (SIMD) processors, perform very well on highly data parallel tasks. They have a massively parallel hardware architecture, are capable of achieving high floating point performance and have large off-chip memory bandwidth, however it

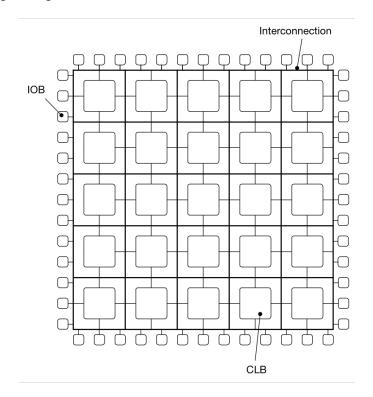

is usually very difficult to make GPGPUs work at their full capacity and use all the available bandwidth. Also, for high end chips the power demand can be huge, even though they are still capable of delivering high power efficiency - at least with respect to conventional CPUs, which justifies their employment as coprocessors in heterogeneous systems. FPGAs offer very high I/O bandwidth and fine-grained, custom and flexible parallelism. They are mainly composed of three building blocks [61]: the Control Logic Block (CLB) is the main component, it can implement one or more function generators using Look-Up Tables (LUTs) which in turn implement an arbitrary logic function, storing the result of the function for every possible combination of the input. The Input-Output Blocks (IOBs) are in charge of connecting the signals of the internal logic to an output pin of the FPGA package. The interconnection resources allow the connection of CLBs and IOBs. An FPGA can have additional resources embedded on the die, such as Random Access Memory (RAM) cells (also called Block RAM (BRAM)) that can be used to store data on-chip during the computation, Digital Signal Processings (DSPs) and other specific processors.

Figure 1.3: The general architecture of an FPGA.

The structure of an FPGA enables tasks-tailored logic to be created on-the-fly, that, considering the ever-increasing computational needs coupled with the frequency/power wall, is the perfect solution to have both performance and low power consumption. Indeed, the employment of custom logic, shaped on the specific type of computation, allows to have, within the entire fabric of an FPGA, only the part demanded to implement the circuit to be powered on. Therefore, an efficiently designed custom logic can lead to both sustained performance and low power consumption, as previously stated, thus high power efficiency. High Performance Reconfigurable Computers (HPRCs) based on conventional CPUs and FPGAs as coprocessors have indeed been gaining the attention of the HPC community in the past few years. In these systems, the main application executes on the CPUs, while the FPGAs handle kernels that have a long execution time and are suitable to hardware implementations. Such kernels are typically data-parallel overlapped computations that can be efficiently implemented as fine-grained architectures. Optimization techniques such as overlapping data transfers between the CPUs and FPGAs with computations are useful for dataintensive, memory bound applications.

However, there is an underlying complexity in heterogeneous systems that simply cannot be handled with modern software solutions, as different architectures must be programmed in different ways. Therefore, there is the need to provide automatic solutions capable to hide the complexity of these systems, as well as promoting the adoption of techniques that bring together software and hardware design, the so called *co-design*, which is believed to be a promising solution to make Exascale computing a reality [19].

#### 1.4 A Contextualized Overview of the Proposed Work

Within this context, the work proposed in this thesis embraces the principles of heterogeneous computing to make a little step towards the achievement of the Exascale milestone. We restrict ourselves to treat one class of algorithms, namely the Iterative Stencil Loop (ISL), a relatively small but very interesting domain in the context of HPC, as they systematically appear in both scientific and industrial related computations. ISLs usually operate on multi-dimensional arrays, with each element computed as a function of some neighboring elements, and these neighbors represent the *stencil*. A thorough description of them will be provided in section 2.4.

In this work, we attempted to meet the presented challenges for the class of ISLs by designing a domain-tailored hardware accelerator, which relies on the following key points:

- the employment of custom logic to deliver high power efficiency;

- a custom memory architecture to *reduce data movements to the minimum*, realizing an efficient data reuse;

- a technique that realize *linear scaling* which enables throughput increase with constant bandwidth requirements;

- an inherent *parallelism* due to the use of a distributed microarchitecture, which fits perfectly with the distributed nature of an FPGA;

- a *design automation flow* to automatically derive the accelerator from the input source code.

#### **1.5** Thesis Outline

The rest of this thesis is organized as follows. In Chapter 2 the needed background knowledge is provided, where all the basic concepts related to this work are presented. In Chapter 3 the thesis motivation is clearly stated, followed by a general overview of the proposed solution. Chapter 4 describes all the details related to the proposed design flow and the resulting hardware accelerator, whose evaluation is reported in Chapter 5. The conclusions are then presented in Chapter 6, along with some considerations on possible future work. 2

### **Background Knowledge**

In order to easily read through the rest of this thesis, a full understanding of the background is absolutely essential. Hence, in this chapter the state of the art of technologies, methodologies and key concepts relevant to this work are thoroughly examined. In Section 2.1 the Polyhedral Model (PM) is presented, as it will be employed to provide automatic information extraction from the input program, while in Section 2.2 Streaming-based Systems on Field Programmable Gate Arrays (FPGAs) are introduced, since the proposed architecture is streaming-based as well. Section 2.3 is instead dedicated to High Level Synthesis (HLS), because it is the technology that in this work allows to connect the PM with the generation of the architecture, and nonetheless substantially ease the hardware design, also enabling automation. Finally, in Section 2.4 focus is on Iterative Stencil Loops (ISLs), which are indeed the target of this entire work.

#### 2.1 Polyhedral Framework

In scientific and engineering applications, but in general in the great part of computationally intensive programs, most of the execution time is spent in nested loops. This obviously imply that the ability to perform loop nest restructuring towards optimization and parallelization is mandatory, although undoubtedly non-trivial. Standard compilers use in fact Intermediate Representations (IRs) such as *syntax trees, call trees, control-flow graphs* which are simply not appropriate to perform such a task, as the the kind of abstraction of those techniques inevitably hides certain properties and features of programs, making impossible to perform complex code transformations.

These limitations have created the need to develop techniques specifically aimed at optimizing loop nests, to be used in place of or in combination with standard compilers. A first attempt in this direction has been made in the eighties [89, 123], motivated by the need to map parallel computations onto systolic arrays [73]. It was based on the work of Karp et al. [63] that proposed a mathematical model which mapped onto uniform recurrence equations, which also inspired a series of fundamental papers from Feautrier [46, 47, 48, 49], arrived in the late eighties as well and quickly followed by other works related to the same topic, such as [119, 120, 15]. Those works provided a robust mathematical framework for regular imperative programs, and gave the basis to which is now known as the PM (sometimes called *Polytope Model*). The proposed model rapidly evolved and gained importance, as it allowed to map programs onto a mathematical representation, creating a solid link with algebra, as well as Operations Research (OR), thus making possible to extend their applicability also in the field of programs optimization. With the aid of the Polyhedral Model, loop optimization has reached the point in which a finely calibrated transformation can condense in a single step the equivalent of a significant number of textbook loop transformations [56, 13].

In the following section, a detailed overview of the polyhedral framework is then provided, starting from the model, described in section 2.1.1, and explaining what can be accomplished with such a model, which is the topic of section 2.1.2.

#### 2.1.1 Polyhedral Model

The PM has been proved to be a powerful tool for automatic optimization and parallelization. In fact, at the price of certain regularity conditions, this model can deliver very high standard in terms of execution time, throughput, number of processors and communication channels, memory requirements, and so on. It is indeed based on an algebraic representation of programs, whose manipulation allows to construct and search for complex sequences of optimizations.

This section precisely describe this model, giving a comprehensive overview of all the building blocks.

#### Mathematical Background

In order to understand the following concepts, this section provides the key definitions for polyhedral theory, the mathematical background on which the PM rests its foundations [82].

**Definition 2.1.1.** *Convex Set.* Given S a subset of  $\mathbb{R}^n$ . S is convex iff,  $\forall \mu, \lambda \in S$  and given  $c \in [0, 1]$ :

$$(1-c).\mu + c.\lambda \in S$$

A set is convex if for every pair of points within the object, drawing a line segment that joins the pair of points, each point on this segment is also in the set.

**Definition 2.1.2.** *Affine Function*. A function  $f: \mathbb{K}^m \to \mathbb{K}^n$  is affine if there exists a vector  $\vec{b} \in \mathbb{K}^n$  and a matrix  $A \in \mathbb{K}^{m \times n}$  such that:

$$\forall \vec{x} \in \mathbb{K}^n, f(\vec{x}) = A\vec{x} + \vec{b}$$

**Definition 2.1.3.** *Affine Spaces.* A set of vectors is an affine space iff it is closed under affine combinations.

A line in a vector space of any dimensionality is a one-dimensional affine space.

**Definition 2.1.4.** *Affine half-space*. An affine half-space of  $\mathbb{K}^m$  (affine constraint) is defined as the set of points:

$$\{\vec{x} \in \mathbb{K}^m | \, \vec{a}. \vec{x} \leqslant \vec{b}\}$$

**Definition 2.1.5.** *Affine hyperplane*. An affine hyperplane is an m - 1 dimensional affine sub-space of an m dimensional space.

An hyperplane divides the space into two *half-spaces*, the positive and negative half-space. Each half-space can be represented by an affine inequality.

**Definition 2.1.6.** *Polyhedron*. A set  $S \in \mathbb{K}^m$  is a polyhedron if there exists a system of a finite number of inequalities  $A\vec{x} \leq \vec{b}$  such that:

$$\mathcal{P} = \{ \vec{\mathbf{x}} \in \mathbb{K}^{\mathfrak{m}} | A \vec{\mathbf{x}} \leqslant \vec{\mathfrak{b}} \}$$

Equivalently, it can be defined as the intersection of finitely many half-spaces. Hence the representation as above, where each inequality corresponds to a face of the polyhedron.

**Definition 2.1.7.** *Parametric Polyhedron*. Given  $\vec{n}$  the vector of symbolic parameters,  $\mathcal{P}$  is a parametric polyhedron if it is defined by:

$$\mathcal{P} = \{ \vec{\mathbf{x}} \in \mathbb{K}^{\mathfrak{m}} | A\vec{\mathbf{x}} \leqslant B\vec{\mathfrak{n}} + \vec{\mathfrak{b}} \}$$

Definition 2.1.8. Polytope. A polytope is a bounded polyhedron.

**Definition 2.1.9.** *Integer Hull.* The integer hull of a rational polyhedron  $\mathcal{P}$  is the largest set of integer points such that each of these points is in  $\mathcal{P}$ .

**Definition 2.1.10.** *Lattice*. A subset *L* in  $\mathbb{Q}^n$  is a lattice if is generated by integral combination of finitely many vectors:  $a_1, a_2, ..., a_n(a_i \in \mathbb{Q}^n)$ .

$$L=L(\mathfrak{a}_1,...,\mathfrak{a}_n) = \{\lambda_1\mathfrak{a}_1 + ... + \lambda_n\mathfrak{a}_n | \lambda_i \in \mathbb{Z}\}$$

If the  $a_i$  vectors have integer coordinates, *L* is an integer lattice.

**Definition 2.1.11.**  $\mathbb{Z}$ -*polyhedron.* A  $\mathbb{Z}$ -polyhedron is the intersection of a polyhedron and an affine integral full dimensional lattice.

$$\mathfrak{P}' = \mathbb{Z}^{\mathfrak{n}} \cap \mathfrak{P}$$

#### 2. BACKGROUND KNOWLEDGE

#### Static Affine Nested Loop Program

Let us start with the most generic definition for the PM, as it provides the conditions for given a program to be described in the PM.

**Definition 2.1.12.** *Static Affine Nested Loop Program (SANLP)* [76]. A SANLP consists of a set of statements and function calls, each possibly enclosed in loops and/or guarded by conditions. The loops do not have to be perfectly nested. All lower and upper bounds of the loops as well as all expressions in conditions and array accesses have to be affine functions of enclosing loop iterators and static parameters. The parameters are symbolic constants, so their values can not change during the execution of the program. Data communication between function calls must be explicit.

#### **Static Control Parts**

The next definition that comes after SANLP, moving to a finer granularity, it the one of Static Control Parts (SCoPs). A SCoP is a subclass of general loops nests that can be represented in the polyhedral model [24].

**Definition 2.1.13.** *Static Control Part.* A SCoP is a maximal set of consecutive instructions such that:

- the control structures are only *for* loops or *if* conditionals

- loop bounds and conditionals are affine functions of the surrounding loop iterators and the global parameters (values unknown at compilation time, but constant).

Even if the definition of SCoPs may seem restrictive, a pre-processing stage can extend its applicability.

As said, SCoPs are a set of statements. A *polyhedral statement* is the atomic dowel of polyhedral representation, and can be defined as:

**Definition 2.1.14.** *Polyhedral Statement*. A polyhedral statement is a program instruction that:

- is not an if conditional statement with an affine condition

- is not a for loop statement with affine loop bounds

- has only affine subscript expressions for array accesses

- does not generate control-flow effects

The resulting statements in the polyhedral representation may differ from those in the input source code, because the compiler may change the internal representation.

# **Iteration Domain**

Iteration Domains capture the dynamic instances of all statements - *i.e.* all possible values of surrounding loop iterators - through a set of affine inequalities. In order to get to the definition in a rigorous manner, let us first of all define what an *iteration vector* is:

**Definition 2.1.15.** *Iteration Vector.* For a polyhedral statement, the iteration vector of a multi-level loop nest over a m-dimensional grid is a vector of iteration variables,  $\vec{i} = (i_0, i_1, ..., i_{m-1})^T$ , where  $i_0, ..., i_{m-1}$  are the iteration variables from outermost to innermost loop.

Starting from the iteration vector, the Iteration Domain can be defined as:

**Definition 2.1.16.** *Iteration Domain* [48]. The Iteration Domain (ID)  $\mathcal{D} \subseteq \mathbb{Z}^m$  is the set of iteration vectors of the loop nest, and is expressed by a set of linear inequalities  $\mathcal{D} = \{\vec{i} | P\vec{i} \ge \vec{b}\}$

Each integral point inside this polyhedron corresponds to exactly one execution of a statement, and its coordinates in the domain matches the values of the loop iterators at the execution of this instance. This model let the compiler manipulate statement execution and iteration ordering at the most precise level.

Notice that, to model IDs whose size are known only symbolically at compiletime, parametric polyhedra are used.

Since the definitions of iteration vector and ID have just been introduced, the notion of lexicographic order can now be provided, as it will be useful to effectively model both *data dependencies* and *schedules*.

**Definition 2.1.17.** *Lexicografic Order* [48]. Lexicographic order relation  $\succ_1$  of two iteration vectors  $\vec{i}$  and  $\vec{j}$  is defined as:

$$\vec{i} \succ_{l} \vec{j} \Leftrightarrow (i_{0} > j_{0}) \lor (i_{0} = j_{0} \land i_{1} > j_{1}) \lor (i_{0} = j_{0} \land i_{1} = j_{1} \land i_{2} > j_{2}) \lor \dots$$

$$\lor (i_{0} = j_{0} \land \dots \land i_{m-2} = j_{m-2} \land i_{m-1} > j_{m-1})$$

# Data dependencies

The modeling of data dependencies is crucial for the effectiveness of the PM, since not all program transformations preserve the semantics, and the semantic is automatically preserved if the dependencies are preserved. Here, some important definitions for data dependency analysis and representation are given. Firstly, an essential definition to model the dependencies in the PM is the *subscript function*, as well as the notion of *image* and *preimage*.

**Definition 2.1.18.** Subscript Function [20]. Given the set of array  $A_P$  of a program P, a reference to an array  $B \in A_P$  in a statement  $S \in S_P$  is written  $\langle B, f \rangle$ , where f is the subscript function. If f is affine it can be written as  $f(\vec{x}) = F\vec{x} + \vec{a}$  where F is the subscript matrix,  $\vec{a}$  is a constant vector.

$f_{s}(\vec{x}_{S2}) = \begin{bmatrix} 1 & 0 & 0 & 0 \end{bmatrix} \cdot \begin{pmatrix} \vec{x}_{S2} \\ n \\ 1 \end{pmatrix}$ for (i = 0; i <= n; ++i) { s[i]=0;for (j = 0; j <n; ++j) s[i]=s[i]+a[i][j]\*x[j];}  $f_{a}(\vec{x}_{S2}) = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix} \cdot \begin{pmatrix} \vec{x}_{S2} \\ n \\ 1 \end{pmatrix}$   $f_{x}(\vec{x}_{S2}) = \begin{bmatrix} 0 & 1 & 0 & 0 \end{bmatrix} \cdot \begin{pmatrix} \vec{x}_{S2} \\ n \\ 1 \end{pmatrix}$

Figure 2.2: Subscript Function Example. The three subscript functions are relative to the three array accesses for s, a and x.

**Definition 2.1.19.** *Image*. The image of a polyhedron  $\mathcal{P} \in \mathbb{Z}^n$  by an affine function  $f: \mathbb{Z}^n \to \mathbb{Z}^m$  is a  $\mathbb{Z}$ -polyhedron  $\mathcal{P}'$ :

$$\mathcal{P}' = \{ f(\vec{x}) \in \mathbb{Z}^m | \vec{x} \in \mathcal{P} \}$$

**Definition 2.1.20.** *Preimage*. The preimage of a polyhedron  $\mathcal{P} \in \mathbb{Z}^n$  by an affine function  $f:\mathbb{Z}^n \to \mathbb{Z}^m$  is a  $\mathbb{Z}$ -polyhedron  $\mathcal{P}'$ :

$$\mathfrak{P}' = \{ \vec{\mathbf{x}} \in \mathbb{Z}^n | \mathbf{f}(\vec{\mathbf{x}}) \in \mathfrak{P} \}$$

The image of a polyhedron by an affine invertible function is a  $\mathbb{Z}$ -polyhedron. The image of a polyhedron by a subscript function  $f_A$  in an ID  $\mathcal{D}_S$  is the set of cell of A accessed from the statement S.

Thanks to those notion, the *data domain* (or *data space*) of a given array reference can be easily modeled. In fact, it is enough to compute the image of the ID of the statement by the reference subscript function.

Within the context of PM dependencies analysis, there is another important definition that must be provided, as it can be useful to check for the legality of a given transformation, but it can be employed for a whole lot of other purposes. This definition is the so called *data distance vector*, which comes together with the definitions of *lexicographically non-negative distance vector* and as an extension the *legality* condition for a given distance vector.

**Definition 2.1.21.** *Data Distance Vector*. Consider two subscript functions  $f_A^R$  and  $f_A^S$  to the same array A of dimension n. Let v and  $\sigma$  be two iteration of the innermost loop. The data distance vector is defined as an n-dimensional vector:

$$\delta(\mathbf{v}, \mathbf{\sigma})_{f_A^R f_A^S} = f_A^R(\mathbf{v}) - f_A^S(\mathbf{\sigma})$$

**Definition 2.1.22.** *Lexicographically non-negative Distance Vector*. A distance vector v is lexicographically non-negative when the left-most entry in v is positive or all elements of v are zero.

**Definition 2.1.23.** *Legal Distance Vector*. A distance vector is legal when it is lexi-cographically non-negative (assuming that indices increase).

In order to easily define the notion of *polyhedral dependency*, there is first the need to provide some introductory definitions, the first being the *Bernstein conditions*.

**Definition 2.1.24.** *Bernstein Conditions* [28]. Given two references, there exists a dependency between them if the three following conditions hold:

- they reference the same memory location;

- one of this access is a write;

- the two associated statements are executed;

Let us consider two statement *instances*,  $S_0$ ,  $S_1$ , with  $S_0$  occurring before  $S_1$ , there are three categories of dependencies that can be identified [58]:

- **Read After Write (RAW)**, S<sub>1</sub> reads what is written by S<sub>0</sub>. If the dependency is not respected, S<sub>1</sub> incorrectly gets the old value.

- Write After Read (WAR), S<sub>1</sub> write a destination after reading from S<sub>0</sub>. If the dependency is not respected, S<sub>0</sub> incorrectly gets the new value.

- Write After Write (WAW), S<sub>1</sub> write to a memory location after S<sub>0</sub>. If the dependency is not respected, the writes end up being performed in the wrong order, leaving the value written by S<sub>0</sub> rather than the value written by S<sub>1</sub> in the destination.

As already stated, to preserve the semantic of the program, *instances* containing dependent references should not be executed in a different order. [82] classifies the dependency relation into three kinds:

- Uniform dependencies: the distance between dependent iteration remains constant

- Non-Uniform dependencies: during the execution the distance between dependent iterations varies

- **Parametric dependencies**: the distance between two dependent relation is expressed regarding to, at least one parameter

Finally, let us define when two statements are said to be *in dependence* in the PM, leveraging the previously given definitions:

**Definition 2.1.25.** *Dependency of statement instances.* A statement *S* depends on a statement *R* ( $\mathbb{R} \rightarrow S$ ), if there exists an operation  $S(\vec{x}_S)$  and  $R(\vec{x}_R)$  and a memory location *m* such that:

- *S*(*x*<sub>S</sub>) and *R*(*x*<sub>R</sub>) refer to the same memory location *m*, and at least one of them writes to that location

- *x*<sub>*R*</sub> and *x*<sub>*S*</sub> belongs to the ID of *R* and *S*

- in the original sequential order,  $S(\vec{x}_S)$  is executed after  $R(\vec{x}_R)$ .

To effectively model dependencies between statements, a Data Dependency Graph can be employed.

**Definition 2.1.26.** *Data Dependency Graph.* A Data Dependency Graph (DDG) G = (V, E) is a directed multi-graph with each vertex representing a statement. An edge  $e \in E$ , from R to S represent a dependency between the source and target, due to a conflict access in R and S.

Another useful representation in polyhedral theory is the *dependence polyhedron*, used in combination with the DDG. The dependency polyhedron provides the relation between the instances of the statements S and R. It is possible to obtain this kind of information because there exists an affine relation between the iterations and the accessed data for regular programs, that can be obtained thanks to the previously defined subscript function. Before providing the definition of the dependence polyhedron, there is first the need to introduce the involved elements. First of all, the ID (being a set of affine inequalities) of S and R can be described as  $A_S \vec{x}_S + c_S \ge 0$ , and  $A_R \vec{x}_R + c_R \ge 0$ , where  $\vec{x}_S$  and  $\vec{x}_R$  are the iteration vectors of S and R. A dependence between S and R means that they refer to the same memory location, which implies that the two subscript functions are equal, hence  $F_S \vec{x}_S + a_S = F_R \vec{x}_R + a_R$  (both expressed as in definition 2.1.18). There is also a precedence order between S and R, at the given *dependence level*, *i.e.* the common loop depth l in which the dependency takes place. For each dependence level l, the precedence constraints are:

• the equality of the loop index variables at any depth lesser to l:

$$x_{R,i} = x_{S,i} \quad \forall i < l$$

• S is executed after R at the common depth l:

$x_{R,l} < x_{S,l}$

If S and R does not share any loop, there is no additional constraint and the dependence only exist if S is syntactically after R. These constraints can be expressed using linear inequalities, *i.e.*  $P_{l,S}\vec{x}_S - P_{l,R}\vec{x}_R + b \ge 0$ .

**Definition 2.1.27.** *Dependence Polyhedron*. The dependence polyhedron  $\mathcal{D}_{\mathsf{R},\mathsf{S},f_{\mathsf{R}},f_{\mathsf{S}},l}$  for  $\mathsf{R} \rightarrow \mathsf{S}$  at a given level *l* and for a given pair of references  $f_{\mathsf{R}}, f_{\mathsf{S}}$  is described as:

$$\mathcal{D}_{\mathsf{R},\mathsf{S},f_{\mathsf{R}},f_{\mathsf{S}},l}:\mathsf{D}_{\mathsf{R},\mathsf{S}}\left(\begin{array}{c}\vec{\mathsf{x}}_{\mathsf{R}}\\\vec{\mathsf{x}}_{\mathsf{S}}\end{array}\right) + \vec{d}_{\mathsf{R},\mathsf{S}} = \left[\begin{array}{c}\mathsf{F}_{\mathsf{R}} & -\mathsf{F}_{\mathsf{S}}\\\vec{\mathsf{A}}_{\mathsf{R}} & 0\\0 & \mathsf{A}_{\mathsf{S}}\\\mathsf{P}_{\mathsf{R}} & -\mathsf{P}_{\mathsf{S}}\end{array}\right] \left(\begin{array}{c}\vec{\mathsf{x}}_{\mathsf{R}}\\\vec{\mathsf{x}}_{\mathsf{S}}\end{array}\right) + \left(\begin{array}{c}\mathfrak{a}_{\mathsf{R}} - \mathfrak{a}_{\mathsf{S}}\\\mathsf{c}_{\mathsf{R}}\\\mathsf{c}_{\mathsf{S}}\\\mathsf{b}\end{array}\right) \stackrel{=0}{\geqslant \vec{\mathsf{0}}}$$

Given all the definitions above, the **Polyhedral Model** can be finally defined:

**Definition 2.1.28.** *Polyhedral Model* [113]. The *polyhedral model* of a sequential program consists of a list of statements represented by:

- an identifier;

- a dimension d<sub>i</sub>;

- an ID;

- a list af accesses;

- a location;

A subscript function and a type (read or write) are associated to each array.

# Schedules

The ID does not describe the order in which each statement instance has to be executed with respect to other instances. A *scheduling* function specifies a virtual timestamp for each instance of a corresponding statement, providing an order relation between statement instances. Hence, statement instances will be executed according to the increasing order of the timestamp. If two instances have the same timestamp can run in parallel.

Figure 2.4: A simple schedule example. In this picture, the statement on the left has an *identity schedule*, as the statement instances are trivially the points (i, j) within the statement ID.

**Definition 2.1.29.** *Affine Schedule* [81]. Given a statement *S*, a p-*dimensional affine schedule*  $\Theta_S$  is an affine form on the outer loop iterators  $\vec{x}_S$  and the global parameters  $\vec{n}$ .

$$\Theta_{S}(\vec{x}_{S}) = T_{S} \begin{pmatrix} \vec{x}_{S} \\ \vec{n} \\ 1 \end{pmatrix}, T_{S} \in \mathbb{K}^{p \times \dim(\vec{x}_{S}) + \dim(\vec{n}) + 1}$$

A schedule assigns a timestamp to each executed instance of a statement. A schedule can be:

- **One-dimensional**, if T is a vector;

- Multidimensional, if T is a matrix.

A one-dimensional schedule express the program as a single sequential loop, while a multidimensional schedule expresses the program as one or more nested sequential loops [84].

There are however *schedules* which by construction are *not legal, i.e.* they enforce an execution order which violates the dependencies. The following definitions are essential to model this condition in the PM.

**Definition 2.1.30.** *Precedence Condition.* Given  $\Theta_R$  a schedule for the instance of R,  $\Theta_S$  a schedule for the instances of S.  $\Theta_R$  and  $\Theta_S$  are legal schedules if  $\forall \langle \vec{x}_R, \vec{x}_S \rangle \in \mathcal{D}_{R,S,f_R,f_S,l}$  (*i.e.* for each instance of R and S in dependence, as specified in the corresponding dependence polyhedron  $\mathcal{D}_{R,S,f_R,f_S,l}$ ):