## Politecnico di Milano Department of Electronics, Information, and Bioengineering Doctoral Programme in Information Technology

# Towards Improving Programmability of Heterogeneous Parallel Architectures

Doctoral Dissertation of:

Michele Scandale

Advisor:

Prof. Giovanni Agosta

Tutor:

Prof. Andrea Bonarini

The chair of the Doctoral Program:

Prof. Carlo Fiorini

## Acknowledgements

The description of my study path along the last four years, at the beginning as research assistant and then as a Ph.D. student, can not be summarized in few lines of acknowledgements. Everything started with my dream at the end of my master of science to acquire strong skills and experience in the wonderful field of compilation techniques. The experience of the Ph.D. is the first step forward to transform my dream into reality.

First of all, I would like to thank my advisor prof. Giovanni Agosta, for giving me the unique possibility to work on topics related to parallel programming and compiler technologies. Thanks to prof. Gianfranco Lamperti, my master thesis advisor, and prof. Stefano Crespi Reghizzi I was able to met prof. Giovanni Agosta and his team.

From the compiler group I would like to thank Ettore Speziale and Michele Tartara for the initial bootstrap in the compiler development and parallel programming worlds, my colleagues Michele Beretta and Alessandro Di Federico, that worked with me in the development and support of the OpenRISC toolchain, and finally master students Giulio Sichel and Marco Bonacina that contributed in the development of OpenCRun.

Indeed, I would like to thank prof. Gerardo Pelosi and Alessandro Barenghi for granting me the possibility to explore the mysterious world of applied cryptography within my minor research topic, and indeed for the useful hints and support provided during my Ph.D. career.

Furthermore, I would like to Marco Cornero for the great experience during my internship in ARM Ltd., granting me the possibility to deeply work on GPU compiler technologies and architectures, and exploring the new features of the next generation of programming models for tightly coupled CPU-GPU platforms.

A special thanks goes again to the people from DEIB office no. 127, Giovanni Agosta, Gerardo Pelosi, Alessandro Barenghi, Ettore Speziale, Michele Tartara, Michele Beretta, Alessandro Di Federico, with whom I shared during the last four years at Politecnico di Milano a great experience with lot of fun and great results.

Finally, I would like to thank my parents and my friends for support to "survive" during this convoluted experience.

### **Sommario**

La computazione parallela è da lungo tempo considerata una tecnica efficace per combinare prestazioni ed efficienza energetica. A partire dal High Performance Computing (HPC) fino ai moderni sistemi embedded, l'adozione di architetture parallele eterogenee diventa una pratica sempre più comune, dato che queste consetono di raggiungere un buon compromesso in termini di efficienza energetica. Il raggiungimento di prestazioni exascale per la prossima generazione di sistemi HPC è vincolata da un consumo complessivo tra i 20 MW e 30 MW. Gli attuali sistemi HPC "green" non sono tuttavia in grado di raggiungere questo grado di efficienza nonostante l'utilizzo di moderne architetture parallele eterogenee. Infine, le piattaforme hardware ultra-low-power guadagnano sempre più visibilità dato che possono essere componenti chiave per consentire ai prossimi sistemi HPC di raggiungere il livello di efficienza necessaria per raggiungere l'obiettivo exascale.

La programmabilità di quesi sistemi è un aspetto critico che ha un forte impatto sull'efficienza raggiungibile e ancor di più nel costo per ottenere tale obiettivo. Programmare architetture parallele è un'operazione complessa, dato che generalemente molte caratteristiche hardware sono esposte completamente e direttamente ai programmatori. Per questo motivo esistono infrastrutture di programmazione che cercano di nascondere questa complessità, tuttavia le prestazioni ottenibili sono sub-ottime rispetto ad implementazioni dedicate, o sono infrastrutture limitate a specifici domini applicativi.

In questa tesi si affrontano le sfide legate alla programmabilità di architetture parallele eterogenee, operando su modelli di programmazione e architetture sia esistenti che futuri. In particolare, si presenta OpenCRun, un runtime OpenCL che supporta varie piattaforme con caratteristiche molto differenti tra loro, come multi-core X86 e acceleratori paralleli embedded. Nell'ambito delle architetture ultra-low-power, si presentano i risultati della collaborazione tra sviluppatori hardware e software per la piattaforma PULP, mostrando i benefici di oculate estensioni della ISA e il corrispettivo supporto nel compilatore per massimizzare l'efficienza energetica della piattaforma. Inoltre, per migliorare la portabilità funzionale e prestazionale di codice OpenCL tra GPGPU e acceleratori many-core embedded con memorie esplicitamente gestite

come PULP e STHorm, si presenta una trasformazione, work-item coalescing, che supera le limitazioni mostrate dalle piattaforme embedded, e una ottimizzazione dei trasferimenti di memoria per incrementare le prestazioni del codice finale. Al fine poi di innalzare il livello di astrazione in modo più radicale, assumendo piattaforme dotate di memoria virtual condivisa in quanto caratteristica hardware attesa a breve nelle prossime generazioni di piattaforme eterogenee, si presenta un metodo per implementare puntatori a funzione condivisi in piattaforme eterogenee con due o più ISA, un mattone fondamentale per ottenere il supporto al linguaggio C++ tra ISA eterogenee. In aggiunta si presenta un meccanismo per supportare chiamate a funzione il cui codice non è presente per il dispositivo invocante. Tale meccanismo è necessario per ottenere un supporto trasparente del linguaggio C++ e fornire una maggiore flessibilità ai programmatori che lavorano con applicazioni complesse per portarle all'utilizzo di acceleratori paralleli eterogenei.

#### **Abstract**

Parallel computing has been considered an effective approach to combine performance and power efficiency for a long time. Starting from High Performance Computing (HPC) to modern embedded systems, the employment of heterogeneous parallel architectures is becoming the common case, since they provide a good tradeoff in terms of power efficiency. The exascale objective for the next generation of HPC systems is constrained to a target power envelope ranging from 20 MW to 30 MW. The existing "green" HPC systems are not yet able to reach the such power efficiency although they already employ modern heterogeneous parallel architectures. Ultra-low-power hardware platforms are gaining an increasing traction, as they may represent the key component to allow future HPC systems to match the required power efficiency.

The programmability of such systems is a critical aspect that has an huge impact on the reachable power efficiency and the effort required to reach such target. Programming parallel architectures is a complex task, since many hardware features are directly exposed to the programmers. Programming frameworks that try to hide such complexity exist, however they either provide only sub-optimal performance with respect to hand tuned implementations, or they are limited to specific application domains.

This dissertation tackles challenges related to the programmability of heterogenous parallel architectures, acting on both existing and future programming models and hardware architectures. In particular, we present OpenCRun, an OpenCL runtime implementation supporting a range of platforms with very different architectures characteristics, such as X86 multicores and embedded parallel accelerators. In the context of ultra-low-power architectures we report the joint effort between hardware and software developers towards the PULP platform, showing the benefits of selected ISA extensions and their compiler support to maximize the power efficiency. Moreover, to improve functional and performance portability of OpenCL code between GPGPUs and embedded many-core accelerators with explicitly managed memory such as PULP and STHorm, we have proposed a code transformation technique, work-item coalescing, that bypasses the limitations of the embedded platforms, allowing code developed for GPGPU to be ported seamlessly, as

well as a memory transfer optimization technique to tune the resulting code to improve performance. Finally, to increase the abstraction level in a more radical way, leveraging Shared Virtual Memory that is expected to be available in future architectures, we have presented a method to transparently implement shared function pointers in heterogeneous platforms with two or more ISAs, a building block for enabling full C++ support across heterogeneous ISAs. Indeed we presented a fallback solution to implement function calls from device side to functions not available on the device itself. This mechanism is needed to enable the transparent support of C++, and to provide more flexibility to the programmers dealing with large and complex applications to be ported towards heterogeneous parallel accelerators.

## **C**ontents

| In | trodu | ction                                               | 1  |  |  |

|----|-------|-----------------------------------------------------|----|--|--|

| 1  | Para  | Ilel Computing                                      | 5  |  |  |

|    | 1.1   | Introduction                                        | 5  |  |  |

|    | 1.2   | Hardware: evolution of computer architectures       | 6  |  |  |

|    |       | 1.2.1 Flynn's Taxonomy                              | 7  |  |  |

|    |       | 1.2.2 Single-core architectures                     | 7  |  |  |

|    |       | 1.2.3 Multi-core architectures                      | 9  |  |  |

|    |       |                                                     | 12 |  |  |

|    |       |                                                     | 19 |  |  |

|    | 1.3   |                                                     | 20 |  |  |

|    |       |                                                     | 22 |  |  |

|    |       | 1.3.2 Comparison                                    | 28 |  |  |

|    | 1.4   | Conclusion                                          | 31 |  |  |

| 2  | Soft  | ware/Hardware Architecture                          | 33 |  |  |

|    | 2.1   |                                                     | 33 |  |  |

|    | 2.2   | OpenCRun                                            | 34 |  |  |

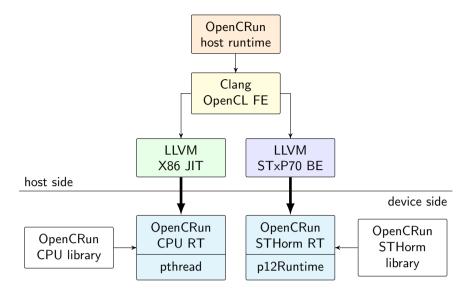

|    |       | 2.2.1 Host-runtime architecture                     | 35 |  |  |

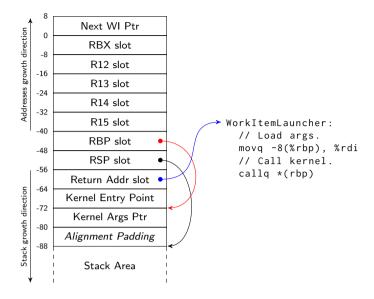

|    |       | 2.2.2 CPU device                                    | 36 |  |  |

|    |       | 2.2.3 STHorm device                                 | 37 |  |  |

|    |       | 2.2.4 OpenCL builtin library                        | 38 |  |  |

|    | 2.3   |                                                     | 39 |  |  |

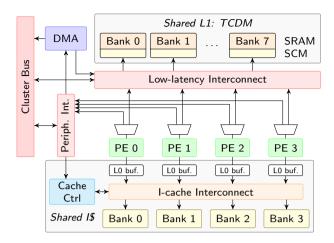

|    |       | 2.3.1 Overview of the Platform                      | 41 |  |  |

|    |       | 2.3.2 Instruction-Set Extensions for OpenRISC       | 43 |  |  |

|    |       | 2.3.3 Implementation in the ULP-Cluster             | 47 |  |  |

|    |       | 2.3.4 Performance, Area, And Power Results          | 49 |  |  |

|    | 2.4   | Conclusion                                          | 53 |  |  |

| 3  | Cros  | s-Platform Functionality and Performance for OpenCL | 55 |  |  |

|    | 3.1   |                                                     | 55 |  |  |

|    | 3.2   | Preliminaries on OpenCL and Background 5            |    |  |  |

|    | 3.3   | Kernel Transformations                              | 60 |  |  |

|    |       | 3.3.1 Work-item Coalescing                          | 61 |  |  |

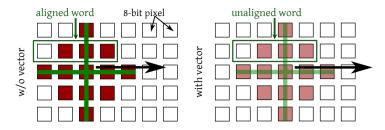

|    |       | 3.3.2 Memory Transfers Optimization                 | 64 |  |  |

#### Contents

|     | 3.4    | Evaluation                                             | 66  |

|-----|--------|--------------------------------------------------------|-----|

|     | 3.5    | Related Work                                           | 70  |

|     | 3.6    | Conclusion                                             |     |

| 4   | C+-    | + Support across Heterogeneous Systems                 | 73  |

|     | 4.1    | Introduction                                           | 73  |

|     | 4.2    | Transparent Function Pointers                          | 76  |

|     | 4.3    | Integrating C++ Support across Heterogeneous Systems . | 82  |

|     |        | 4.3.1 Virtual member functions                         | 83  |

|     |        | 4.3.2 Generalized system calls                         | 86  |

|     |        | 4.3.3 Other C++ features                               | 88  |

|     |        | 4.3.4 Heterogeneous Linker                             | 88  |

|     | 4.4    | Evaluation                                             | 91  |

|     | 4.5    | Related Work                                           | 94  |

|     | 4.6    | Conclusion                                             | 95  |

| Co  | onclus | sion                                                   | 95  |

| Lis | st of  | Figures                                                | 99  |

| Lis | st of  | Tables                                                 | 102 |

| Bi  | bliog  | raphy                                                  | 105 |

#### Introduction

Parallel computing has been considered an effective approach to combine performance and power efficiency for a long time. Originally, highly parallel architectures were designed primarily for application specific purposes in the field of High Performance Computing (HPC) – typically solving large simultaneous equation sets by means of finite elements methods, tackling problems coming from metereology and fluidodynamics among the others. More recently, the application of parallel computing to computer graphics and the shift from fully-dedicated graphics hardware to programmable graphic accelerators has brought this kind of massively parallel hardware into the domain of general purpose computing, and from there back into HPC.

At the same time, in embedded computing smaller-scale parallelism has been exploited primarily to achieve energy-efficiency – e.g. through Very Long Instruction Word architectures.

Nowadays, there is a widespread trend towards convergence between systems targeting very different domains.

HPC systems are increasingly built using heterogeneous components such as General Purpose Graphics Processor Units (GPGPUs), with the goal of achieving significant gains in terms of the FLOPS/W metric – the target power envelope for future exascale system ranges between 20 MW and 30 MW. Such "Green" HPC systems are espected to make HPC facilities available to a wide range of smaller-scale clients, expanding the industrial application of HPC from a few capital intensive domains (e.g., oil & gas, financial services) to SMEs in fields such as drug design, mechanical engineering, and so on.

High-end embedded systems feature programmable graphics accelerators. These architectures are clearly moving towards laptop- or even desktop-grade capabilities, with applications e.g. in gaming.

Finally, ultra-low-power hardware platforms are being designed around the concept of a fabric of numerous, very small processing elements loosely coupled to a host processor. Such architectures target a range of application domains that are gaining increasing traction, such as mobile image processing for autonomous vehicles.

Heterogeneity seems to be the common denominator of these architectures – combining larger cores for processing control-intensive tasks with smaller but numerous cores for processing data-parallel tasks allows, through appropriate resources management, to limit energy consumption while guaranteeing Quality of Service. This heterogeneity, however, comes at a cost – programming heterogeneous platforms is all but an easy task, since these platforms and the programming models built for them tend to leave to the programmer the explicit management of data allocation and communication.

Currently, industry standards such as OpenCL [50] are employed to program heterogeneous, massively parallel platforms. OpenCL supports functional and performance portability, albeit by exposing both to the programmer through platform introspection capabilities – the programmer is in charge to read the platform capabilities and encode in his application all the necessary logic to optimize code execution, or even simply make it possible on a range of different platforms. Typically, programmers tends to focus on just a set of platforms that are optimal for their application domain, foregoing performance and even functional portability to other classes of hardware platforms.

While this may appear sufficient for current purposes, the fast evolution of hardware platforms in all of the computing continuum may easily mean that code written today for an HPC application may need to be rewritten entirely, leading to a slow-down of adoption of new architectures and to increased development costs.

#### **Contributions**

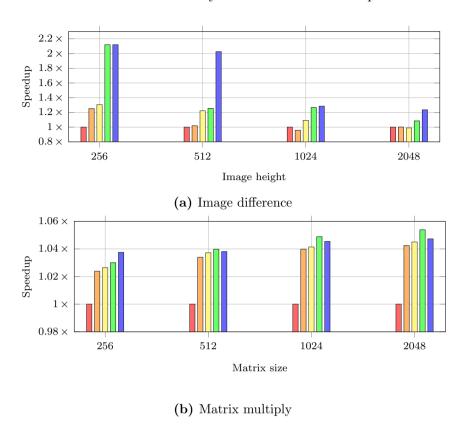

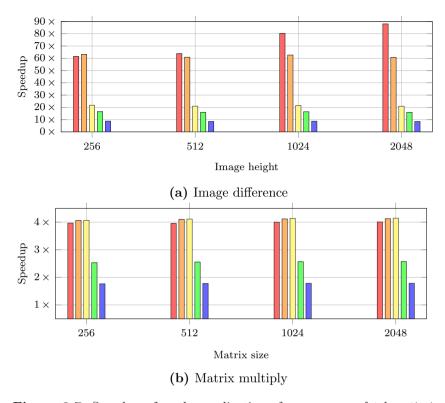

In this work, we tackle the abovementioned issue through a two pronged approach. On one hand, we aim at providing improved functional and performance portability to OpenCL code through compiler transformations for low-end parallel architectures. We believe that such techniques will become relevant to other application domains, up to HPC, as hardware approaches more commonly found in embedded systems become prevalent in higher-scale systems to cope with the power wall. maximizing the performance on heterogeneous parallel architectures, OpenCL applications are usually written in a target specific way, affecting the portability the application code itself. A common source of non-portability for embedded heterogeneous parallel architectures is represented by hard constraints on the work-group size. In the general case the work-items in a work-group cooperate together exploiting local memories, thus work-groups reshaping may not be applicable. Chapter 3 shows how to transparently run OpenCL applications presenting non native work-group sizes on embedded heterogeneous accelerators. Indeed, it shows a compiler transformation that introduce double-buffering in order to exploit DMA units available on such embedded platforms.

On the other hand, we look at future parallel architectures featuring Shared Virtual Memory, and, aiming at providing a radically simpler programming model, we simplify host/device interaction by allowing a fully transparent programming model, abstracting the coexistence of multiple Instruction Set Architectures (ISA) and Application Binary Interfaces (ABI). Chapter 4 presents a very efficient implementation of shared function pointers on ISA-heterogeneous architectures, as well as a transparent programming model employing full C++ support. The function pointer support in the heterogeneous context is a key component for exploiting the shared virtual memory mechanism. From the programmer perspective, the proposed approach ensures the complete sharing of both code and data between host and device. This mechanism allows the full C++ support on heterogeneous systems, providing a simpler but much more flexible programming model that allows the porting of large C++ application towards the use of heterogeneous parallel platform in a incremental fashion with a reduced programming effort, since no strong restriction are applied to the code will be promoted to computational parallel kernel.

The baseline for our work is provided by the Open Source OpenCL runtime we have developed, OpenCRun, which we also describe in this thesis.

#### Organization of the dissertation

The rest of this dissertation is organized as follow. Chapter 1 introduces the world of parallel computing, from both the hardware and software perspective. Chapter 2 presents the software architecture developed as baseline for this work, and the contribution on the PULP platform definition in the context of ultra low-power parallel accelerators. Chapter 3 deals with the problem of portability of OpenCL application between GPGPUs and embedded parallel accelerators. Chapter 4 discusses about the challenges and solutions for full C++ support on heterogeneous parallel architectures. Concluding remarks close this dissertation.

## 1 Parallel Computing

To understand the requirements imposed on future programming models for parallel computing and the gap with respect to the state of the art, it is necessary to analyze the historical evolution of the field, as well as the current and future trends. Therefore, we present the evolution of hardware architectures starting from uni-processors to many-core architectures discussing the evolution path of hardware architectures, and the converging point of modern heterogeneous parallel architectures. We then discuss parallel programming models for multi-cores and many-cores architectures, pros and cons in terms of programmability of the underlying architecture versus the ability to exploit the available hardware features.

#### 1.1 Introduction

High Performance Computing (HPC) has been traditionally the domain of grand scientific challenges and a few industrial domains such as oil & gas or finance, where investments are large enough to support massive infrastructures. However, nowadays HPC has been recognized as a powerful tool to increase the competitiveness of nations and their industrial sector, including small scale but high-tech businesses – to compete, you must compute has become an ubiquitous slogan [26].

The current road-maps [2, 85] for HPC systems aim at reaching exascale levels (10<sup>18</sup>FLOPS) within 2023 – a ×1000 improvement over petascale, which was reached in 2009, and a ×100 improvement over current systems. Reaching exascale poses the additional challenge of significantly limiting the energy envelope while providing massive increases in computational capabilities – the target power envelope for future exascale system ranges between 20 MW and 30 MW. Thus, a distinct class of HPC systems, dubbed Green HPC systems, are being designed aiming at maximizing a FLOPS/Watt metric, rather than the typical FLOPS one. Such systems are increasingly moving towards heterogeneous architectures employing GPGPUs as accelerators - in the November 2014 Green500 list, the top 23 systems have parallel accelerators. The efficiency of such heterogeneous systems is more than double that of homogeneous ones (i.e., 5271 MFLOPS/W vs. 2304 MFLOPS/W

considering the 1st and 24th entries of the current Green 500 ranking www.green500.org). This level of efficiency is still one order of magnitude lower than that needed for supporting exascale systems at the target power envelope of 20 MW. To this end, European efforts have been focused towards building supercomputers out of the less powerhungry ARM cores and GPGPUs [40, 74]. On the semiconductor industry side, the wide margin provided by modern chip manufacturing techniques, combined with the inability to exploit this silicon headroom to produce faster, more complex cores due to the breakdown of Dennard scaling, has given rise to a pervasive diffusion of a number of parallel computing architectures, up to the point where embedded systems are also characterized by multi-core processors. The large design effort has led to a variety of approaches in terms of core interconnection and data management. Thus, the ability to port applications designed for current platforms, based on GPGPUs like the NVIDIA Kepler or Tesla families, to heterogeneous systems such as those currently designed for embedded systems is critical to provide software support for future HPC.

Designing and implementing HPC applications is a difficult art, which requires mastering many specialized languages and tools for performance tuning. This is incompatible with the current drive of opening HPC infrastructures to a much wider range of users – the current model of having the HPC center staff directly support the development of the application will become unsustainable in the long run. Thus, the availability of effective standard programming languages and APIs is critical to provide migration paths towards novel heterogeneous HPC platforms as well as to guarantee the ability of developers to work effectively on these platforms.

In the following, Section 1.2 presents the evolution of hardware architectures starting from uni-processors to many-core ones discussing the evolution path of hardware architectures, and the converging point of modern heterogeneous parallel architectures, while Section 1.3 discusses parallel programming models for multi-cores and many-cores architectures, pros and cons in terms of programmability of the underlying architecture versus the ability to exploit the available hardware features.

#### 1.2 Hardware: evolution of computer architectures

Starting from the beginning of the Computer science, hardware has driven the evolution of languages, programming models and software architectures. The main goal of the evolution of hardware architectures has been the improvement of the running time of applications. De-

pending on the application domain and the target requirements, several strategies have been proposed.

#### 1.2.1 Flynn's Taxonomy

Flynn's taxonomy [35] is a useful classification of the main directions of the computer architecture evolution. In Flynn's taxonomy the hardware is modelled as a set of processing units, executing program instructions fetched from an instruction pool employing an instruction stream. Data is stored in a data pool, and accessed employing a data stream. The classification considers the number of processing units and how they are connected to the instruction and data pools.

**Single Instruction Single Data (SISD)** There is only a single processing unit, and a single data stream. This was the architecture dominating the general purpose market up to year 2005. Nowadays it represents a building block for large multi-cores, and it is used in embedded low-power devices, such as low end micro-controllers.

**Single Instruction Multiple Data (SIMD)** There are multiple processing units executing the same instruction, and each unit fetches data from different streams. Vector processors represent the first architecture of this class, while GPGPUs represent the current design choice in this class.

Multiple Instruction Multiple Data (MIMD) There are multiple, independent processing units. Each one executes instructions fetched from different instruction streams, and fetches data from different data streams. Modern multi-core processors fall into this category: each core is independent, so it is possible to execute completely unrelated instruction flows manipulating independent data streams on each core.

Multiple Instruction Single Data (MISD) There are multiple processing units, executing different instructions on the same data. This class was defined by Flynn for the sake of symmetry, however basically no architecture, save for systolic arrays is classified as MISD.

#### 1.2.2 Single-core architectures

Until to 2005 the majority of general-purpose architectures were SISD. The main target during this period were single-threaded applications,

thus the focus in the computer architectures development was the improvement of the execution time of a sequential application. To this end, the first attempt made was the implementation in hardware of the most recurrent complex operations present in target user applications. The result of such a design trend are architectures known as Complex Instruction Set Computing (CISC) architectures. Common features among them are the support of complex operations and complex addressing modes. However the hardware complexity required to support such operations impacts adversely on the critical path, thus limiting the maximum working frequency.

As a consequence of this mindset, the design criteria of computer architectures were aimed at improving the throughput of completed instructions, measured in terms of *Instructions Per Cycle* (IPC). *Reduced Instruction Set Computing* (RISC) architectures exploit better the pipelining technique. The processing of a single instruction is split into stages. At each clock cycle, the architecture executes all the stages of the pipeline in parallel, thus the clock cycle is determined by the latency of the slowest stage. The latency of an instruction is equivalent to the latency of the pipeline, however the throughput is increased since an instruction is completed at each cycle.

Pipelining exploits the parallelism between instructions in a single execution flow — Instruction Level Parallelism (ILP) — executing them partially in parallel while still exposing a sequential programming model. However, the benefit of pipelining holds if and only if the pipeline is kept full, i.e. at each clock cycle an instruction must be issued. If this is not possible a stall is inserted in the pipeline, leading to a performance loss. This may happen due to hazards induced by the instruction sequence. There are three kind of hazards: control, data, and structural. A control hazard is generated whenever the address of the next instruction is not ready as an input to the fetch stage. A data hazard is generated when data needed by an instruction are not available yet. A structural hazard is triggered when all hardware resources required to execute an instruction are not free.

To reduce the effect of hazards, several techniques were proposed: cache hierarchy, pipeline forwarding, super-scalar pipelines, VLIWs, speculative execution, out-of-order execution [84], branch prediction [91]. In order to increase the clock frequency pipelines have been split in multiple stages (e.g. with the last Intel Pentium 4 being designed with a 31-stages pipeline). However, the intrinsic limitation of the ILP [88] in a single instruction stream acts against advanced and complex techniques when considering the performance gains versus the power and silicon costs. This increased power consumption also prevents further increases

of the clock frequency, as that would also worsen the the dynamic power consumption issue. Indeed advanced techniques to minimize the amount of stalls inserted in the pipeline require complex logic, often contributing more than a clock increase to the overall power consumption. This problem is generally identified with the term *power wall* [18].

Orthogonally, cache hierarchy is used to amortize the cost of accessing data in memory, however feeding the processor with instructions to be executed, and data to be computed at each clock cycle is still an issue. The inability of the memory hierarchy to fulfill the data requests is identified with the term memory wall [89].

#### 1.2.3 Multi-core architectures

Hitting the power wall forced architecture designers to move towards other strategies beyond ILP to improve the overall performance and reduce the power consumption.

To enclose the power consumption, designers removed power-hungry components required by aggressive ILP techniques. Pipelines became shorter, the issue width narrowed, and static scheduling with in-order execution was preferred on low power designs. These design criteria do not necessarily imply that we cannot execute more complex applications. At the same time, such simpler designs fit better the emerging figures of merit, such as the power consumption, and power/energy efficiency. However, some applications still require raw performance. For example HPC applications need faster processors to perform more accurate simulations. Computer-graphics is another field where raw performance is a stringent requirement.

To provide raw performance, techniques beyond pure ILP have been employed. Moore's law is still in effect, increasing each year the number of transistors that can be packed in a given amount of silicon area, thus allowing the implementation of new techniques to improve performance.

Starting from 1995, computer architectures contain explicitly parallel features. Vector instruction set extensions [30, 73] are a good example of this trend. This concept is borrowed from vector processors, the idea is to have instructions operating on fixed length vector types.

The trend of exposing hardware parallel features reached the critical point around 2005. Starting from 2002, Simultaneous Multi Threading (SMT) designs (e.g. Intel Hyper-Threading [61]) have been employed to allow the execution of more than one independent execution flow. Pipeline stalls due to hazards in one execution flow are used to execute another execution flow.

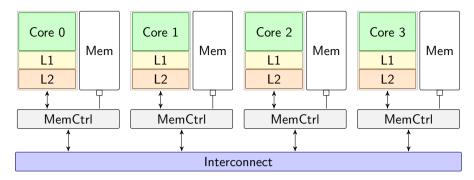

Figure 1.1: Quad-core SMP UMA architecture.

The evolution of this approach is *Symmetric Multi Processing* (SMP) design, were multiple independent processing elements are explicitly exposed. This technique, initially exploited at multiple package level – i.e. installing more than one single-core processor on the same motherboard –, has been widely applied at the single package level – i.e. putting more than one core on the same die – starting from 2005. This new design strategy leads to architectures that can be classified as MIMD in Flynn's taxonomy.

The problem of feeding processors with data is orthogonal to the power problem. However the same techniques can be useful to deal with the memory wall. On SISD architectures there is an unique path for accessing the main memory – all accesses go through the memory controller. The primary measure of its efficiency is the bandwidth, that is the amount of bytes it can transfer from/to the memory per time unit. To increase this amount, the memory controller has been integrated in the same die on which the CPU resides. It works closely with the cache hierarchy, and they are responsible for ensuring memory consistency. Considering that the memory access latency and bandwidth do not evolve like the performance of the core, the memory controller becomes rapidly a bottleneck of the architecture. Moreover, the increasing number of cores per die imposes a further load on the memory controller due to the fact that it has to provide data for all of them.

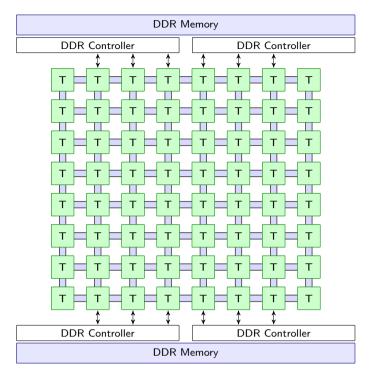

Architectures where the memory access latency is constant among all processors are called *Uniform Memory Access* (UMA). When an access to the main memory is generated, the cores send a request to the memory controller. The communication between cores and memory controller is a shared bus. Figure 1.1 shows the structure of a quad-core UMA architecture.

Figure 1.2: Quad-core SMP NUMA architecture.

This design, however, does not scale well increasing the number of cores. To remove the bottleneck, the number of paths to the main memory must be increased. Each core can have its own memory controller, directly connected to a different memory module. In this scenario, a memory access can be local – i.e. a memory request satisfied by the private memory controller – or remote – i.e. a memory request thus satisfied by the memory controller of another core. This choice makes the access latency dependent on which core performs the memory request and on which memory module contains the data. On the other hand, the overall bandwidth is increased. This kind of architectures are called *Non Uniform Memory Access* (NUMA). A NUMA node is composed by the code, the cache hierarchy, the memory controller, and the local memory module. The communication channel between nodes is generally an *interconnect network*. Figure 1.2 shows the structure of a quad-core NUMA architecture.

UMA designs are used in small multi-core architectures, while NUMA designs are used whenever the number of cores grows beyond the practical scalability limit for the UMA approach. Hybrid designs are generally adopted, e.g. Intel QuickPath Interconnect [46] based multi-core show in Figure 1.3. In these multi-cores we have groups of cores. Each group has one integrated memory controller. Groups of cores are connected via a *point-to-point* interconnect.

The advances of semiconductor technologies, according to Moore's law, allow in principle to pack more cores in the same die area. In practice this is not true for the breakdown of Dennard scaling law – i.e., constant power density reducing the size and voltage of transistors. Shrinking the transistors leads to an increment in the power density, and consequently the temperature of the silicon itself. It becomes an issue to keep the entire silicon die to a proper working temperature, thus not all the transistors can be powered on at the same time. The

**Figure 1.3:** Intel QuickPath Interconnect architecture. In (a) is shown the Nehalem architecture. In (b) the interconnection through point-to-point links of four Nehalem processors.

transistors that cannot be powered at a given time instant are defined as dark silicon [33].

As a consequence of the dark silicon problem, it's not feasible to increase unconditionally the number of cores, as a thermal runaway phenomenon would ensue. Because of this, multi-core designs are moving towards heterogeneous architectures, in order to better employ the available silicon, and create better power efficient multi-cores. The Cell Broadband Engine [42] is one the first heterogeneous multi-core architectures. It is composed by a *Power Processor Element* (PPE) and eight *Synergistic Processing Elements* (SPEs). These are linked toghether by a high speed bus. The SPEs are optimized for single precision floating point computation. The PPE is based on the PowerPC architecture, a two way multithreaded core acting as a controller for the SPEs. Each SPE is composed of a *Synergistic Processing Unit*, and a *Memory Flow Controller* (DMA, MMU, and bus interface). The SPU instruction set is characterized by 128 bit vector floating point instructions. Indeed each SPE contains 256 KiB of SRAM for instruction and data.

The big.LITTLE [8] architecture designed by ARM is another example of heterogeneous multi-core. Unlike the CellBE architecture all the cores implement the same base instruction set. The multi-core is composed by 4 high performance Cortex-A15 cores, and 4 power efficient Cortex-A7 cores.

#### 1.2.4 Many-core architectures

As a consequence of the power wall, processors do not scale anymore towards higher frequencies. The major trend goes to the integration of more cores per chip. Architecture designs considering a large number of cores are generally called *many-cores* architectures. We refer to *heterogeneous many-cores* architectures whenever different kind of cores are involved. These architectures fit well applications where the same computation is performed independently on a huge set of input data. Examples of such application are N-Body simulations, PDE solvers, and high-end computer graphics such as animation rendering.

For such workloads the most important figure of merit is the throughput rather than the latency. To this end, considering the trade-off between number of cores, their complexity, and the total power budget, increasing the number of cores has turned out to be the best choice. To manage the power wall and the dark silicon issues, the trend is to balance the number of cores versus their complexity, and to reduce the clock frequency of the cores.

#### **General Purpose GPUs computing**

The first kind of many-core architecture is represented by *Graphic Processing Unit* (GPU) architectures. Starting off in 1999 with NVIDIA's GeForce 256 [67], graphics rendering started to be offloaded on graphics board. Graphics hardware evolved towards stand-alone processors becoming able to completely replace and outperform general purpose CPUs for complex graphics operations.

GPU architectures focus on performing large numbers of mostly independent operations on vertices, and triangles, composing a scene to be rendered. The affinity with general purpose massive parallel applications leaded to  $General\ Purpose\ GPU$ s, where typically computationally intensive parallel tasks are offloaded to exploit the parallel hardware features. In June 2007 NVIDIA released the first version of CUDA –  $Computed\ Unified\ Device\ Architecture$  – as parallel computing platform working on Tesla micro-architecture.

Modern GPGPU architectures are composed by an array of computational units, i.e. *Stream Multiprocessors* for NVIDIA or *Compute Units* for AMD. These architectures can be classified as SIMD machines in the Flynn's taxonomy.

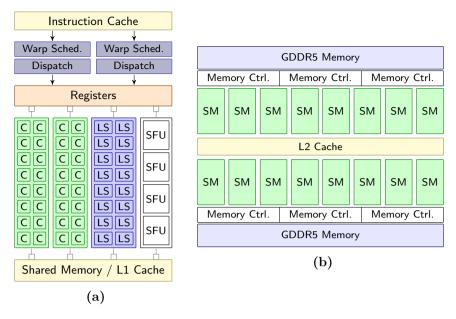

NVIDIA Fermi Stream Multiprocessor is composed by 32 cores – Stream Processors – containing an integer ALU and a floating point unit each, 16 load/store units, 4 special function units, a shared register file of 32k registers, and 64 KiB of shared memory [66]. The execution unit of a Stream Multiprocessor is called warp, that is a group of 32 threads. In a NVIDIA Fermi SM there are 2 warp-schedulers and 2 dispatch units. The dispatch unit sequentially feeds all the 16 cores with

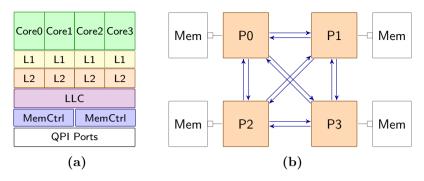

**Figure 1.4:** NVIDIA Fermi architecture. In (a) the architecture of a Fermi SM, while in (b) the global architecture of a Fermi GPGPU.

an instruction for the selected warp as depicted in Figure 1.4. The result is that the 16 cores work in a step locked fashion.

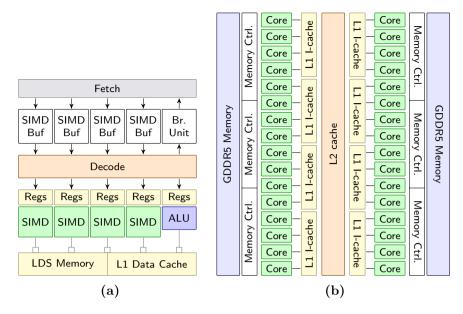

AMD GCN Compute Unit [5] is composed by a 4 independent SIMD units 16 element wide, a scalar unit, a branch and messages unit, and 64 KiB of shared local memory as depicted in Figure 1.5. Each SIMD unit has 64 KiB of registers, while the scalar unit has 8 KiB registers partitioned in 512 entries for each SIMD unit. The execution unit is called wavefront, that is a group of 16 threads – i.e. one for each SIMD lane. Each SIMD unit can hold up to 10 wavefronts. The scalar unit is used to support control flow instructions, including jumps, calls, and returns. Indeed, predication for vector instructions is managed by the scalar unit.

#### Standalone many-core architectures

Apart from GPGPUs, that were designed to accelerate specifically graphic tasks, and subsequently have been adapted to support also general purpose computation, proper many-core architectures designed for computing have been proposed starting from 2007.

**Figure 1.5:** AMD GCN architecture. In (a) the architecture of a single GCN core, while in (b) the global architecture of a AMD GCN graphic processor.

**Tilera TILE64** released in 2007, it consists of a mesh network of 64 tiles [14]. Each tile is composed by a general purpose core, L1 and L2 caches, and a non blocking router used for communication with other tiles. Figure 1.6 shows the tiled architecture of TILE64. Each core is a 3-way VLIW architecture, with two integer ALUs and a load/store unit. The running frequency of the system is ranging from 600 MHz to 900 MHz.

Intel 80-core Teraflops Research Processor presented in 2007, is a tiled architecture [86] similarly to TILE64. Each tile is composed by two single precision FPMAC units, 3 KiB of instruction memory, and a 5 port router for 2D mesh and 3D stacking. The project investigated inter-core communication methods, per-chip power management, and achieved 1.01 TFLOPS at 3.16 GHz consuming 62 W of power. This chip has never been a product, but from this research in 2009 Intel presented the Single-Chip Cloud computer [43]. This processor contains 48 P54C Pentium cores connected with a 2D mesh. Each tile contains 2 cores, and a router.

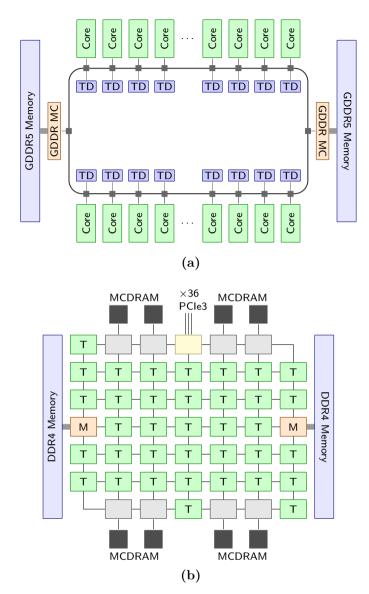

Intel Xeon Phi is the brand name of Intel Many Integrated Core [31] architectures. In 2010 Intel presented the first prototype – codename Knights Ferry. The first commercial version of the MIC architecture –

Figure 1.6: TILE64 architecture

codename  $Knights\ Corner\ (KNC)$  – was released in 2011, and started being employed in HPC systems. The KNC is composed by 60 small in-order execution x86 cores. Each core has 64 KiB L1 cache, 512 KiB L2 cache, and a 512 bit wide vector unit. As shown in Figure 1.7a, the cores are connected through a 512 bit bi-directional ring bus. L2 caches are kept fully coherent by a global distributed tag directory. The peak performance of KNC is  $\sim 1\ TFLOPS$  double precision consuming 300 W. In 2013 Intel presented the second generation of Xeon Phi – codename  $Knights\ Landing\ (KNL)$ . The KNL is composed by up to 72 cores, structured in 36 tiles, connected through a 2D mesh interconnect rather than the previous ring bus, as shown in Figure 1.7b. The cores are based on the Silvermont architecture: 4 threaded, out-of-order execution, two 512 bit vector units, supporting almost the entirety of the common Xeon ISA. The peak performance of KNL is  $\sim 3\ TFLOPS$  double precision consuming 300 W.

#### Power-efficient many-core architectures

GPGPU architectures have been employed in HPC systems since their beginning. Their massive peak performance come at a cost of a con-

**Figure 1.7:** Xeon Phi architectures. In (a) the *Knights Corner* architecture, while in (b) the *Knights Landing* architecture.

siderable power consumption (150 W to 200 W for a single GPGPU). As reported in Section 1.1, the current HPC road-maps aim to reach exascale levels ( $10^{18}$ FLOPS) within 2020, which poses the challenge of limiting significantly the overall power budget while providing a massive increases in computational capabilities. In particular the target power budget for future exascale systems ranges between 20 MW and 30 MW.

#### 1 Parallel Computing

The best system of The Green500 list of November 2014 reach a power efficiency of 5271 MFLOPS/W which is still one order of magnitude lower than the efficiency needed for supporting exascale systems within 20 MW.

Because of this designers are looking for alternative, more power efficient solution to many-core architectures. Nowadays are becoming more interesting designs from embedded architectures where the power efficiency is a primary goal from long time, while the performance requirements is constantly increasing.

Three interesting architectures are Kalray MPPA-256 [28], STMicroelectronics STHorm [16], and PULP [23].

Kalray MPPA-256 released at the end of 2012, is a clustered architecture of 16 clusters of cores interconnected through an explicitly addressed Network-on-Chip (NoC). The NoC is a 2D-wrapped-around torus structure providing a bandwidth up to 3.2 GiB/s between adjacent clusters. Indeed a quality of service mechanism is used to guarantee predictable latencies for all data transfers. Each cluster is composed by 16 cores as processing elements, one system core, 2 MiB of shared memory, a DMA unit, L1 instruction and data cache, and the NoC interface. Each core is a 5-issue VLIW architecture with one branch unit, two ALUs, one load-store unit with a reduced ALU, double precision FPU with FMA, and private MMU. The architecture provides a power efficiency of 23 GFLOPS/W at 400 MHz consuming typically 10 W.

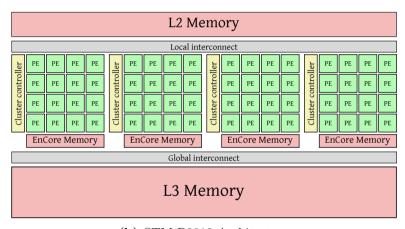

STMicroelectronics STHorm - also known as P2012 - is an heterogeneous many-core architecture where the host processor is a dual core ARM A9 paired with a fabric used as accelerator. The fabric is a clustered architecture composed by 4 clusters connected through a global asynchronous NoC. Each cluster is composed by 16 cores as processing elements, one core as cluster controller, 256 KiB of L1 shared memory, and dual channel DMA unit. Each core is an STxP70, an extendible core designed by STMicroelectronics. On P2012 each core is extended with a floating point unit. The core is a 2-issue VLIW with DSP oriented ISA. Barrier operations intra-cluster are implemented in hardware. Indeed, there is one extra core – i.e. fabric controller – used as coordinator for all the clusters on the fabric. At fabric level there is also 1 MiB of L2 shared memory across all the clusters. Indeed within cluster dedicated IPs can replace the general purpose core to accelerate specific functions. The cores within a cluster are connected to the shared memory through a logarithmic interconnect. The fabric can access to a portion of the

main memory of the host processor. DMA units are useful to implement asynchronous data transfer between memories. The fabric with 4 clusters provides a peak performance of 80 GFLOPS (single precision) consuming 500 mW per cluster at a frequency of 600 MHz.

**PULP Platform** – the Parallel Ultra-Low Power Platform – is a on going project developed by ETH Zurich and Università di Bologna under the lead of Prof. Luca Benini, the chief architect of P2012. The design of such platform is inspired by the results of P2012. However the target of this platform are ultra-low power embedded systems. Each core is an OpenRISC architecture based on the opensource OR1200 microarchitecture. The idea was to replace the proprietary STxP70 cores with smaller but more power efficient ones. To this end, the microarchitecture has been optimized, and the ISA has been extended to add DSP-like features to improve the performances (more details in Section 2.3). The fabric is composed by a single cluster of 4 cores. Within the cluster there are also 48 KiB of TCDM, 256 KiB of L2 memory, and a dedicated DMA unit. All the cores within a cluster are attached to a 4 KiB shared instruction cache. PULP version 3 has been implemented using ST28 FDSOI technology with RVT transistors. The maximum frequency is 66 MHz with a power supply voltage of 0.6 V. In such condition the consumed power is roughly 1.59 mW. Another implementation using UMC65 technology reaches the maximum frequency of 362 MHz and is capable of processing 1.4 GOPS at a power budget of 93 mW.

#### 1.2.5 Future perspective

It is clear the hardware evolution trends is converging towards many-core heterogeneous architectures. The limits in scaling with huge and complex cores, and the increasing emphasis on the power consumption moved the interests of architectures designers in architectures with a considerable amount of cores with different features and complexity. Many-core architectures started with GPU designs, where a great number of simple cores is employed to execute a single instruction flow on multiple independent data. However the interest in irregular parallel problems has shown limitations of such architectures. This is leading towards hybrid architectures, i.e. a mix of multi-cores and many-cores, where the complexity of each core is increased to better fit irregular control-flows and non predictable data access patterns. Indeed the current trend is moving towards integrating such cores in the same die area to reduce the cost of communication between heterogeneous cores. An example of such trend is the introduction of shared virtual memory between CPU

and GPUs, e.g., the HSA Foundation [44] requires all the agents to share the same virtual address space. Once the decision of integrating general purpose CPUs and GPU cores on the same die, it is feasible, and much desirable, to interface them with the same main memory. Indeed to simplify the programmability and to remove the overheads due to useless memory transfers, it is interesting to make CPUs and GPUs share the same virtual address space similarly to what already happens within modern multi-cores. This is currently a challenge considering the goal to have transparent coherency between cache hierarchies of both CPUs and GPUs. The OpenCL 2.0 programming model exposes this feature to the programmer in two forms: coarse-grain SVM and fine-grain SVM. The former is the minimum requirement where at least explicitly allocated buffers can be shared between CPUs and GPUs, and are kept coherent at given synchronization points. The latter is optional as it requires that the whole address space to be shared, and must be coherent also on atomic operations. Modern GPU architectures implement only the coarse-grained model of SVM, as it can be implemented without the need for support for lazy page loading, i.e. no page-fault exceptions, and without the support for cache coherency protocols, because the coherency must be ensured only at given synchronization points, thus this can be enforced by the software runtime. The fine-grain SVM model requires much more hardware support still not available. However the fact that such features have been introduced in programming models suggests that in the near future the hardware will move towards providing them.

#### 1.3 Parallel programming models

Exposing the control of parallel hardware features to the programmers allows architecture designers to increase the overall architecture performance. However this makes the task of programming these architectures much more complex.

To take advantage of parallel processing elements there are two possible approaches: *implicit* and *explicit* techniques.

Implicit techniques aim to hide as much as possible the details of the target architecture from the programmer perspective. The actual exploitation of parallelism is achieved transparently at run-time or compiletime. For example ILP exposes to the programmer a sequential programming model, while the actual execution may be performed in parallel. In an out-of-order architecture ILP acts at runtime dynamically identifying independent instructions, and executing them in parallel using

different functional units. At the other end of the architecture design spectrum, in a VLIW architecture the compiler is in charge of scheduling instructions to exploits the different functional units available.

Explicit techniques, instead, expose the hardware parallelism to the programmers. This allows developers to have a greater control on the mapping of the application on the hardware. On the other hand, it becomes the programmer's responsibility to identify and map the parts of the application which can be efficiently parallelized. To this end explicit parallel programming models are needed.

A programming model is the description of an abstract architecture used as reference architecture to describe how computation is performed. The concepts of a programming model are strongly connected with the class of hardware architectures it targets. Parallel programming models are built around the concept of multiple execution flows. The ways multiple execution flows may interact with each other are determined by the programming model rules, and generally depend on the hardware features available.

How a given computation on a data set is mapped on multiple execution flows determines the nature of the parallelism: the two base approaches are named *data* and *task* parallelism.

**Data parallelism** partitions the input data set mapping the processing of each chunk to an execution flow. All the execution flows are fed by the same instruction stream but compute on different data streams. This computational model fits SIMD class of Flynn's taxonomy.

It fits also extensions of this class, like Single Instruction Multiple Thread (SIMT) – the same instruction is executed by different cores in a step-locked fashion – and Single Program Multiple Data – the same program is executed by different cores on different data but the threads are independent. It is often said that an application suitable for a data-parallel programming model exhibits a regular behaviour: not control intensive, with a large number of operations often on large arrays accessed with fixed strides.

**Task parallelism** partitions the computation in independent tasks mapping each one to a different execution flow. The *task* is the unit of parallelism. A parallel computation is originated by the creation of new tasks. The act of creating a new task is called *spawning*. Spawning a task represents the intent of execute the task in parallel with the current execution flow. Synchronization between tasks is usually achieved by *joining*: a task can wait for the termination of another task before

moving on with its execution. The relationships between tasks can be represented by means of a *task-graph*. Each node in the graph is a spawned task. Arcs between nodes can be either spawning actions or joining actions. This computational model fits MIMD class of Flynn's taxonomy and its extensions such as the *Multiple Program Multiple Data* (MPMD). This model is said to be suitable for applications with an *irregular behaviour*: they are generally control-intensive, accessing data in a non predictable way.

In the following, a brief overview of the most adopted parallel programming models suitable for programming of multi-core and many-core architectures, and a comparative analysis of the interesting features of such programming models is provided. This analysis aims to highlight modern trends of parallel programming models illustrating the different approaches to express the parallelism exploiting the available hardware features.

#### 1.3.1 Overview

Several programming models and frameworks have been proposed in the literature for programming parallel and heterogeneous architectures. The interest in this chapter is towards the most adopted programming models for multi-cores and many-cores architectures. Programming models for distributed systems, such as MPI and PGAS models, are not discussed as they lie beyond the scope this overview. The selected programming models are OpenCL [50], CUDA [65], OpenMP [6], OpenACC [70], Codeplay Offload [24], C++AMP [64], SYCL [53], Cilk [36], Intel TBB [25], StarSs [15, 19], SkePU [32, 10], and some DSLs.

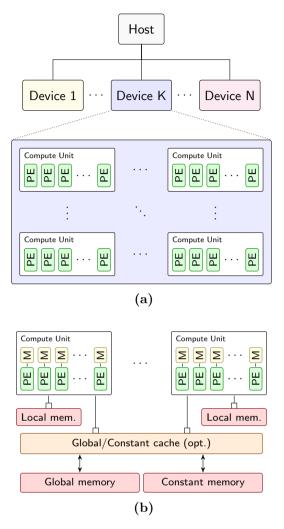

**OpenCL** is a framework for programming parallel heterogeneous platforms. The architecture of the OpenCL platform, shown in Figure 1.8a, is composed by an *host* connected to one or more *devices*. Each device is composed by one or more *compute units*. Each compute unit is composed by one or more *processing elements*.

An OpenCL application is generally split into two parts: the *host* program, and the kernels for the devices. The kernels represent the computation executed on the devices. The host program defines the context for the kernels and manages their execution.

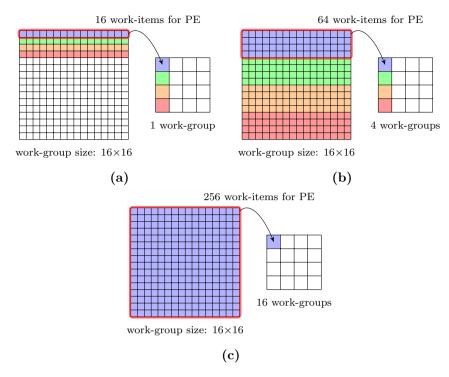

The OpenCL execution model describes how kernels are executed. When a kernel is submitted to a device for execution by the host, an index space is defined. An instance of the kernel executes for each point in the index space. This kernel instance is called *work-item* and it is

Figure 1.8: The OpenCL platform. In (a) the relationship between host and devices, and the structure of a device, while in (b) the memory hierarchy within a generic device.

identified by its position in the index space. Work-items are organized in work-groups. The work-groups are the result of a tiling process onto the index space. The work-items in a given work-group execute concurrently on the processing elements of a single compute unit. A barrier operation is indeed defined between the work-items in a given work-group.

There are four distinct memory regions in OpenCL, illustrated in Figure 1.8b. The *global* memory can be accessed by all the work-items in all the work-groups. The *constant* memory is specialization of global memory for constant data. Both constant and global memory can be

accessed by the compute units through a cache hierarchy. Each compute unit has a dedicated *local* memory, that is a shared memory space between work-items in a given work-group. The *private* memory is used for private variable of each work-item.

The OpenCL execution model is suitable for both data-parallel and task-parallel approaches. However the execution model fits better data-parallelism .

The host-program and the OpenCL kernels are expressed in different languages. The OpenCL runtime has a standardized set of C APIs. The runtime offers full control on the management of memory buffers allocation, and the execution of kernels across the devices. OpenCL kernels are described through the OpenCL-C programming language. This language is a restriction of C99 language (e.g. no recursion, no variable length array) plus some extensions to support vector types and builtin functions.

OpenCL claims functional portability of an application, as the programming language for the kernels is target independent. However it is still possible to write code for specific targets relying on implicit knowledge of the underlying architecture. This freedom is useful to extract more performance from the underlying parallel hardware, however it limits the portability of the code itself.

OpenCL 2.0 introduced some new features, such as the support to shared virtual memory between host and devices, the generic address space, and the support for dynamic parallelism, i.e. the possibility of "spawning" new kernels on a device with no needs for host interaction.

**CUDA** is the programming framework of NVIDIA for its GPUs. Almost all the key concepts are the same as in OpenCL. In the CUDA parlance work-items are called *threads*, and work-groups are called *blocks*. The memory model is equivalent to the OpenCL 2.0 one.

The main differences resides in the interface to the programmer. In particular, CUDA allows to specify the host program and kernels in a single translation unit. The CUDA programming language is an extension to C/C++ with attributes for tagging functions that must be compiled only for the device, for tagging variables with the appropriate address space modifier. Indeed a new syntax to invoke kernels from the host part of the program is provided.

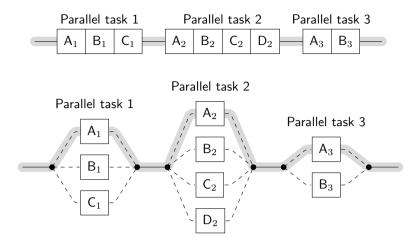

**OpenMP** is a programming framework for multi-cores. It consists of a set of compiler directives, library routines, and environment variables. It is available for C, C++, and Fortran. OpenMP follows the *fork-join*

**Figure 1.9:** Fork-join model. The execution path of the master thread is highlighted in grey. On the top of the picture the sequential execution flow, where only the master thread is active. On the bottom of the picture the parallel execution flow, where the master thread forks to generate worker threads to execute the tasks in parallel, and joins them to synchronize.

model, show in Figure 1.9. The program starts with a single thread called *master-thread*. At the beginning of a parallel region, the master threads creates – *forks* – a team of parallel worker threads. An instance of the parallel region body is executed by all threads. At the end of the parallel region all the threads synchronize, and *join* the master thread.

Using OpenMP both task-parallelism and data-parallelism strategies can be implemented. The compiler directives are used to describe parallel sections and whether some variables are shared or private. These directives are platform independent, allowing an high degree of portability. Furthermore, it enables incremental parallelism as ideally only additional compiler directive should be added to enable parallel execution of a piece of code. However synchronization bugs and race conditions may occur. Starting with OpenMP 4.0 it is possible to offload parallel regions to accelerators such as GPGPUs.

**OpenACC** is a programming framework for parallel computing that targets CPU-GPGPUs heterogeneous architectures. Similarly to OpenMP it is based on compiler directives to describe parallel regions, and manage data movement from/to the GPU memory. Like OpenMP, it supports C, C++, and Fortran programming languages. It is common for an OpenACC compiler to emit OpenCL/CUDA code (or equivalent intermediate representations such as SPIR) for the kernels, and rely on

vendor specific OpenCL/CUDA drivers to offload the computation on the GPUs.

**Codeplay Offload** is programming model for both homogeneous and heterogeneous multi-core processors such as the Cell Broadband Engine. It allows to offload portions of large C++ applications to be run on accelerator cores. The code that must be offloaded is wrapped in a *offload* block, indicating that the code should be compiled for an accelerator, and executed asynchronously as a separate thread. The main point is to ensure the portability across heterogeneous and homogeneous platforms, and relieve the programmer from the burden of writing data movement and accelerator setup code.

C++ AMP is programming framework that extends C++ to support data-parallel computation on parallel accelerators like GPUs. The initial implementation by Microsoft was targeting DirectX 11 drivers. It has been extended to target both OpenCL and HSA compliant platforms. C++ AMP is based on the C++11 language and introduces function modifiers to specify the fact a function should be compiled for the device or not. The codebase of kernels is expressed using lambda functions as arguments to the parallel\_for\_each template function. The data access by kernel code can only be done throughout the array and array\_view wrappers. These wrapper are used as proxy for data that must be transferred on the accelerator. Although the base language is C++, the code constructs which can be employed within a kernel are constrained to match the requirements for offloading the computation using existing OpenCL drivers.

**SYCL** is a programming framework built on top OpenCL. It allows to specify a parallel program exploiting OpenCL devices in a single C++ source. Kernels are expressed similarly to C++AMP through a lambda function as a parameter to the parallel\_for template function. This function takes as input the work-item identifier, and access global and local data through accessor objects captured by value. The accessors acts like a proxy for data that must be transferred on the accelerator. The SYCL compiler identifies kernels, generates OpenCL code (or equivalent intermediate representations like SPIR). The SYCL runtime is responsible for wrapping the OpenCL driver in order to offload kernels on the accelerator. The SYCL compiler is responsible for auto-deducing address spaces of variables in the most common cases, however the explicit pointer classes can be used to indicate the belonging of a given memory

region to a specific address space. A SYCL program is valid C++ program that can be compiled by any C++ compliant compiler, and can be executed on the host as fallback for platforms with no OpenCL support.

**Cilk/Cilk++** are general purpose programming language designed for multi-threaded parallel computing. They are based on C and C++ languages, and they extend these with constructs to express parallel loops and spawn/join tasks. Indeed they simplify the syntax for array operations to help the compiler to effectively vectorize the operations. The task scheduler in Cilk uses the *work-stealing* policy to balance the workload across the cores.

**Intel TBB** is a C++ template library intended to support task parallelism on multi-core processors. Tasks are scheduled using the work stealing policy like in Cilk. It is composed by generic algorithms (such as parallel\_for, parallel\_reduce), concurrent containers, scalable memory allocators, mutual exclusion primitives, and a task scheduler.

**StarSs** is a programming framework developed at Barcelona Supercomputing Center. It is directive based like OpenMP and OpenACC, it targets multi-core and heterogeneous accelerators. The directives are used to express data dependencies between tasks. These are organized in a task-graph according to their data dependencies. Task with no predecessors represent ready tasks. The runtime moves them from the task-graph to the ready queues of worker threads. Data dependencies refer to memory locations, expressed as base address and size. An input dependency represents a location that is read by the task. An output dependency represents a location read and written by the task.

**SkePU** is C++ template library of "skeletons". A skeleton is a predefined, generic component such as map, reduce, scan, farm, pipeline, etc. that implements a common specific pattern of computation and its data dependencies. Skeletons provide an high degree of abstraction and portability, as their implementations encapsulate all low-level and platform specific details, such as parallelization, synchronization, and communication. It supports multi-cores and multi-GPUs systems both with OpenCL and CUDA. It implements an auto-tuning framework for a context-aware dynamic selection of the expected fastest implementation variant of each skeleton. Indeed it ca be integrated with the StarPU runtime system. StarPU is a task programming library for heterogeneous

architectures, it manages automatically all the data transfers between devices.

Domain specific languages are employed to simplify the specification of algorithms and programs relative of a given application domain. They generally are high-level languages that completely hide the detail of the target architectures. Such approaches to parallel programming can be very effective for those domains where applications have intrinsic parallelism. Some examples are the fields of *image processing*, *computer graphics*, *streaming applications*, *linear algebra*, and *graph analysis*. The use of high-level languages gives the programmers the ability to express the target application in a natural way for the given domain. The compilers for DSLs can exploit the properties derived by the application domain to generate more efficient code for multi-cores and accelerators.

StreamIt [83] is an example of DSL for streaming applications. A StreamIt application is the composition of filters. These can be connected in cascade to generate a pipeline, or through special nodes, splitter and joiner, for splitting/joining the data stream on several parallel filters.

GLSL – OpenGL Shader Language – is a domain specific language for computer graphics [72]. This language allows the specification of graphics shaders to be executed by GPUs.

Writing a DSL with the relative compiler is not a trivial task. There exist frameworks that simplify the implementation of a DSL compiler, like *Delite* [82] and *Pencil* [12]. These frameworks provide a platform-neutral intermediate representation for DSLs.

# 1.3.2 Comparison

The aforementioned programming frameworks cover most of the approaches to write program for parallel architectures. Interesting dimensions of analysis are the following:

• Abstraction Level, the degree of detail exposed to the programmer to expressthe parallelism. This aspect is important in terms of programmability because more details explicitly under control of the programmer, on one side they imply the possibility of fine-tuning the mapping onto specific target architectures, while on the other side limit the portability the application as the parameters value are inherently target specific. An high abstraction level ensures a high degree of portability as all the details of the architecture are hidden from the programmer.

- Parallelism flavor, the ability to express data or task parallelism.

While data-parallelism has been the first kind of investigated parallelism, task-parallelism is becoming much more interesting as also irregular applications are moving towards heterogeneous architectures.

- *Heterogeneity*, the ability to target heterogeneous parallel architecture, thus suitable for modern many-cores.

- Extended Language, whether the parallelism is expressed by means of extensions to the base language. Solutions employing language extensions are less portable as an extended compiler is needed, while a pure library based approach is immune to this issue. On the other side the use of an extended compiler gives more opportunities to accurately optimize the generated code.

- Elision property, this feature implies the fact that if the features introduced by a language extension are ignored, the resulting program is a correct sequential version of the parallel program. This property is useful for testing purposes and to ensure compatibility of the source code with platforms where such extensions are not available.

- Data management kind, whether data moves are under the explicit control of the programmer or are implicitly managed by the compiler/runtime system. This an important part related to the abstraction level.

Table 1.1 shows the classification of the analyzed programming frameworks. Almost all the frameworks support both data and task parallelism, even if few of them, e.g. OpenCL, are biased towards data parallelism. Most of them support heterogeneous architectures confirming the trend towards heterogeneous parallel architectures.

OpenCL, CUDA, and with a lower degree SYCL and C++AMP are classified as low/mid-low level of abstraction programming framework because the programmer is either required or allowed to specify how to map a data-parallel computation onto a given device. In particular for OpenCL and CUDA, the programmer is also responsible for data transfers between host and accelerators increasing the boiler-plate code required and the complexity of programming for such parallel accelerators.

Frameworks based on compiler directives such as OpenMP, OpenACC, StarSs offer a high degree of portability, as their directives should be

Table 1.1: Comparison of parallel programming frameworks

|                  |                                                                 | ۰                             |                 | c                       |                     |                                                                                   |

|------------------|-----------------------------------------------------------------|-------------------------------|-----------------|-------------------------|---------------------|-----------------------------------------------------------------------------------|

|                  | $\begin{array}{c} {\rm Abstraction} \\ {\rm Level} \end{array}$ | $\mathrm{Data}/\mathrm{Task}$ | Heterogeneity   | Extended<br>Language    | Elision<br>property | Data moves                                                                        |

| OpenCL           | low                                                             | both <sup>1</sup>             | yes             | yes                     | no                  | explicit                                                                          |

| CUDA             | low                                                             | $both^2$                      | yes             | yes                     | no                  | explicit                                                                          |

| ${\bf OpenMP}$   | mid                                                             | both                          | $\mathrm{no}^3$ | pragmas                 | yes                 | implicit                                                                          |

| OpenACC          | $\operatorname{mid}$                                            | data                          | yes             | pragmas                 | yes                 | implicit + hints                                                                  |

| Codeplay Offload | mid                                                             | task                          | yes             | yes                     | no                  | implicit                                                                          |

| C++AMP           | mid-low                                                         | data                          | yes             | yes                     | no                  | implicit                                                                          |

| $\mathbf{SYCL}$  | $\operatorname{mid-low}$                                        | both                          | yes             | no                      | n.a.                | implicit                                                                          |

| Cilk/Cilk++      | $\operatorname{mid-high}$                                       | both                          | no              | yes                     | yes                 | implicit                                                                          |

| Intel TBB        | mid-high                                                        | both                          | no              | no                      | n.a.                | implicit                                                                          |

| ${f StarSs}$     | mid-high                                                        | task                          | yes             | pragmas                 | yes                 | $\begin{array}{c} \mathrm{implicit} + \mathrm{data} \\ \mathrm{deps} \end{array}$ |

| SkePU            | mid-high                                                        | both                          | yes             | no                      | n.a.                | implicit                                                                          |

| $\mathbf{DSLs}$  | high                                                            | both                          | yes             | $\operatorname{custom}$ | n.a.                | generally implicit                                                                |

<sup>&</sup>lt;sup>1</sup> OpenCL support both data and task parallelism, however data parallel is the preferred model.

<sup>&</sup>lt;sup>2</sup> CUDA initially supported only data parallel model. Task parallelism has been introduced with CUDA 5.0

$<sup>^3</sup>$  OpenMP historically targets homogeneous multi-cores. Offload to accelerators has been introduced in OpenMP 4.0.

target-independent. This is a lightweight approach to integrate parallelism annotations within pragmas or comments. However directives for offloading the computation to parallel accelerators may present parameters that depend on the specific knowledge of target architecture, limiting the portability of such approach.

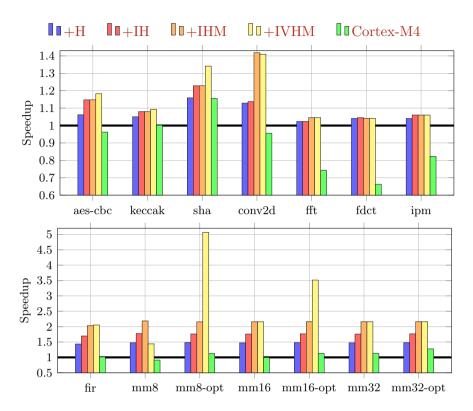

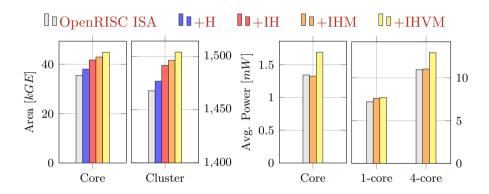

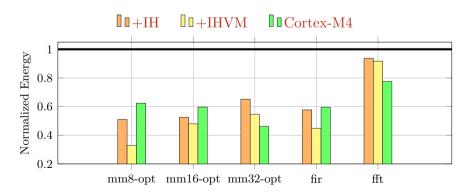

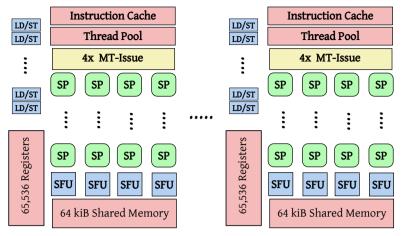

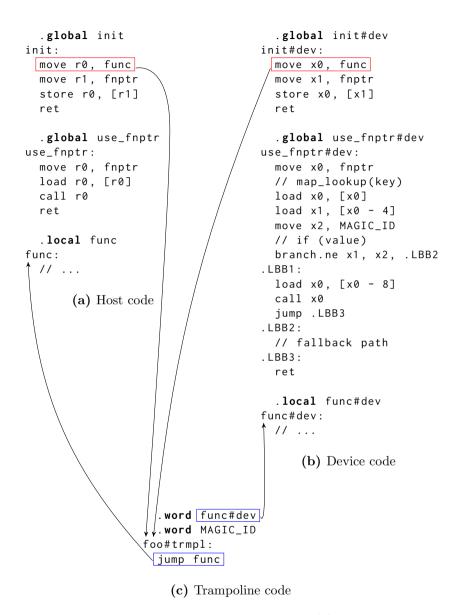

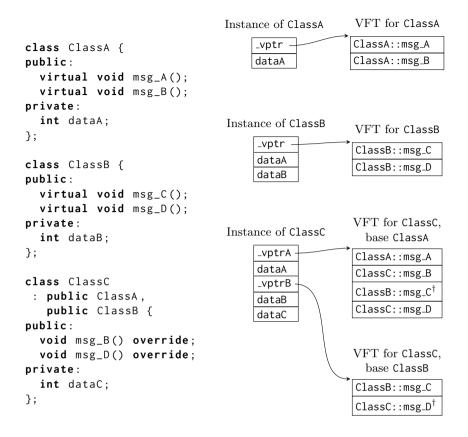

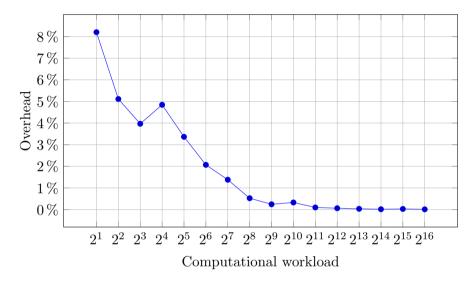

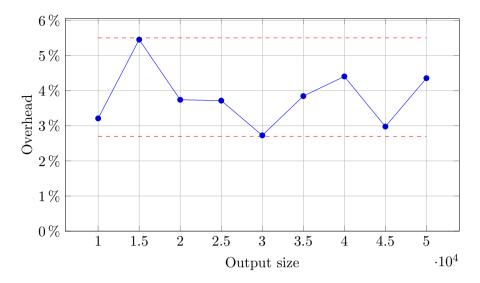

A more intrusive way to express parallelism is to extend existing programming languages such as C, C++, or Fortran to support parallel constructs. This allows for a better integration of such constructs while keeping the quantity of new notions to learn for the programmer at minimum. The compiler for such languages is in charge of lowering such constructs in the best possible manner, on a runtime layer that exploits parallel hardware features. When dealing with language extensions a desirable property is *elision*. Cilk/Cilk++ ensure this property, while C++AMP does not. Directive based extensions such as OpenMP, OpenACC, and StarSs ensure the elision of the directives that are added on the sequential version of the program.