## POLITECNICO DI MILANO Corso di Laurea Magistrale in Ingegneria Informatica Dipartimento di Elettronica e Informazione

## **Control Based Tickless Scheduling**

Relatore: William Fornaciari Correlatore: Federico Terraneo

> Tesi di Laurea di: Ahmad Golchin, matricola 832923

Anno Accademico 2016-2017

## Contents

| 1        | Intr | oducti  | ion                                                                                                | 11 |

|----------|------|---------|----------------------------------------------------------------------------------------------------|----|

|          | 1.1  | Brief l | literature review                                                                                  | 13 |

|          | 1.2  | Contri  | ibutions $\ldots$ | 15 |

|          | 1.3  | Thesis  | s organization                                                                                     | 18 |

| <b>2</b> | Ticl | kless k | ernel                                                                                              | 19 |

|          | 2.1  | Time    | subsystem in Miosix                                                                                | 20 |

|          | 2.2  | Transf  | formation of Miosix into a tickless kernel                                                         | 24 |

|          |      | 2.2.1   | Context Switch Timer interface $\ldots \ldots \ldots \ldots \ldots$                                | 25 |

|          |      | 2.2.2   | Implementation                                                                                     | 26 |

| 3        | The  | e contr | ol based tickless scheduler                                                                        | 32 |

|          | 3.1  | Sched   | uling as a control problem                                                                         | 32 |

|          |      | 3.1.1   | The I+PI scheduler                                                                                 | 35 |

|          |      | 3.1.2   | Motivations for a new control scheduler                                                            | 39 |

|          | 3.2  | The N   | Iultiburst scheduler                                                                               | 42 |

|          |      | 3.2.1   | Design $\ldots$   | 42 |

|          |      | 3.2.2   | Scheduling in Miosix                                                                               | 49 |

|          |      | 3.2.3   | Implementation and integration into Miosix                                                         | 50 |

| 4        | Eva  | luation | n and Benchmarking                                                                                 | 60 |

|          | 4.1  | Simula  | ation results                                                                                      | 61 |

|          | 4.2  | Hartst  | tone benchmark                                                                                     | 62 |

|          |      | 4.2.1   | Benchmark one - asymmetric pool                                                                    | 64 |

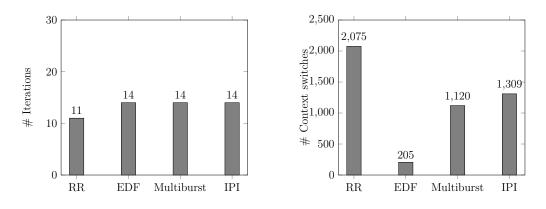

|              | 4.2.2  | Benchmark two - balanced workloads                         | 65              |

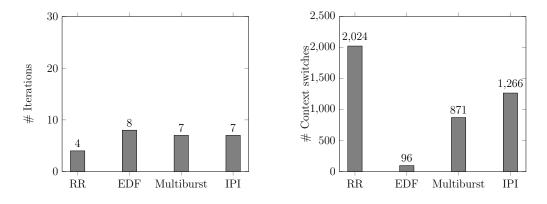

|--------------|--------|------------------------------------------------------------|-----------------|

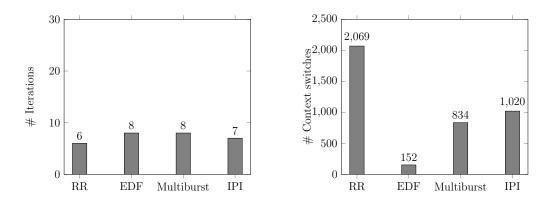

|              | 4.2.3  | Benchmark three - unbalanced workload growth $\ . \ . \ .$ | 65              |

|              | 4.2.4  | Benchmark four - task pool growth                          | 66              |

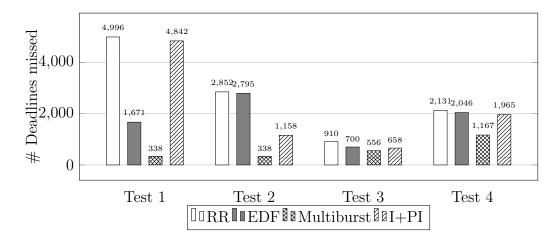

| 4.3          | Exten  | ded Hartstone benchmark                                    | 67              |

| 5 Con<br>5.1 |        | o <b>ns</b><br>e works                                     | <b>70</b><br>71 |

| Biblio       | graphy | 7                                                          | 72              |

## List of Figures

| 1.1  | Miosix kernel architecture                                                                                  | 16 |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Miosix - Kernel tick call graph                                                                             | 23 |

| 2.2  | Miosix - Sleep primitive call graph                                                                         | 24 |

| 2.3  | Context Switch Timer interface                                                                              | 25 |

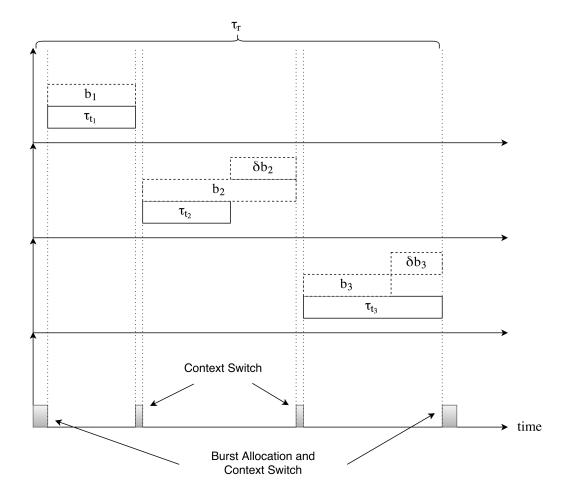

| 3.1  | Task pool model and behavior                                                                                | 34 |

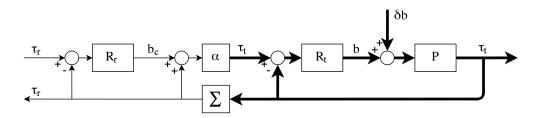

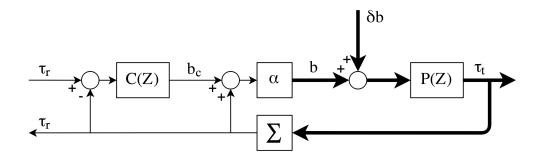

| 3.2  | Control block diagram of I+PI scheduler $\ldots \ldots \ldots \ldots$                                       | 35 |

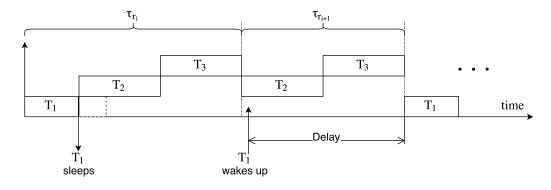

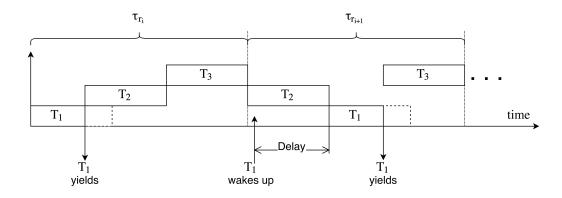

| 3.3  | Reponsiveness problem of I+PI with tasks that give the CPU                                                  |    |

|      | up early $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                   | 40 |

| 3.4  | Expected behavior of the Multiburst scheduler in the case of                                                |    |

|      | I+PI's problem $\ldots \ldots \ldots$ | 42 |

| 3.5  | Control block diagram of PI-Multiburst scheduler $\ . \ . \ . \ .$                                          | 42 |

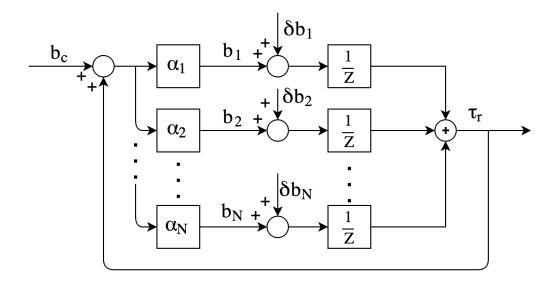

| 3.6  | Expanded model of the task pool together with disturbances                                                  |    |

|      | and CPU shares                                                                                              | 43 |

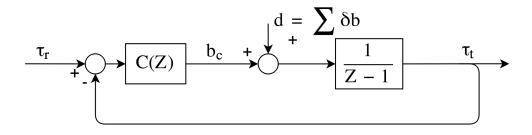

| 3.7  | Simplifed model for tuning Multiburst scheduler's regulator                                                 | 44 |

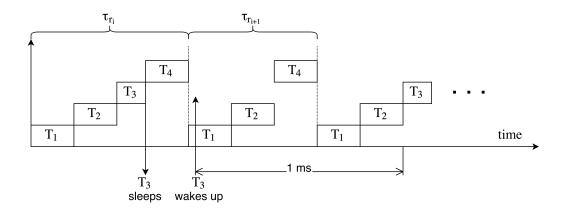

| 3.8  | Problematic example - I+PI scheduling                                                                       | 48 |

| 3.9  | Problematic example - Multiburst scheduling                                                                 | 48 |

| 3.10 | The scheduler interface in Miosix $\ldots \ldots \ldots \ldots \ldots \ldots$                               | 50 |

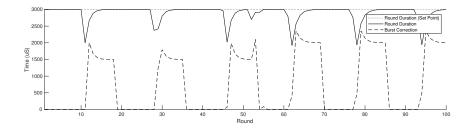

| 4.1  | Simulation - Round duration and burst correction                                                            | 61 |

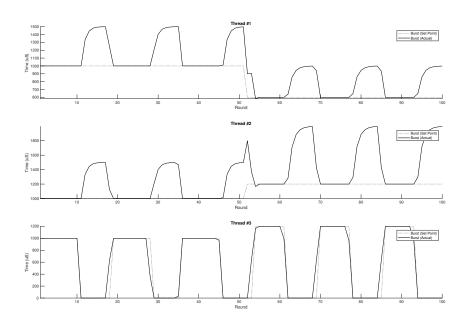

| 4.2  | Simulation - Tasks' actual and desired bursts                                                               | 62 |

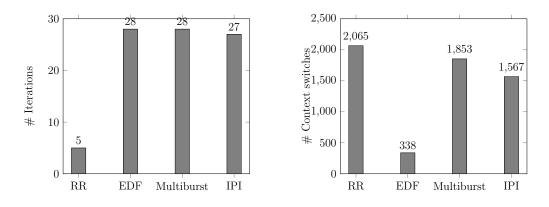

| 4.3  | Hartstone Benchmark - Test 1                                                                                | 64 |

| 4.4  | Hartstone Benchmark - Test 2                                                                                | 65 |

| 4.5  | Hartstone Benchmark - Test 3                                                                                | 66 |

|      |                                                                                                             |    |

| 4.6 | Hartstone Benchmark - Test $4\ .\ .\ .$ . | • | • |  | • | • |  | • | • | • | 67 |

|-----|-------------------------------------------|---|---|--|---|---|--|---|---|---|----|

| 4.7 | Extended Hartstone - Deadline miss        |   | • |  |   |   |  |   |   |   | 68 |

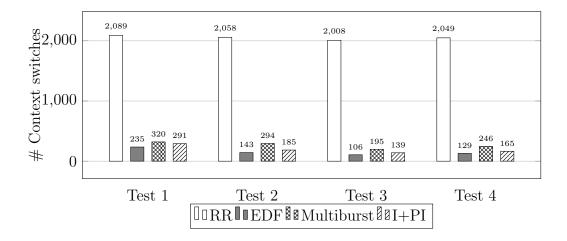

| 4.8 | Extended Hartstone - Context switches     |   | • |  |   |   |  |   |   |   | 69 |

## List of Tables

| 2.1 | Architectures for which tickless Miosix has been ported into . | 26 |

|-----|----------------------------------------------------------------|----|

| 3.1 | Worst case delay after wake-up for Multiburst policies         | 47 |

| 4.1 | The Hartstone [28] baseline task pool                          | 63 |

## Abstract

The use of theoretical methodologies in systems design is highly endorsed in many fields of engineering due to simplicity, flexibility, and uniformity of the solutions as well as the possibility to assess the results even in unpredictable run-time situations. The latter is probably the strongest incentive for exploiting such approaches also in the design of operating system components. This thesis is a part of the aforementioned research trend, as it is devoted to enhance robustness and responsiveness of an existing task scheduler named I+PI which is designed in the light of control theory. This scheduler works by partitioning a run-time modifiable amount of time, called the round time, among all the active tasks, and correcting on-line for any observed discrepancy. The fraction of the round time allotted to each task is also configurable on a per-task basis to best suit the tasks needs. The original scheduler was shown to have a performance closely chasing the EDF scheduler for schedulable task pools, and outperforming it for pools that may become transiently unschedulable. However, a weakness was found in I+PI with pools of periodic tasks having highly asymmetric periods. Scheduling such task pools with I+PI calls for short round times, which increases the scheduling overhead. The contribution of this thesis is to improve I+PI's responsiveness-overhead trade-off by redesigning the control scheme and exploiting the concept of tickless kernels. In such kernels, the time system is designed in an aperiodic fashion that provides other subsystems with dynamic ticks rather than having a periodic interrupt from the system timer. The performance of employing a control theory based task scheduler on top of a tickless kernel is demonstrated in this work through suitable experiments showing that it outperforms the original I+PI scheduler in all the evaluated cases, and tends to be strictly better than EDF in many situations. We will show that the new approach is a highly qualified candidate in real-time applications with or without deadlines and without imposing any particular symmetry on the arrival pattern of tasks.

## Italian abstract

L'uso di metodologie teoriche nella progettazione dei sistemi è una strada seguita in molti campi dell'ingegneria per via della sua semplicità, flessibilità e uniformità delle soluzioni nonchè per la possibilità di valutare i risultati anche in situazioni imprevedibili di esercizio. Quest'ultimo è probabilmente il più forte incentivo per sfruttare tali approcci anche nella progettazione di componenti di un sistema operativo. Questa tesi è parte di questa linea di ricerca, in quanto è dedicata a migliorare la robustezza e la reattività di uno scheduler esistente denominato I + PI, progettato usando la teoria del controllo. Questo scheduler partiziona un tempo modificabile a run-time, detto tempo di round, tra i task attivi nel sistema, correggendo on-line eventuali discrepanze osservate nel loro comportamento. La frazione del tempo di round assegnata a ogni task è anch'essa configurabile, e può essere diversa per ogni task in modo da meglio adattarsi alle necessità specifiche dei task. Lo scheduler originale ha dimostrato delle prestazioni che si avvicnano allo scheduler EDF nel caso in cui il task pool sia schedulabile, e prestazioni migliori di EDF nel caso in cui il task pool diventi temporanemaente non schedulabile. Tuttavia, lo studio dello scheduler I+PI ha evidenziato un problema nel caso di pool di task periodici con periodi molto diversi tra loro. In queste condizioni è necessario scegliere tempi di round molto bassi, cosa che causa un impatto sull'overhead di scheduling. Il contributo di questa tesi è quello di migliorare le performance di I+PI in queste condizioni, riprogettando lo schema di controllo e traendo vantaggio dalle caratteristiche di un kernel tickless. In questi kernel, il sottosistema temporale è progettato in modo aperiodico, generando interrupt solo quando richiesto invece di avere interrupt ad un periodo fisso. Le performance del nuovo scheduler e del kernel tickless sono state verificate tramite un'opportuna campagna sperimentale. I risultati mostrano come le performance del nuovo scheduler siano strettamente superiori allo scheduler I+PI originale, e migliori di EDF in alcuni casi. Mostreremo che il nuovo approccio è un ottimo candidato in applicazioni real-time con o senza deadline e senza imporre una particolare simmetria sul modello di arrivo dei task.

## Chapter 1

## Introduction

Apart from design choices imposed by hardware architectures, operating system components have been heavily depending on heuristic designs and algorithms and thus, maintenance and evolution of system software have become increasingly difficult with the ongoing advances in hardware. For instance, in [14] it is evident that the Linux CFS (Completely Fair Scheduler)[6], albeit being operational, has a serious inefficient processor utilization problem that have been just revealed after a long time. Or, there are some other efforts such as [17] and [24] to redesign kernels from scratch to become inline with and better utilize the newest hardware capabilities. As far as this work is concerned, some of the problems are still dealt with to a significant extent through the use of heuristics that are not rooted in formal and strong mathematical models that allow better uniformity in design and assessment methods. Various parts of kernel such as task scheduler, load balancer, USB bandwidth scheduler and etc., can be viewed as closed-loop time-varying systems to be controlled, hence, a right tool for modeling these problems would be Control Theory.

An interesting research work in this direction is the I+PI scheduler[16] which proposes a model for single-core scheduling problem ensuring responsiveness and fairness through two control loops in which an outer loop makes sure that all the active tasks will receive processor's control within a user-

defined window of time - i.e. round duration - and an inner loop that ensures each task consumes a prescribed portion of the round duration, hence, guaranteeing fairness. For instance, if the round duration is 5 milliseconds, all active tasks will be processed at least once every 5 milliseconds. I+PI easily outperforms MFQ (Multilevel Feedback Queue) and closely follows EDF scheduler in the Hartstone[28] benchmark in terms of the first deadline miss but, outperforms both in the number of deadlines missed over a specific duration in which the processor utilization exceeds one hundred percent which means it does not suffer from the domino effect <sup>1</sup> of EDF and proves to be a good substitute in real-time applications <sup>2</sup>.

The purpose of this work was to improve the performance of I+PI scheduler through the use of high-resolution timers and the tickless kernel design pattern which is relevant since the equations of dynamic systems do not usually match perfectly with periodic time steps unless endowed with a high enough resolution. Naturally, the higher the system timer's resolution, the more frequent the kernel invocation will be and thus the unnecessary overhead. However, during the investigations into I+PI, another potential responsiveness improvement regarding the tasks that yield the control voluntarily was discovered in which they would not gain the processor back in the same and next round in the case that their inactivity time is less than the end of the next round. For instance, consider a thread that sleeps after consuming half of its prescribed CPU time. If it wakes up during the current round, it just misses the remaining half of the CPU time allotted to it but, if it wakes up after the end of the round, not only the thread will lose its share from the current round, it is also not scheduled during the next round which would be problematic in the case that the round duration is long. This issue

<sup>&</sup>lt;sup>1</sup>In the scheduling of tasks with deadlines, the domino effect is referred to the situation where all the deadlines are missed. This can happen with EDF scheduler when utilization is over hundred percent.

<sup>&</sup>lt;sup>2</sup>Applications wherein the correctness of a computation relies not only on the logical outcomes of the computation but also on the time at which the results are produced are referred to as real-time[4]

was not revealed before [16] since the round duration was set to a very small value that prevented the gap from being large enough to miss the deadlines.

In fact, the inner loop was designed to account for fairness, based on its classic definition [12] that essentially is about assigning a prescribed amount of a shared resource (Processor's time in this case) to each task, however, a task may not need the whole share assigned to it and yields on purpose - for instance, consider a periodic task sending a signal from a wireless sensor node which has been assigned a larger window of time necessary to prepare and transmit the packet. The fact that tasks are not always striving for the resource impacts the responsiveness and this has led to a modeling error in I+PI that tries to force threads to consume as their prescribed CPU share for them which is not always possible.

In conclusion, this work provides a new control scheme along with proper actuation layer to solve the responsiveness problem of I+PI while dealing fairness nominally.

#### **1.1** Brief literature review

The classical time-invariance assumption is often not met in real-life applications. Considering the OS kernel as an arbiter of shared resources, the assumption hardly fits the setting where tasks' demand of those resources does not remain constant during their lifetime. Therefore, it is inevitable to provide the kernel components with adaptation capabilities in such unpredictable environment. This fact is even more relevant when focusing on real-time or embedded systems with limited resources, power and (soft or hard) deadlines.

A common practice for the introduction of adaptive abilities in systems design is to extract and exploit feedback signals from the system at runtime that is equivalent to the closed-loop system design in control theory jargon. A classic example would be the MFQ scheduler which provides the system with different task queues and selects the next task to run from the first non-

empty queue with the highest priority. The priority would change during the runtime as the result of using feedbacks (For instance, the last time a task has been scheduled is used as a feedback to possibly increase its priority if it is considerably far in the past) and consequently, the CPU time allotted to the tasks are adapted. Therefore, it is not a new concept to use feedbacks as knobs for online adjustment of the system, however, especially during the last decade, research communities have shed light to the importance of utilizing control models besides choosing the right feedback signals. For instance, [29] proposes a perspective shift from traditional open-loop scheduling of network resources to a closed-loop one in order to mitigate the impact of limited bandwidth and variable workload on the QoC(quality-of-control) of networked control systems. The aim of this work was to maximize the overall QoC by dynamically allocating available network bandwidth through a codesign of control and scheduling and an integrated feedback scheduler that enables flexible QoC management in dynamic environments (under both underloaded and overloaded network conditions). The paper [2] is another research work utilizing feedback signals - and control theory more explicitly - to control CPU usage and memory consumption of a virtual database machine in a data center under a time-varying heavy workload through a design of multiple SISO (single input - single output) feedback controllers. One of the most recent works in this direction and pertaining to real-time systems is [1] which targets both energy consumption and processor utilization where the processor is provided with DVFS (Dynamic Voltage/Frequency Scaling). The paper [1] proposes a feedback scheduler maximizing battery life while minimizing deadline miss ratio by adjusting the processor speed in proportion to the available energy in the batteries and the processor utilization. All the aforementioned works follow the ARTIST2 project which was aimed at defining a roadmap on control of real-time computing systems [3]. In the vast majority of cases, the controlled item is the allocation of computing and communication resources.

Limiting the scope of the topic to the scheduling problem, the same tech-

nique is applicable through viewing the task pool as a system with measurable outputs that are used as feedback signals to adjust the policy of the scheduler. In this regard, in the article [15], Lu et al. propose a conceptual framework for introducing Feedback Control in real-time operating system scheduling. A remarkable contribution of their work is the introduction of the distinction between open- and closed-loop policies in which the latter corresponds in system-theoretical terms to feedback. In their work, the authors proposed to use the estimated future utilization as a control signal and to derive from the desired utilization and miss ratio an admission controller that allows tasks to enter the system. Notice that admission control, in general, is very popular in the context of web servers, where the tasks could be rejected to preserve utilization. Thus the application domain is the main difference between the referenced paper and I+PI (and therefore this thesis) i.e. in one case it being a server and in the other an embedded device. Consequently, the amount of control and the place where this control is introduced is different.

As the target environment for the proposed scheduler in this thesis is embedded devices that are limited in power and resources, it is worthwhile to highlight another remarkable trend in operating systems i.e. the "Tickless" kernels. Provided that such a kernel eliminates unnecessary system calls, advantages in terms of performance and power usage are delineated by various research works and many operating systems including Linux[18, 8, 9] have been switched in this manner for the same reasons. For instance, in [13] authors have characterized power consumption of the POWER6 system in different layers including the OS and, have successfully demonstrated the remarkable effect of tickless Linux kernel.

#### **1.2** Contributions

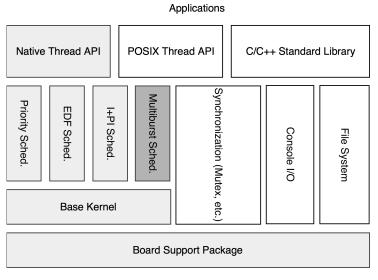

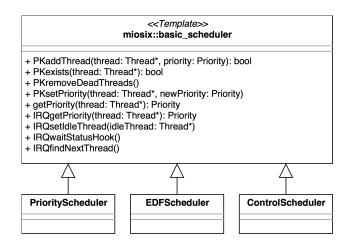

This thesis is a contribution to the research trend trying to incorporate control theory into the design of operating system components with the focus on single processor scheduling and in fact, pursues the thesis "Control based design of OS components" [26]. This section delineates briefly the additional work performed through this thesis with respect to [26] that encompasses the design and implementation of I+PI which is the ground for the new scheduling mechanism (Multiburst scheduler) introduced in this thesis. Both I+PI and Multiburst schedulers are implemented in C++ and on top of the Miosix kernel[7] which is an open source OS kernel running on 32-bit microcontrollers. It provides a platform for the multi-threaded programming model where applications are statically linked with the kernel. Figure 1.1 depicts architecture of Miosix in which blocks shaded in gray correspond to amendments made as the contribution of this work.

Hardware

Figure 1.1: Miosix kernel architecture

As it is mentioned earlier, the work can be categorized into two main groups i.e. transforming Miosix into a tickless kernel, and design and implementation of the new scheduler.

• Since Miosix kernel is targeting multiple architectures which in turn provide different hardware capabilities for timing and synchronization, the first task was to design an abstract uniform interface for the kernel to provide the required base for both periodic and continual system timer. The interface enables the kernel or scheduler to set the next interrupt in nanoseconds (and regardless of the resolution) while processing the current one.

- Modification of the startup flow to make the kernel inline with the new timer interface. This involves bypassing of the usual periodic systick timer <sup>3</sup>, setting up the selected timer peripheral and configuring the desired resolution through the instantiation of the proper implementation of the interface.

- Implementation of timer/counter drivers according to the new interface for the various architectures and embedded boards supported by Miosix.

- Principally, the kernel was using the systick for two reasons: task preemption and management of sleep/wake-up of threads. Thus, the next modification to the kernel was pertaining to the system calls in charge of initiating preemptions and a subset of Miosix's native thread API. Moreover, since Miosix is transformed to a tickless kernel, all the timedependent routines have been amended to operate in terms of nanoseconds rather than "kernel ticks" which can vary from a configuration to the other.

- With the new interface in place, an additional task of setting the next context switch point is implemented for Miosix schedulers as there are no automatic periodic interrupts anymore. This enables the scheduler to avoid prescribing fixed CPU allocation time and behave in an adaptive fashion. Whether the scheduler is exploiting this feature or not,

<sup>&</sup>lt;sup>3</sup>Systick is the default timer/counter peripheral circuit found in every computing system which supports multi-tasking and is used to fire an interrupt according to a configurable period of time. OS kernels use this peripheral to gain the control back from the running task and perform a context switch.

all the existing schedulers should set the next context switch point in order to fully integrate with the new tickless kernel.

- A comprehensive review of the I+PI scheduler has been done and the root cause of its weakness regarding responsiveness is detected. One of the major contributions of the thesis is the design of a new control scheme to establish a better trade-off between response time and the number of context switches.

- The new control scheduler (Multiburst) is implemented according to the generic interface provided by Miosix and on top of the new tickless kernel. After performing a number of profiling tests to verify the functionality, some standard benchmarks have been used to evaluate the performance and cost of the Multiburst scheduler with respect to that of EDF, MFQ, and I+PI.

#### **1.3** Thesis organization

The thesis is structured as follows.

Chapter 2 illustrates the key concept of tickless kernels and presents the recent practice in existing operating systems. Then it provides a detailed description of the previous time system of Miosix kernel and integration of the new method along with a general view of timer/counter drivers implemented to provide the required hardware support. In chapter 3 the scheduler subsystem of Miosix and implementation of I+PI is described along with the transition steps to derive the new scheduler. Chapter 4 is dedicated to the extensive benchmarks used to evaluate the correctness and performance of the new approach and the results are compared to that of Round Robin, EDF and I+PI schedulers with/without presence of dynamic ticks provided by the tickless kernel. Finally, the last chapter draws conclusions regarding the work presented in this thesis and outlines the future directions and possible extensions to the work.

## Chapter 2

## Tickless kernel

The system timer is one of the most crucial requirements of a multi-tasking operating system from hardware support point of view. It is used in order to fire an interrupt request every once in a while so that the kernel can regain the control by preempting running tasks mainly in order to switch the context to the next task to run according to a scheduling policy. A common methodology that has been practiced in the design of virtually all types of kernels was to utilize a periodic timer/counter to generate the aforementioned interrupt request at regular intervals, gave birth to the concept of the tick of the kernel.

However, since the kernel tick is not only used for context switches, but also for timekeeping and waking up tasks that sleep, the kernel tick imposes a tradeoff between the resolution of the **sleep** primitive (and the one to return the current time, at least in kernels that use the tick for both) and the overhead of the ticks themselves. In theory, one could have a ticked kernel with wakeups at microsecond resolution, but it would require one million tick interrupts per second, effectively overloading the CPU with interrupts.

Fortunately, the availability of timer/counter circuits with large registers for timekeeping (counter and capture registers) has endowed system software with the possibility to have the processor interrupted whenever it is necessary rather than relying on the periodic IRQ for kernel intervention and hence,

one could design a tickless kernel. A tickless kernel refers to an OS kernel that employs an aperiodic time scheme wherein timer interrupts are only delivered as required by the kernel space code. Moreover, avoiding unnecessary ticks allows the kernel to put idle processor cores in the deep-sleep state as much as possible in order to decrease power consumption. Although the advantages of this fundamental change may be more tangible in real-time and/or embedded kernels which are run on lower performance hardware platforms with limited power supplies, general purpose operating systems such as Linux, Minix<sup>1</sup>, Solaris, Windows and OSX have also undertaken the same path of transforming their kernels to a tickless one. The Linux kernel on s390 from 2.6.6[27] and on i386 from release 2.6.21 can be configured to turn the timer tick off (tickless or dynamic tick) for idle CPUs using CONFIG\_NO\_HZ, and from 3.10 with CONFIG\_NO\_HZ\_IDLE extended for non-idle processors with CONFIG\_NO\_HZ\_FULL. The XNU kernel<sup>2</sup> in OSX 10.4 on, and the NT kernel in Windows 8 kernel  $^3$  are also reported to be tickless. The Solaris 8 kernel introduced the cyclic subsystem which allows arbitrary resolution timers and tickless operation<sup>4</sup>.

### 2.1 Time subsystem in Miosix

This section provides essential information about the time subsystem of Miosix kernel necessary to understand the transition into a tickless counterpart that is exploited to design a highly responsive task scheduler later, hence, the description provided here pertains to the state of the Miosix kernel before the fulfillment of this thesis.

Before stepping into implementation of the kernel it is worthwhile to point out an important naming convension in Miosix that hints the state in which

<sup>&</sup>lt;sup>1</sup>http://wiki.minix3.org/doku.php?id=tickless

$<sup>^2</sup> See \ e.g.: \ https://github.com/darwin-on-arm/xnu/blob/master/osfmk/arm/rtclock.c$

<sup>&</sup>lt;sup>3</sup>Bright, Peter. "Better on the inside: under the hood of Windows 8", October 2012 <sup>4</sup>Bryan Cantrill (former Solaris kernel engineer) comment at

https://news.ycombinator.com/item?id=13091162 (Retrieved 2017-01-07)

a routine should be called. The names prefiexed by IRQ should be called if and only if interrupt requests are disabled and those that start with PK can be invoked securely only when the kernel is paused, hence, there would be no preemption or context switch.

Limiting the scope of the discussion to task management and scheduling, Miosix kernel provides a native definition and implementation for thread-/process, a pointer to the current running thread and its context information and a linked list sorted by wake-up times of the threads (a.k.a sleeping list) and some routines to manage the list. On the other hand, the scheduler provides a function IRQfindNextThread which is responsible for setting the next thread to run by changing the current thread pointer, saving and, switching the context defined in the kernel. This function is called whenever a thread yields the execution <sup>5</sup> or upon a preemption call invoked by the Systick interrupt (fired by the system timer). This workflow is distributed throughout the following parts of the kernel.

- **Portability Interface** which abstracts the hardware layer and endows the kernel with an architecture independent interface which contains:

- Architecture dependent startup code (function IRQportableStartKernel).

- Sequence of instructions required to perform a context switch and enable/disable interrupts.

- Interrupt handlers for performing preemption (function Systick\_Handler) and yielding (function ISR\_Yield). Systick\_Handler will call another function (IRQtickInterrupt) which accounts for a single tick of the kernel and leads to a context switch.

- The basic kernel interface that defines and implements the following independently of the hardware which is encapsulated by the portability interface:

$<sup>^5 \</sup>rm upon$  calling sleep primitives, calling peripheral services that lead to an I/O waiting status or, the will to terminate.

- Hardware independent startup routine which creates the main thread<sup>6</sup> and the Idle thread <sup>7</sup> and calls the function IRQportableStartKernel to configure and setup the interrupt controller device and finally the system timer to enable kernel's ticks.

- Functions and RAII classes<sup>8</sup> for toggling the interrupts

- Functions and RAII classes to pause/resume the kernel, hence, enabling/disabling preemption which should be respected by scheduler.

- A native definition and implementation of threads which particularly includes front-end functions for a thread to yield or sleep.

The sleep functions are fed with number of ticks of the kernel which in turn correspond to ticks of the system timer.

- Information about the current thread and context which is used by the scheduler's code to perform context switches

- A linked list sorted by the kernel's tick in the order which threads desire to become ready again and the two functions IRQaddToSleepingList and IRQwakeThreads. The former is called by threads whenever a thread desires to sleep for a particular amount of ticks while, the latter is called upon every tick (by IRQtickInterrupt) to check whether it is time to activate some sleeping threads or not. This check being done on a fixed time step, implies imprecision when dealing with time-critical tasks or unnecessary kernel code execution when the first thread activation point is far in future.

Therefore, for Miosix to be transferred into a tickless kernel, two major workflows should change i.e. whenever a tick occurs and upon current thread's

<sup>&</sup>lt;sup>6</sup>In Miosix, the user's application is compiled with the kernel through a function named main() which is executed by the main thread. This thread can spawn other threads later on.

<sup>&</sup>lt;sup>7</sup>The Idle thread will be selected when there is no active task to run e.g. when all the threads are in a waiting/sleeping state

<sup>&</sup>lt;sup>8</sup>Resource acquisition is initialization

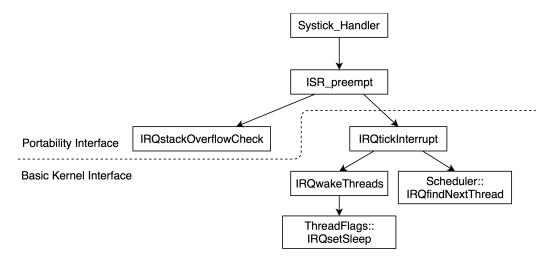

will to sleep. Figure 2.1 represents the call graph for the tick processing in the kernel.

Figure 2.1: Miosix - Kernel tick call graph

The IRQtickInterrupt can be called whenever a preemption should take place or just a thread should be woken which does not necessarily lead to a context switch. Thus, in tickless setting, this flow should change in particular in a way to distinguish between these two cases so as to eliminate the dependency of the time domain resolution of sleep primitives with that of scheduler interventions. Moreover, since there would be no periodic timer interrupts, the scheduler should set the next preemption point in IRQfindNextThread function.

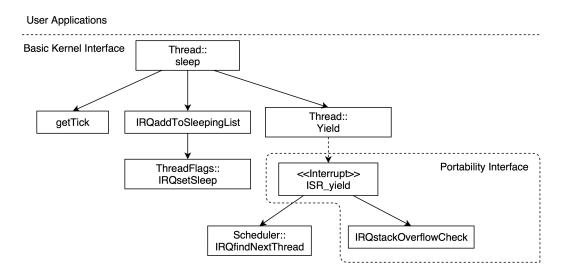

As for the second workflow pertaining to the sleep primitive routines which is depicted in figure 2.2, it is clear that sleep functions should not depend on kernel tick any longer and instead rely on a universal concept i.e. the time unit (e.g. nanoseconds). In this regard, the sleeping list should be ordered by the actual time unit and IRQaddToSleepingList should function aligned with the scheduler to keep the next interrupt to the minimum of the first wake-up time (head of the sleeping list) or the next preemption point set by the scheduler during the previous preemption.

Figure 2.2: Miosix - Sleep primitive call graph

# 2.2 Transformation of Miosix into a tickless kernel

In addition to the benefits enumerated about tickless kernels and the trend of other operating systems towards this design, having Miosix kernel operate in tickless mode is a crucial requirement for the purpose of this thesis. As it will be explained deeper in the next chapter, the CPU time alloted to the tasks may significantly vary due to some tuning parameters and the control scheme behind the new scheduler proposed by this work. Therefore, the following steps have been taken in order to provide the scheduler with an aperiodic timing system - hence the ticklessness - while keeping the changes so few that do not disrupt the operation of other modules relying on the previous time system of the kernel.

- Defining a new interface for the kernel as the unified model of timer drivers used to manage preemptions in different architectures

- Modification of kernel startup routines to switch from systick to the new interface

- Integration of task sleep/wake-up management in the kernel and thread interface with the new time subsystem

- Decoupling kernel's time unit from the underlying hardware from user perspective by introducing an internal tick-to-nanosecond conversion

- Implementation of new high resolution timer drivers for Miosix supported architectures according to the new interface

- Integration of existing schedulers with the new interface, making them able to cause preemptions.

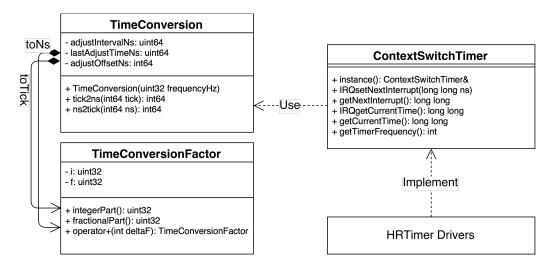

#### 2.2.1 Context Switch Timer interface

The simple scheme of having an interrupt handler being invoked periodically by the **systick** timer which in turn calls the preemption routine, is replaced by the interface shown in the figure 2.3 that is defined to support aperiodic configuration of next preemption point and automatic conversion of timer ticks to/from nanoseconds so as to separate timing logic of other components and user applications from the speed configured for the hardware timer.

Figure 2.3: Context Switch Timer interface

Depending on the architecture the kernel is compiled for, there should be a proper implementation of the ContextSwitchTimer as a singleton class which is instantiated by the hardware dependent kernel startup routine i.e. IRQportableStartKernel. It is expected that the implementation provides an apparently infinite time horizon which always moves forward through the use of large enough hardware or hardware/software counter registers. For instance, a high resolution timer operating at 1 GHz (one tick every nanosecond) with a 64-bits counter register, the system can keep track of the time without any rollovers for 584 years which is large enough to be considered an infinite upperbound for any system's uptime.

However, most of the timer/counter circuits usually support 16/32-bit registers that would easily overflow in a very short time - 65 microseconds and 4.3 seconds respectively - and therefore they must be expanded through software controlled memory by the driver.

#### 2.2.2 Implementation

The ContextSwitchTimer interface illustrated in the previous section has been implemented and tested on the architectures reported by the table 2.1 for which none of the target architectures provides 64-bits registers and thus, the counter is extended by the driver through additional variable. Of course the expansion is achieved at the cost of additional interrupt requests due to overflow of the hardware register and therefore it is really important to limit the overflow interrupt handler to few instructions and decrease the timer's frequency as low as possible.

|   | Architecture - SoC            | Peripheral Timer Used | Register Capacity |

|---|-------------------------------|-----------------------|-------------------|

| 1 | Cortex<br>M3 - STM32 [23]     | TIM2                  | 16 bits           |

| 2 | CortexM3 - EFM32GG [20]       | TIM3                  | 32 bits           |

| 3 | Cortex<br>M3 - STM32F2 [21]   | TIM2                  | 32 bits           |

| 4 | Cortex<br>M4 - STM32F4 $[22]$ | TIM2                  | 32 bits           |

Table 2.1: Architectures for which tickless Miosix has been ported into

The listings below present the implementation of functions defined by ContextSwitchTimer in pseudocodes equivalent to the C++ implementation of drivers for the target archtectures.

The timers provide two registers keeping track of current tick count and a checkpoint set by the software. When the value of the former becomes equal to the latter a "Capture" IRQ will be fired that is the usual capacity found in virtually all the timer/counter peripherals and is exploited to notify the kernel about the next time event. Therefore, the driver need two variables as the most significant 32 bits of the total value.

| t |

|---|

|   |

|   |

|   |

|   |

|   |

| t |

In order to set the next timer intervension, a time value in nanoseconds should be taken as the input and its equivalent in timer's tick should be stored in the checkpoint upper part variable ms32chkp concatenated with the register. The driver should also react promptly if the point is in the past as the time is not periodic and always increasing and thus the event could be missed eventually. Therefore, after setting the next checkpoint on the timer, the driver should check and raise an interrupt if the point is in the past. The order matters since otherwise, it is possible to have a checkpoint close enough to the current time that would be passed before the timer register is set.

| Algorithm 2: ContextSwitchTimer driver - Setting the next event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Input: ns: Desired time point in nanoseconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| <b>Precondition:</b> Interrupts should be disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| tick = ns2tick(ns);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| $ms32chkp = tick BIT_AND upperMask;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| timer. $CCR = tick BIT_AND$ lowerMask;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| if checkpoint is in the past then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Set lateIrq;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |