# POLITECNICO DI MILANO

Scuola di Ingegneria Industriale e dell'Informazione

Master of Science in Automation and Control Engineering

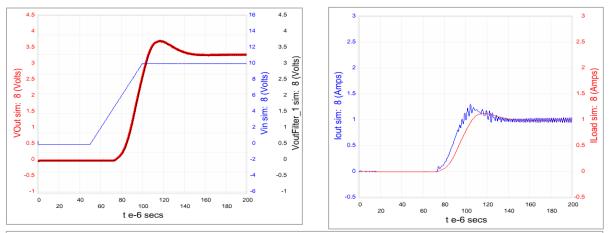

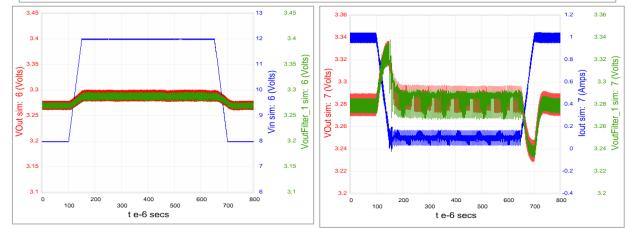

# TUNING AND CONTROLLING OPTICAL TELECOMMUNICATION CHANNELS BASED ON RING RESONATOR MODULATORS

SUPERVISOR: Prof. Alberto Leva

Master thesis by: Seyed Alireza Tabatabaei Mashayekh Student ID: 833196

Academic Year 2016 – 2017

Dedicated to my mother

# Acknowledgments

I would like to express my special appreciation to my advisor Prof. Alberto Leva for supporting me by a valuable guidance and encouragement.

I would like to appreciate Prof. Dr. Jeremy Witzens, Dr. Florian Merget and Dr. Alvaro Moscoso Martier about supporting me during the 1 year hardworking on this project by providing a very precious practical and theoretical guidance in IPH- Integrated Photonics at RWTH- Aachen university by sharing a valuable achievements and infrastructures to realize this master project.

Special thanks to my parents for their support and attention throughout my whole life in general.

# Abstract

Silicon micro ring resonators have been hailed for their potential use in next-generation optical interconnects. However, the functionality of silicon micro ring based devices suffer from susceptibility to thermal fluctuations that is often overlooked in their demonstrated results, but must be resolved for their future implementation in microelectronic applications. In this work we survey the emerging efforts that have been put forth to resolve these thermal susceptibilities and provide a comprehensive discussion of their advantages and disadvantages. The growing bandwidth needs within data applications have motivated the replacement of traditional electronic links with optical links for information networks as diverse as data centers, supercomputers, and fiber-optic access networks. Applications such as these stress the traditional portfolio of optical components, rebalancing the emphasis from expensive highperformance components towards low-cost high-volume components that can be closely integrated with electronics. With these considerations in mind, the silicon photonics platform has received wide attention for its ability to deliver the necessary bandwidth required at an economy-of-scale that will be enabled by its compatibility with CMOS fabrication processes. Online controlling of the micro rings is the main goal of the project presented in this thesis, not only to obtain a production-grade package in commercialized scale and take advantage of the optical telecommunication facilities in a feasible way but also to achieve user friendliness and independence of the used PC/Spectrometer in tuning the optical telecommunication channels while in data transmission.

# Table of Contents

| ١.  | Chapter1: Introduction                   | .13  |

|-----|------------------------------------------|------|

|     | Optical telecommunication                | .13  |

|     | Overview                                 | .13  |

|     | Optical Data modulation                  | .14  |

|     | Silicon photonics                        | . 17 |

|     | Silicon photonics towards silicon Laser  | .17  |

|     | Laser                                    | . 18 |

|     | Key Optical Components                   | . 22 |

|     | Overview                                 | . 22 |

|     | Interconnection                          | .23  |

|     | Receiver                                 | . 29 |

|     | Optical Amplification                    | .31  |

|     | Optical filters                          | .34  |

|     | Multiplexer & De-Multiplexer             | .36  |

|     | Motivation and goals of this project     | . 37 |

|     | Organization of content                  | . 38 |

| II. | Chapter 2: WDM System subject to control | .40  |

|     | Overview                                 | .40  |

|     | WDM in Macro Scale                       | .41  |

|     | WDM System Architecture in Micro Scale   | .43  |

|     | Laser                                    | .44  |

|     | Transmitter                              | .45  |

|     | Receiver                                 | .47  |

|     | WDM Control System                       | .48  |

| II  | I. Chapter 3: Hardware                   | .50  |

|     | Overview                                 | .50  |

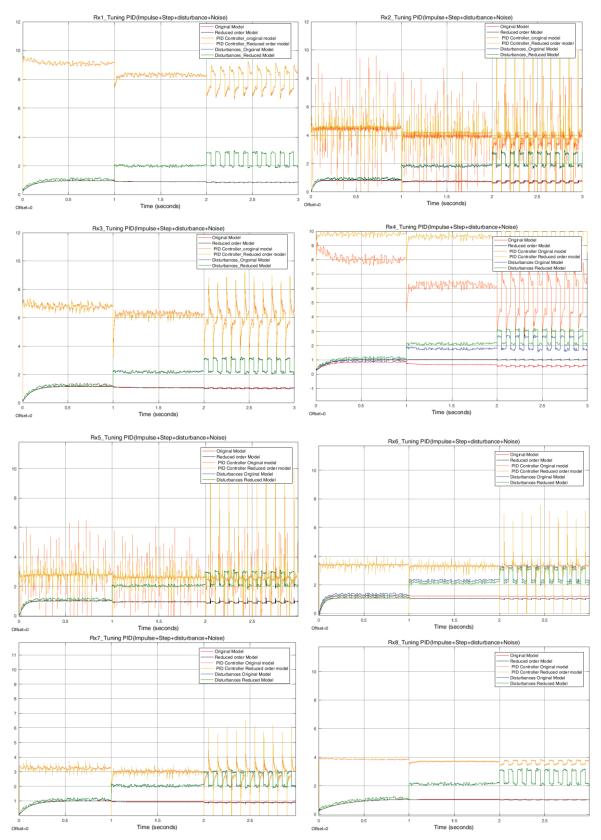

|     | Microcontroller – Xmega256A3BU           | .51  |

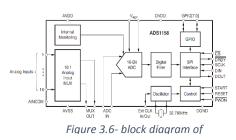

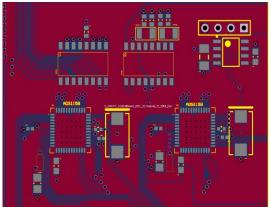

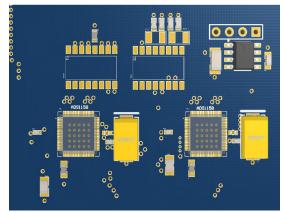

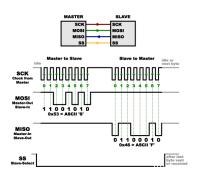

|     | Analog to Digital Convertor (ADS1158)    | .54  |

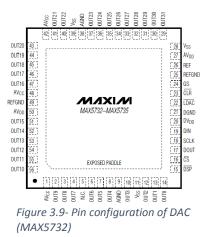

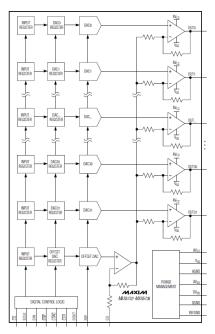

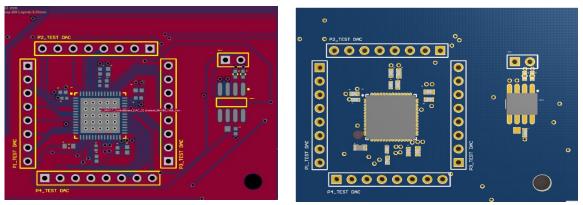

|     | Digital to Analog Convertor (MAX5732)    | .56  |

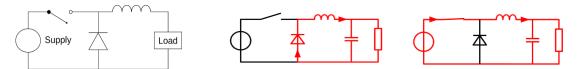

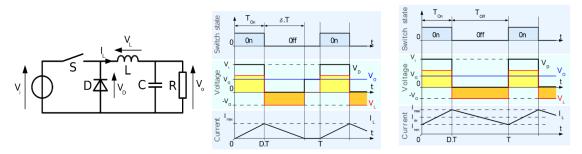

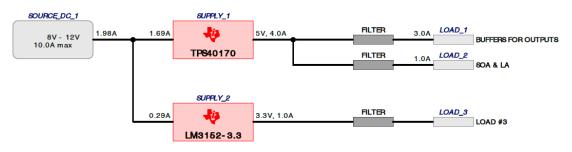

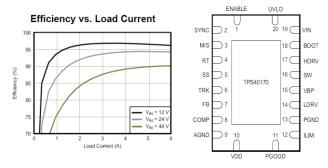

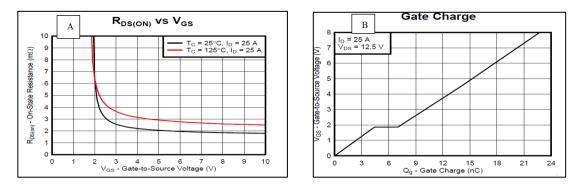

|     | Power supply                             | . 58 |

|     | Trans-Impedance Amplifier (TIA)          | .69  |

|     | Output Buffers (OPA4251)                 | .73  |

|     | High Current Output Buffer (OPA567)      | .76  |

| ١V  | 7. Chapter 4: Software                   | .79  |

|     | Overview                                 | .79  |

|    | System Under control                                      | 80    |

|----|-----------------------------------------------------------|-------|

|    | The closed-loop transfer function                         | 82    |

|    | Analog disturbances in a digital system                   | 83    |

|    | Analog sub system evaluation                              | 84    |

|    | Data Acquisition and Identification                       | 91    |

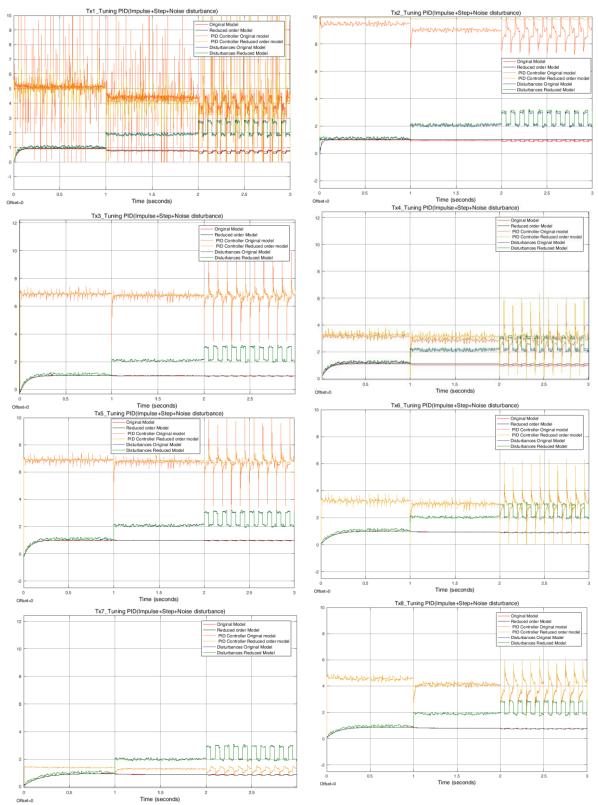

|    | PID Controller Simulation                                 | 99    |

|    | Simulation of PID for receiver side                       | . 102 |

|    | Approaches to control System                              | . 104 |

|    | Approaches for Realization of Control Methods by Hardware | . 112 |

| V. | Chapter 5: Measurement Results and Conclusion             | . 117 |

|    | Overview                                                  | . 117 |

|    | Measurement Results                                       | . 117 |

|    |                                                           | . 121 |

|    | Conclusion and Prospects                                  | . 123 |

# I. Chapter1: Introduction

# **Optical telecommunication**

#### Overview

Optical communication is any type of communication in which light is used to carry the signal to the remote end, instead of electrical current. Optical communication relies on optical fibers to carry signals to their destinations [1]. A modulator/demodulator, a transmitter/receiver, a light signal and a transparent channel are the building blocks of the optical communications system. Because of its numerous advantages over electrical transmission, optical fibers have largely replaced copper wire communications in core networks in the developed world.

Since the development of low-loss optical fiber cables in the 1970s, optical communications became one of the most popular methods of communication. Optical communication systems consist of the following components:

- 1. Transmitter: Converts and transmits an electronic signal into a light signal. The most commonly used transmitters are semiconductor devices, such as light-emitting diodes (LEDs) and laser diodes.

- 2. Receivers: Typically consist of a photo-detector, which converts light into electricity using the photoelectric effect. The photo detector is typically a semiconductor-based photodiode.

- 3. Optical Fiber: Consists of a core, cladding and a buffer through which the cladding guides the light along the core by using total internal reflection.

The main benefits of optical communication include high bandwidth, exceptionally low loss, great transmission range and no electromagnetic interference. The cons of optic communication include the high cost of cable, transmitter/receiver and other support equipment, and the skill and expertise required during cable installation and interconnection.

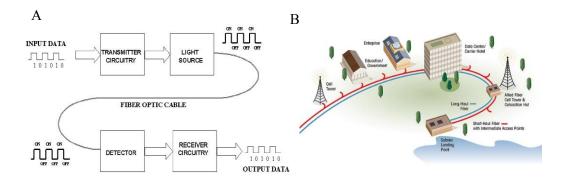

An overview of optical telecommunication data transmission cycle is shown in Figure 1.1(A) which contains Input & Output Data, Transmitter/Receiver, Optical fiber and Detectors. A sample of an Optical Telecommunication Network is shown in Figure 1.1 (B).

Figure 1.1 – (A) Block Diagram of Optical Telecommunication Cycle (B) Optical Telecommunication Network

# **Optical Data modulation**

#### Overview

a)

#### Direct Modulation

Digital signals consist of logical 1s and 0s, which readily corresponds to electrical ON and OFF states, or to two discrete voltage (or current) levels. The typical optical communications light source is a laser diode, which is easily modulated by controlling its current. Several factors limit the upper frequency at which a laser diode can be modulated. These include the time constants (frequency response) of the driving circuitry, the physics of the diode itself, and the characteristics of the transmission medium, which is typically an optical fiber. Microwave design and layout techniques have been used to assure performance of driving circuitry well into the GHz range, removing this as a major limitation [2]. Optical fibers have a certain amount of dispersion, which introduces uncertainty at the detector, related mainly to transmission distance [3]. This uncertainty is worse at high data rates—integration can help solve the uncertainty, and there is less integration time with the shorter highspeed pulses.

Ultimately, direct modulation is limited by the characteristics of the diode itself. A full turnon/turn-off cycle represents a significant electrical and thermal stress, which can result in a frequency shift (chirp), transients (ringing), as well as reduced operational lifetime, of the laser diode. One method of dealing with these effects is to apply a modulated "radio signal" to the diode. The current swing is reduced, which improves reliability, and the bandwidth is greatly increased because the diode's drift and transient responses are reduced. But this technique also greatly reduces the signal-to- noise ratio, which reduces the range, and it requires more complex driver and detector circuitry.

#### *b) Indirect Modulation*

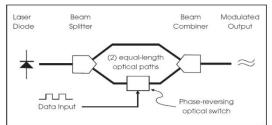

Modulation of a continuous light beam removes the laser diode-related problems at the cost of greater complexity. It also eliminates the signal-to-noise problems of applying a modulated subcarrier. The stable light source allows maximum transmission distance for a given amount of dispersion in the fiber. Established methods include delivering the data to electrically modulated crystalline materials such as lithium neonate. These devices can rapidly switch the light beam between a direct signal path, or split the beam into two paths with 180-degree phase shift, which cancel when recombined. This provides electrically controlled on-off transitions that do not affect the light source. The other common method uses electro-absorption (EA) modulators, usually a semiconductor material that can be switched between trans missive and opaque states to provide the on-off transitions. Materials used in these modulators can be conveniently integrated with the laser diode. As with direct modulation, the driving circuitry uses microwave design and layout to couple high speed data streams to the modulating devices. The latest methods of achieving indirect modulation are fully integrated onto a single substrate. The latest developments in solid state optical switching are faster than EA, so switched optical paths are used, integrated onto the same substrate, with optical paths typically using transparent versions of the same material. Figure 1.2 is a block diagram of such an optical modulator, which can be further integrated with a detector onto a microprocessor or other device, as on-chip optical interface.

Figure 1.2- Functional diagram of an optical modulator

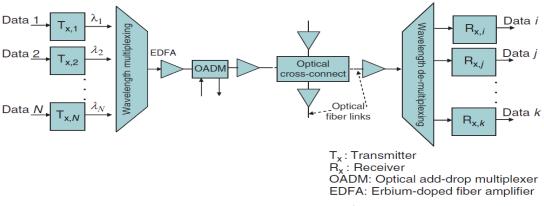

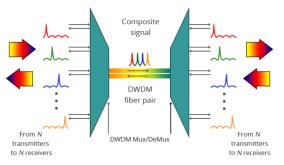

#### Wavelength Division Modulation WDM

Wavelength division multiplexing is a kind of *frequency division multiplexing* – a technique where optical signals with different wavelengths are combined, transmitted together, and separated again [4]. It is mostly used for optical fiber communications to transmit data in several (or even many) channels with slightly different wavelengths. In this way, the transmission capacities of fiber-optic links can be increased strongly, so that most efficient use is made not only of the fibers themselves but also of the active components such as fiber amplifiers. Apart from telecom, wavelength division multiplexing is also used for, e.g., interrogating multiple fiber-optic sensors within a single fiber.

Theoretically, the full data transmission capacity of a fiber could be exploited with a single data channel of very high data rate, corresponding to a very large channel bandwidth. However, given the enormous available bandwidth (tens of terahertz) of the low-loss transmission window of silica single-mode fibers, this would lead to a data rate which is far higher than what can be handled by optoelectronic senders and receivers. Also, various types of dispersion in the transmission fiber would have very detrimental effects on such wide-bandwidth channels, so that the transmission distance would be strongly restricted. Wavelength division multiplexing solves these problems by keeping the transmission rates of each channel at reasonably low levels (e.g. 10 Gbit/s) and achieving a high total data rate by combining several or many channels.

Two different versions of WDM, defined by standards of the International Telecommunication Union (ITU), are distinguished:

- Coarse wavelength division multiplexing (CWDM, ITU standard G.694.2 [6]) uses a relatively small number of channels, e.g. four or eight, and a large channel spacing of 20 nm. The nominal wavelengths range from 1310 nm to 1610 nm. The wavelength tolerance for the transmitters is fairly large, e.g. ±3 nm, so that unstabilized <u>DFB lasers</u> can be used. The single-channel bit rate is usually between 1 and 3.125 Gbit/s. The resulting total data rates are useful e.g. within metropolitan areas, if broadband technologies are not widespread in household.

- Dense wavelength division multiplexing (DWDM, ITU standard G.694.1 [7]) is the extended method for very large data capacities, as required e.g. in the Internet backbone. It uses many channels (e.g. 40, 80, or 160), and a correspondingly small channel spacing of 12.5, 25, 50 or 100 GHz. All optical channel frequencies refer to a reference frequency which has been fixed at 193.10 THz (1552.5 nm). The transmitters should meet tight wavelength tolerances. Typically, they are temperature-stabilized DFB lasers. The single-channel bit rate can be between 1 and 100 Gbit/s, and in the future even higher.

Due to the wide amplification bandwidth of EDFA (erbium-doped fiber amplifiers), all channels can often be amplified in a single device (except in cases where e.g. the full range of CWDM wavelengths is used). However, problems can arise from the variation of gain with wavelength or from interaction of the data channels (*crosstalk, channel interference*) e.g. via fiber nonlinearities. Enormous progress has been achieved with a combination of various techniques, such as the development of very broadband (double-band) fiber amplifiers, gain flattening filters, nonlinear data regeneration and the like. The system

parameters such as channel bandwidth, channel spacing, transmitted power levels, fiber and amplifier types, modulation formats, dispersion compensation schemes, etc., need to be well balanced to achieve optimum overall performance.

Even for existing fiber links with only one or a few channels per fiber, it can make sense to replace senders and receivers for operation with more channels, as this can be cheaper than replacing the whole system with a system with a higher transmission capacity. In fact, this approach often eliminates the need to install additional fibers, even though the demand on transmission capacities is increasing enormously.

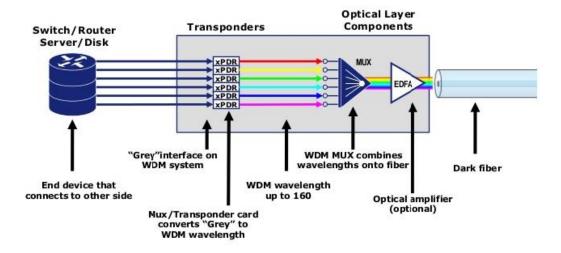

Apart from increasing the transmission capacity, wavelength division multiplexing also adds flexibility to complex communication systems. In particular, different data channels can be injected at different locations in a system, and other channels can be extracted. For such operations, *add–drop multiplexers* can be used, which allow one to add or drop data channels based on their wavelengths. Reconfigurable add–drop multiplexers make it possible to reconfigure the system flexibly to provide data connections between many different stations. In Figure 1.3 we can see a basic scheme of WDM.

Figure 1. 3 - Basic Scheme of WDM

# **Silicon photonics**

#### Overview

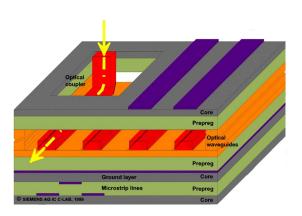

Silicon photonics can reuse the huge technology base and supply chain from electronics industry. Photonic components (i.e. modulators, detectors, sources) are fully compatible with CMOS technology [5]. Photonic links may replace copper links for very short distances and co-exist electronics in functional optoelectronic chips. The main role of silicon chip is bolded in optical telecommunication as interface of the data centers and optical fiber used in optical telecommunication. Figure 1.4 is an overview of the silicon photonic as an interface in optical data transmission cycle.

To summarize the pros and cons of the silicon photonic features we can introduce them as table 1.1.

| Advantage                               | Disadvantage                        |

|-----------------------------------------|-------------------------------------|

| Take advantage of CMOS platform         | Indirect bandgap material           |

| High index contrast (strong light       | Weak electro optic effect           |

| confinement, small footprint)           |                                     |

| Transparent in $1.3 - 1.6 \mu m$ region | Relatively lossy waveguides         |

| Devices with sub-wavelength dimension   | Lacks efficient light emission – No |

| feasible                                | electrically pumped Si laser        |

Table 1.1 – Pros and cons of Silicon photonics

### Silicon photonics towards silicon Laser

There are different approaches to have integrated laser sources on silicon chips but in practice there exist lots of non-ideal behavior of the light sources. Also, it is needed to control the affecting parameters on the laser sources which makes use of them difficult. Here we briefly introduce the approaches of the integration of laser sources on silicon chips.

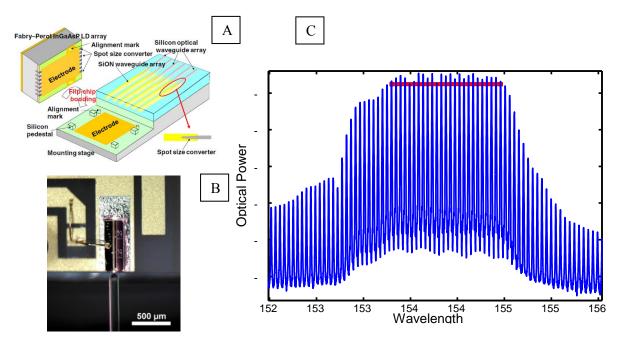

#### Hybrid silicon photonic integrated circuit technology Bonding of functional III-V active components onto silicon-on-insulator substrates

- **Bonding of III-V epitaxial layers** Wafer or die bonding of III-V films on Si and processing thereof

- hetero-epitaxial growth of III-V on Si selectively grow III-V crystals on Si substrate

- selective growth of Germanium on Si Growth of Ge layers on silicon oxide trenches

Figure 1.4 – Silicon Photonics in Optical data

Laser integration could be counted as challenges of silicon photonics because of alignment of laser structure and wave guides, CW operation at desired wave length, Key Enabling technology for integrated multi-lambda sources, up to 10mW coupled power. Next section will be a brief introduction about the basics of a laser source as main part of the silicon photonics.

#### <u>Laser</u>

#### Overview

Lasers are devices that produce intense beams of light which are *monochromatic*, *coherent*, and *highly collimated*. The wavelength (color) of laser light is extremely pure (monochromatic) when compared to other sources of light, and all the photons (energy) that make up the laser beam have a fixed phase relationship (coherence) with respect to one another [8]. Light from a laser typically has very low divergence. It can travel over great distances or can be focused to a very small spot with a brightness which exceeds that of the sun. Because of these properties, lasers are used in a wide variety of applications in all walks of life. The term "laser" is an acronym for (L)ight (A)mplification by (S)timulated (E)mission of (R)adiation. To understand the laser, one needs to understand the meaning of these terms. The term "light "is generally accepted to be electromagnetic radiation ranging from 1 nm to 1000 mm in wavelength. The visible spectrum (what we see) ranges from approximately 400 to 700 nm. The wavelength range from 700 nm to 10 mm is considered the near infrared (NIR), and anything beyond that is the far infrared (FIR). Conversely, 200 to 400 nm is called ultraviolet (UV); below 200 nm is the deep ultraviolet (DUV).

#### PHOTONS AND ENERGY

Light is made up of particles called "photons" which exhibit both particle-like and wave-like properties. Each photon has an intrinsic energy determined by the equation:

$$E = h\nu \qquad (1)$$

Where vthe frequency of the light and h is is Planck's constant. Since, for a wave, the frequency and wavelength are related by the equation:

$$\lambda v = c$$

(2)

Where  $\lambda$  the wavelength of the light and c is the speed of light in a vacuum, equation 1 can be rewritten as:

$$E = \frac{hc}{\lambda} \quad (3)$$

It is evident from this equation that the longer the wavelength of the light, the lower the energy of the photon; consequently, ultraviolet light is much more "energetic" than infrared light.

Returning to the Bohr atom: for an atom to absorb light (i.e., for the light energy to cause an electron to move from a lower energy state  $E_n$  to a higher energy state  $E_m$ ), the energy of a single photon must equal, almost exactly, the energy difference between the two states. Too much energy or too little energy and the photon will not be absorbed. Consequently, the wavelength of that photon must be:

$$\lambda = \frac{hc}{\Delta E} \ (4)$$

Where

$$\Delta E = E_m - E_n (5)$$

Likewise, when an electron decays to a lower energy level in a radiative transition, the photon of light given off by the atom must also have an energy equal to the energy difference between the two states.

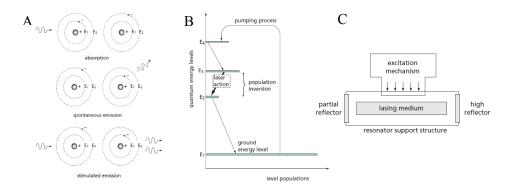

#### SPONTANEOUS AND STIMULATED EMISSION

In general, when an electron is in an excited energy state, it must eventually decay to a lower level, giving off a photon of radiation. This event is called "spontaneous emission," and the photon is emitted in a random direction and a random phase. The average time it takes for the electron to decay is called the time constant for spontaneous emission. On the other hand, if an electron is in energy state E2, and its decay path is to E1, but, before it has a chance to spontaneously decay, a photon happens to pass by whose energy is approximately  $E_2-E_1$ , there is a probability that the passing photon will cause the electron to decay in such a manner that a photon is emitted at exactly the same wavelength, in exactly the same direction, and with exactly the same phase as the passing photon. This process is called "stimulated emission." Absorption, spontaneous emission, and stimulated emission are illustrated in Figure 1.5. in any real population of atoms, the probability for stimulated emission is quite small.

Furthermore, not all of the atoms are usually in an excited state; in fact, the opposite is true. Boltzmann's principle, a fundamental law of thermodynamics, states that, when a collection of atoms is at thermal equilibrium, the relative population of any two energy levels is given by:

$$\frac{N2}{N1} = \exp(-\frac{E_2 - E_1}{kT})$$

Where N2 and N1 are the populations of the upper and lower energy states, respectively, T is the equilibrium temperature, and k is Boltzmann's constant. Substituting hv for E2 - E1 yields:

$$\Delta N = N_1 - N_2 = \left(1 - e^{-\frac{h\nu}{kT}}\right) N_1$$

For a normal population of atoms, there will always be more atoms in the lower energy levels than in the upper ones. Since the probability for an individual atom to absorb a photon is the same as the probability for an excited atom to emit a photon via stimulated emission, the collection of real atoms will be a net absorber, not a net emitter, and amplification will not be possible. Consequently, to make a laser, we have to create a "population inversion."

#### **POPULATION INVERSION**

Atomic energy states are much more complex than indicated by the description above. There are many more energy levels, and each one has its own time constants for decay. The four-level energy diagram shown in Figure 1.6 is representative of some real lasers. The electron is pumped (excited) into an upper level E4 by some mechanism (for example, a collision with another atom or absorption of high-energy radiation). It then decays to E3, then to E2, and finally to the ground state E1. Let us assume that the time it takes to decay from E2 to E1 is much longer than the time it takes to decay from E2 to E1. In a large population of such atoms, at equilibrium and with a continuous pumping process, a population inversion will occur between the E3 and E2 energy states, and a photon entering the population will be amplified coherently.

#### THE RESONATOR

Although with a population inversion we can amplify a signal via stimulated emission, the overall single-pass gain is quite small, and most of the excited atoms in the population emit spontaneously and do not contribute to the overall output. To turn this system into a laser, we need a positive feedback mechanism that will cause most of the atoms in the population to

contribute to the coherent output. This is the resonator, a system of mirrors that reflects undesirable (off-axis) photons out of the system and reflects the desirable (on-axis) photons back into the excited population where they can continue to be amplified.

Now consider the laser system shown in Figure 1.6. The lasing medium is pumped continuously to create a population inversion at the lasing wavelength. As the excited atoms start to decay, they emit photons spontaneously in all directions. Some of the photons travel along the axis of the lasing medium, but most of the photons are directed out the sides. The photons traveling along the axis have an opportunity to stimulate atoms they encounter to emit photons, but the ones radiating out the sides do not. Furthermore, the photons traveling parallel to the axis will be reflected back into the lasing medium and given the opportunity to stimulate more excited atoms. As the on-axis photons are reflected back and forth interacting with more and more atoms, spontaneous emission decreases, stimulated emission along the axis predominates, and we have a laser.

Figure 1.5 - (A) Spontaneous and stimulated emission (B) A four-level laser pumping system (C)

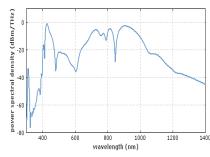

#### Laser spectrum

The optical spectrum (or *emission spectrum*) of a light source or some beam contains information on how the optical energy or power is distributed over different wavelengths. Usually, it is presented in the form of a diagram where the power spectral density (not necessarily with an absolute calibration) is plotted as a function of the wavelength or optical frequency. As an example, Figure 1.6 shows the numerically simulated optical spectrum of a supercontinuum source. In contrast to that very broad spectrum, the optical spectrum of a single-frequency laser source is often characterized by a very narrow line – in extreme cases, with a linewidth of the order of 1 Hz, corresponding to only  $\approx 3 \cdot 10^{-12}$  nm (for 1 µm center

wavelength). Other lasers have a spectrum consisting of multiple lines, and some (particularly mode-locked lasers for ultrashort pulses) can have a large spectral width of 100 nm or more with a frequency comb structure.

Optical spectra can be recorded with different types of spectrometers, which greatly differ in terms of the covered spectral range and the spectral resolution.

The optical spectrum is intimately related to the temporal coherence properties of the light. For example, the

Figure 1.6 - Example of a Laser

to the Fourier transform of the electric field, although the latter is in most cases not directly accessible. Therefore, it is also called the *Fourier spectrum* of the optical field.

The optical <u>bandwidth</u> is essentially the width of the optical spectrum. There are different definitions, but the full width at half maximum (FWHM) is often used.

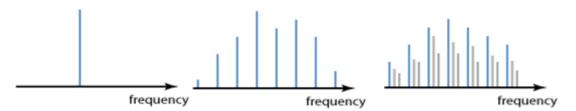

#### Single-Mode vs. Multi-Mode Laser

The term *single-mode operation*, which usually applies to <u>lasers</u>, is ambiguous, as it is used with different meanings:

- It can mean *single-transverse-mode operation*, where a laser operates on a single kind of *transverse* resonator mode, which is almost always a Gaussian mode (although operation on a single higher-order mode is also possible, e.g. by using some diffractive element in the laser resonator). If operation indeed occurs in a Gaussian mode, the laser's beam quality is diffraction-limited. However, laser oscillation may then still occur on multiple *axial* (longitudinal) modes, which have essentially the same transverse shape but differing optical frequencies, separated by the free spectral range.

- In other cases, the term really indicates operation on a single resonator mode, which is then also usually an axial (Gaussian) mode. This is more precisely called *single-longitudinal-mode operation* or *single-frequency operation*. In that case, the laser is a single-frequency laser, and the laser linewidth is fairly small (*-narrow-linewidth lasers*).

The number and type of oscillating resonator modes in a laser depends on the circumstances:

- The excitation of higher-order transverse modes can often be avoided by pumping only the volume covered by the axial modes. This is often done e.g. in end-pumped solid-state lasers.

- Multiple axial modes may still be excited, if the gain bandwidth is larger than the axial mode spacing (as is the case in most solid-state lasers). This may be changed by decreasing the gain bandwidth, by inserting an intracavity filter (e.g. an etalon), or by increasing the axial mode spacing (free spectral range), i.e. by using a very short laser resonator.

Single-frequency operation is usually more difficult to achieve than just single-transverse-mode operation, because it is not sufficient to introduce spatially varying loss or gain. Factors which make it more challenging are all those reducing the <u>mode competition</u>, e.g. <u>inhomogeneous</u> <u>saturation</u> via <u>spatial hole burning</u>.

Figure 1.7 - Emission spectra of lasers with single-mode emission (top), multiple axial mode (but single transverse mode) emission (middle), and full multimode emission (bottom).

# **Key Optical Components**

#### **Overview**

In this section, we would like to describe the basic optical components used in in an optical transmission system. An exemplary optical network identifying the key optical components shown in Figure 1.8 [9]. The end-to-end optical transmission involves both electrical and optical signal paths. To perform conversion from electrical to optical domain, the optical transmitters are used, while to perform conversion in opposite direction (optical to electrical conversion), the optical receivers are used. The optical fibers serve as foundation of an optical transmission system because the optical fiber is used as a medium to transport the optical signals from source to destination. The optical fibers attenuate the signal during transmission, and someone has to use optical amplifiers, such as erbium-doped fiber amplifiers (EDFAs), Raman amplifiers, or parametric amplifiers, to restore the signal quality. However, the process of amplification is accompanied with noise addition. The simplest optical transmission system employs only one wavelength. The wavelength division multiplexing (WDM) can be considered as an upgrade of the single-wavelength system.

During transmission of WDM signals, occasionally one or several wavelengths are to be added or dropped, which is performed by the optical component known as optical add–drop multiplexer (OADM). To combine several distinct wavelength channels into composite channel, the wavelength multiplexers are used. On the other hand, to split the composite WDM channel into distinct wavelength channels, the wavelength demultiplexers are used. To impose the information signal, optical modulators are used. The optical modulators are commonly used in combination with semiconductor lasers.

Figure 1.8 - An exemplary optical network identifying key optical components

#### **Interconnection**

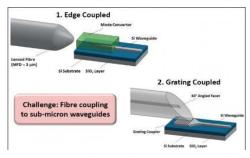

c)Grating coupler and Edge Coupler Materials with a high refractive index contrast are useful for high-density photonic integrated circuits. The basic building blocks of those circuits are nanophotonic waveguides such as photonic-crystal or photonic-wire waveguides. Examples of materials with a high refractive index contrast are silicon-on-insulator (SOI) or indium phosphide (InP) membranes with an air cladding [10]. However, a difficulty is coupling light between optical fibers and integrated waveguides. Because the waveguide core layer is only 100 - 300 nm thick

Figure 1.11 – Edge coupler vs. Grating Coupler

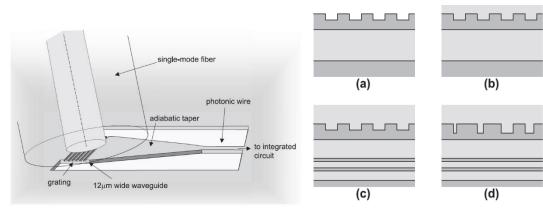

and the guided mode is strongly confined in that core, there is a large mismatch between the waveguide mode and a single-mode fiber mode. This coupling problem is important and several groups have recently demonstrated1,2) coupling losses below 1 dB using an inverted lateral taper with a polymer overlay. Although this is a very elegant solution to the coupling problem, it may be beneficial to have a surface coupler that can be placed anywhere on a chip, not only at the edges. Such a coupler does not require polishing of facets and allows wafer-scale testing of photonic integrated circuits because light can be coupled in and out of the surface of the chip. Waveguide grating couplers are suitable for this task. The grating coupler can be fabricated using one additional lithography and etching step. Standard single-mode fibers and fiber arrays can be used for the packaging. The grating, which couples light from an out-of-plane fiber into a planar waveguide, is followed by an in-plane taper to couple to a single-mode photonic wire waveguide. The grating coupler can be shown schematically according to Figure 1.9.

Figure 1. 9 - principle of grating coupler for coupling

Figure 1.10 - Schematic drawing of different types of couplers: Uniform grating in (a) SOI with air top cladding, (b) SOI with oxide top cladding, (c) SOI

With bottom Si/SiO2 mirror, (d) a grating coupler with varying groove widths is shown. Dark gray represents Si and light gray SiO2.

As shown in Figure 1.10, the difference among the grating coupler and edge coupler is obvious. In grating coupler, the fiber with a certain angle is approaching to the grating coupler and coupling is happening. However, in edge coupler lensed fiber is in the same level as wave guide and in sub-micron distance without any angle coupling is performed.

#### d) Waveguide

An optical waveguide is a spatially inhomogeneous structure for guiding light, i.e. for restricting the spatial region in which light can propagate. Usually, a waveguide contains a region of increased refractive index, compared with the surrounding medium (called cladding) [11]. However, guidance is also possible, e.g., using reflections, e.g. at metallic interfaces. Some waveguides also involve plasmonic effects at metals.

The applications of waveguides are manifold. Some examples are:

- Optical fibers allow the transmission of light over long distances, e.g. for optical fiber communications.

- On *photonic integrated circuits*, as used e.g. in *silicon photonics*, waveguides guide light between different optical components.

- In the future, silicon waveguides on digital processor chips and polymer waveguides in circuit boards may be used for fast optical data transmission between components of computers.

- Some waveguides are used for maintaining high optical intensities over appreciable lengths, e.g. in nonlinear devices [12] [13] such as frequency doublers and Raman lasers. Active (amplifying) waveguides are used in waveguide lasers and amplifiers. Important examples are fiber lasers and fiber amplifiers.

- A waveguide can be used for stripping off higher-order transverse modes, thus acting as a *mode cleaner*.

- In some cases, an interaction of the guided light with material in the evanescent field is used, e.g. in certain *waveguide sensors*.

- Waveguides can also be employed for splitting and combining light beams, e.g. in integrated optical interferometers.

Figure 1.12 - Wave guide schematics in photonic devices

Figure 1.13 - Electric field amplitude profiles for all the

Waveguide structures are spatially inhomogeneous structures which can guide waves. For light propagating in a waveguide, the self-consistency condition for a mode is stricter than for free-space modes: the shape of the complex amplitude profile in the transverse dimensions must remain exactly constant. Any re-scaling is not allowed, only an overall phase change and a loss or gain of total optical power, which are both described by the *propagation constant*.

A waveguide has only a finite number of *guided propagation modes*, the intensity distributions of which have a finite extent around the waveguide core. The number of guided modes, their transverse amplitude profiles and their propagation constants depend on the details of the waveguide structure and on the optical frequency. A single-mode waveguide (e.g. a single-mode fiber) has only a single guided mode per polarization direction. As an example of a multimode waveguide, Figure 1.12 shows the transverse profiles of all the LP modes of a multimode fiber.

A waveguide also has *cladding modes*, the intensity distributions of which essentially fill the whole cladding (and core) region. Optical fibers (even single-mode fibers) have a large number of cladding modes, which often exhibit substantial propagation losses at the outer interface of the cladding.

Optical fibers (except for photonic crystal fibers) usually have a radially symmetric refractive index profile and also a relatively small refractive index contrast between core and cladding. In that case, one can quite accurately describes the mode as LP modes, which are mathematically simpler to describe and are therefore usually used in practice.

For radially symmetric refractive index profiles, there is also the interesting phenomenon of *orbital angular momentum modes* [12] [13]. Those carry an angular momentum which is *not* related to the photon spin, also not to a rotating polarization direction. The wave fronts exhibit a helical structure. This is possible only for modes having zero intensity at the beam center – for example, LP modes with non-zero l.

Modes of fiber and other waveguides can be numerically calculated numerically with so-called *mode solvers*, which can be part of a fiber simulation software. Depending on whether the waveguides have radially symmetric profiles and are weakly guiding, mode solver algorithms with a different level of complexity and quite different computation times are required. A mode solver for optical fibers, when restricted to pure LP modes, can be numerically much simpler and faster than a general 2D mode solver.

#### Transmitter

#### e) Overview

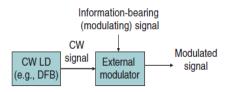

For high-speed communication (10 GBit/s and beyond) it becomes extremely difficult to modulate the laser directly, therefore external optical modulators are used. The electro absorption modulator is such a modulator [9]. It can be understood as a reverse-biased PIN detector. Although it improves the chirp performance considerably compared to direct modulation of the laser, there is still enough chirp to make long haul high speed transmission impossible. More importantly, the modulator chirp is dynamic and changes with the actual drive voltage. Here we briefly describe the main modulation methods which contains MZI, EAM and finally RRM method.

#### f) Mach-Zender Modulators (MZM)

The optical signal generated by semiconductor laser has to be modulated by information signal before being transmitted over the optical fiber [14]. This can be achieved by directly modulating the bias current of semiconductor laser, which can be done even at high speed (even up to 40 Gb/s in certain lasers). Unfortunately, this concept although conceptually simple is

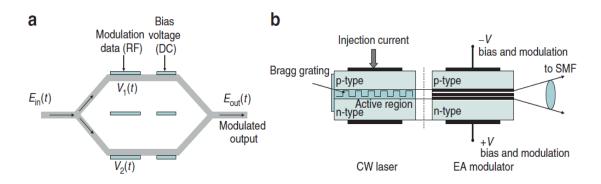

rarely used in practice because of the frequency chirp introduced by direct modulation, nonuniform frequency response, and large current swing needed to provide operation. For transmitters operating at 10 Gb/s and above, instead, the semiconductor laser diode (LD) is commonly biased at constant current to provide continuous wave (CW) output, and external modulators are used to impose the information signal to be transmitted. The most popular modulators are electro-optic optical modulators, such as Mach–Zehnder modulators, and electro absorption modulators [9] [15]. The principle of the external modulator is illustrated in Figure 1.15(A). Through the external modulation process, a certain parameter of the CW signal, used as a signal carrier, is varied in accordance with the information-bearing signal

There are two types of external modulators commonly used in practice: Mach– Zehnder modulator (MZM) and electro absorption modulator (EAM), whose operational principle is illustrated in Figure 1.15. The MZM is based on electro-optic effect, the effect that in certain materials (such as LiNbO3) where the refractive index n changes with respect to the voltage V applied across electrodes:

$$\Delta n = -\frac{1}{2} \Gamma n^3 r_{33}(\frac{V}{d_e}) \implies \Delta \varphi = \frac{2\pi}{\lambda} \Delta n L$$

Where  $\Delta n$  denotes the refractive index change,  $\Delta \varphi$  is corresponding phase change,  $r_{33}$  is the electro-optic coefficient, d<sub>e</sub> is separation of electrode length, and  $\lambda$  is the wavelength the light. The MZM (see Fig. 1.15(A)) is a planar waveguide structure deposited on the substrate, with two pairs of electrodes (1) for high-speed ac voltage representing the modulation data (RF) signal and (2) for dc bias voltage. Let V1.t / and V2.t / denote the electrical drive signals on the upper and lower electrodes, respectively. The output electrical field Eout.t / of the second Y-branch can be related to the input electrical field Ein by:

$$E_{out}(t) = \frac{1}{2} \left[ \exp\left(j \frac{\pi}{V_{\pi}} V_1(t)\right) + \exp\left(j \frac{\pi}{V_{\pi}} V_2(t)\right) \right] E_{in}$$

Where  $V_{\pi}$  is differential drive voltage. V1 -V2 =  $V_{\pi}$  resulting in differential phase shift of  $\pi$  rad between two waveguides. Possible modulation formats that can be used with this MZM include: on–off keying (OOK) with zero/nonzero chirp, binary phase-shift keying (BPSK), differential phase-shift keying (DPSK), quadrature phase-shift keying (QPSK), differential QPSK (DQPSK), and return-to-zero (RZ) with duty cycle 33%, 50%, or 67.

The electro absorption modulator (EAM) is a semiconductor-based planar waveguide composed of multiple p-type and n-type layers that form multiple quantum wells (MQWs). The basic design of EAM is similar to that of semiconductor lasers. The MQW is used to support the quantum-confined Stark effect (the absorption spectrum being a function of applied field) more effectively. Because of similarities of EAMs and semiconductor lasers design it is possible to fabricate them on the same substrate (see Figure 1.15 (B)), providing that EAM and laser are electrically isolated. Bandgap of quantum wells is larger than photon energy, so that the light is completely transmitted in the absence of bias, which corresponds to the ON state. When the reverse bias is applied the input signal is absorbed, which corresponds to the OFF state. The modulation speed of EAMs is typically comparable to the modulation speed of MZMs. However, the extinction ratio (the ratio of average powers corresponding to symbol 1 and symbol 0) is lower.

#### g) Electro Absorption Modulators (EAM)

An electro absorption modulator (or electro-absorption modulator) is a semiconductor device which can be used for controlling (modulating) the intensity of a laser beam via an electric voltage *—optical modulators*) [15] [9]. Its principle of operation is based on the *Franz–Meldish effect* [1, 2], i.e., a change in the absorption spectrum caused by an applied electric field, which changes the bandgap energy (thus the photon energy of an absorption edge) but usually does not involve the excitation of carriers by the electric field. Most electro absorption modulators are made in the form of a waveguide with electrodes for applying an electric field in a direction perpendicular to the modulated light beam. For achieving a high extinction ratio, one usually exploits the quantum-confined Stark effect in a quantum well structure.

Compared with electro-optic modulators, electro absorption modulators can operate with much lower voltages (a few volts instead of hundreds of thousands of volts). They can be operated at very high speed; a modulation bandwidth of tens of gigahertz can be achieved, which makes these devices useful for optical fiber communications [15] [9]. A convenient feature is that an electro absorption modulator can be integrated with a distributed feedback laser diode on a single chip to form a data transmitter in the form of a photonic integrated circuit. Compared with direct modulation of the laser diode, a higher bandwidth and reduced chip can be obtained.

Figure 1.14 – An illustration of external modulation principle. DFB distributed

Figure 1.15 – (a) Mach–Zehnder modulator (b) Electro Absorption Modulator

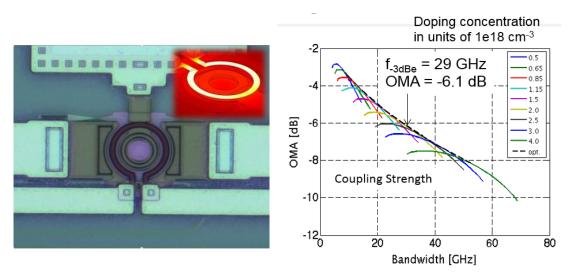

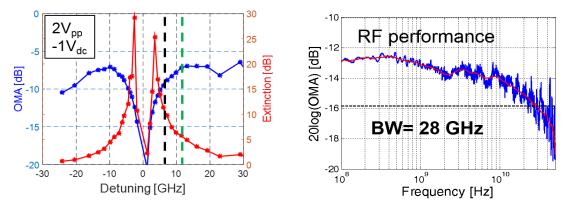

#### h) Ring Resonator Modulators (RRM)

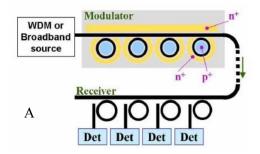

The silicon modulator is a key component for CMOS-compatible optical interconnection systems. Recently, high-speed modulators based on free-carrier plasma dispersion effect have been demonstrated using either Mach-Zehnder interferometers (MZI) or micro-ring resonators in silicon and III-V materials [16]. Comparing to the mm-long MZI-based modulators, the advantages of the ring-resonator-based modulator include its small size (~10µm) and low-power consumption. In the ring resonator, in contrast to single-pass devices like MZI, light at the resonant wavelength travels many round trips in the resonator, and interacts with the carriers many times. As a result, the total number of carriers needed to change the optical transmission of the ring resonator is much less than that needed in MZI-modulators, and therefore much less RF power is needed to drive these carriers in and out of the active region.

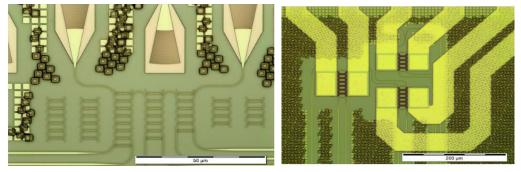

The key components of the WDM interconnection system are the cascaded modulators shown in the shadowed area of Figure 1.16, which are fabricated on a SOI substrate. The device structure is based on the micro-ring modulator we presented inn next sections. They consist of ring resonators embedded with PIN junctions used to inject and extract free carriers, which in turn modify the refractive index of the silicon and the resonant wavelength of the ring resonator using the mechanism of the plasma dispersion effect. The waveguides and rings are formed by silicon strips with the height of 200 nm and the width of 450 nm on top of a 50-nm-thick slab layer. The speed of the modulator was limited to 400 Mbps under non-return-to-zero (NRZ) coding. The reason for this limitation is that the p-i-n junction is formed on only part of the ring resonator, while carriers diffuse into the section of the ring that is not part of the p-i-n junction, where they cannot be efficiently extracted during the reverse biased period, leading to a longer fall time following consecutive '1's.

Figure 1.16 - Schematics of a WDM optical interconnection system with cascaded silicon ring resonators as a WDM modulator and demultiplexer. Det: detector.

Figure 1.17- Top-view microscopic picture of the fabricated modulators, showing two of the four ring modulators coupled to a straight waveguide.

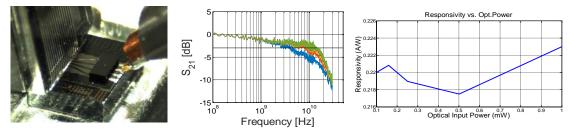

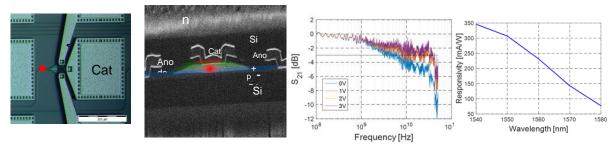

#### **Receiver**

#### *i)* OVERVIEW

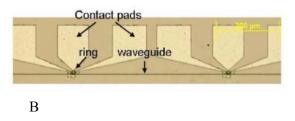

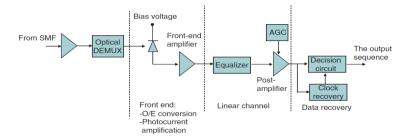

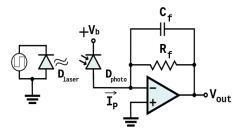

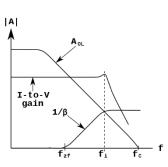

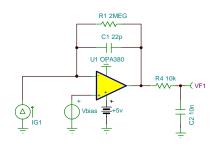

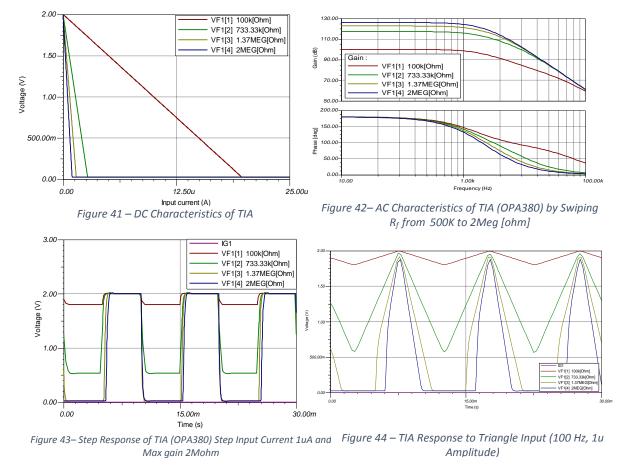

The purpose of the optical receiver is to convert the optical signal into electrical domain and to recover the transmitted data. The typical OOK receiver configuration is already given in Figure 1.18. We can identify three different stages: front-end stage, the linear channel stage, and data recovery stage [9]. The front-end stage is composed of a photodetector and a preamplifier. The most commonly used front-end stages are high-impedance front-end and transimpedance front-end, both shown in Figure 1.18. High-impedance front end employs a large value load resistance to reduce the level of thermal noise and has a good receiver sensitivity. However, the bandwidth of this scheme is low because the RC constant is large. To achieve both the high receiver sensitivity and large bandwidth, the transimpedance front-end scheme, shown in Figure 1.16 is used. Even though the load resistance is high, the negative feedback reduces the effective input resistance by a factor of G - 1, where G is the front-end amplifier gain. The bandwidth is increased for the same factor compared to high-impedance front-end scheme.

The photodiode is an integral part of both front-end stage schemes [9]. The key role of the photodiode is to absorb photons in incoming optical signal and convert them back to the

Figure 1.18 - Optical receiver front-end stage schemes (A) high-impedance front-end (B) trans impedance front-end

electrical level through the process opposite to the one taking place in semiconductor lasers.

The incoming optical signal may be preamplified by an optical amplifier and further processed by an optical filter to reduce the level of amplified spontaneous emission (ASE) noise or by wavelength demultiplexer to select a desired wavelength channel. The optical signal is converted into electrical domain by using a photodetector, followed by an electrical post amplifier. The clock recovery circuit is most commonly implemented using the phase-lock loop (PLL). Finally, the purpose of decision circuit is to provide the binary sequence being transmitted by comparing the sampled signal to a predetermined threshold. Whenever the received sample is larger than the threshold, the decision circuit decides in favor of bit 1, otherwise in favor of bit 0

Figure 1.19 – A typical direct detection architecture. O/E optical to electrical and AGC

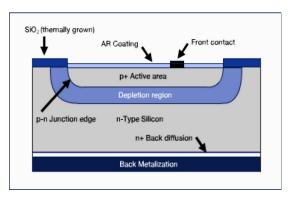

A silicon photodiode is a solid-state device which converts incident light into an electric current. It consists of a shallow diffused p-n junction, normally a p-on-n configuration although "P-type" devices (n-on-p) are available for enhanced responsivity in the 1 $\mu$ m region [17]. Modern day silicon [18]photodiodes are generally made by planar diffusion or ion-implantation methods. In the p-on-n planar diffused configuration, shown in the Figure 1.20, the junction edge emerges on the top surface of the silicon chip, where it is passivated by a thermally grown oxide layer.

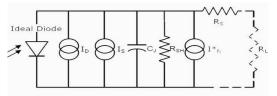

The equivalent circuit of a photodiode is shown in the Figure 1.20. The photodiode behaves as a current source when illuminated. When operated without bias, this current is distributed between the internal shunt resistance and external load resistor. In this mode, a voltage develops which creates a forward bias, thus reducing its ability to remain a constant current source. When operated with a reverse voltage bias, the photodiode becomes an ideal current source. Parameters of shown equivalent circuit of photodiode in Figure 1.20 can be defined according to table 1.2.

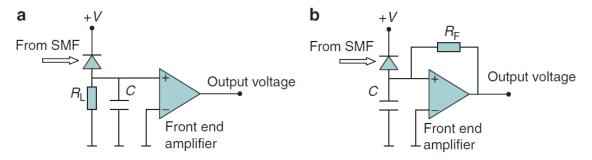

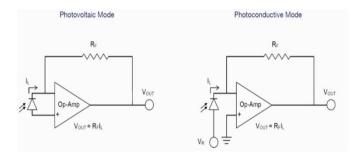

A silicon photodiode can be operated in either the photovoltaic or photoconductive mode. In the photovoltaic mode, the photodiode is unbiased; while for the photoconductive mode, an external reverse bias is applied. Mode selection depends upon the speed requirements of the application, and the amount of dark current that is tolerable. In the photovoltaic mode, dark current is at a minimum. Photodiodes exhibit their fastest switching speeds when operated in the photoconductive mode. Photodiodes and Op-Amps can be coupled such that the photodiode operates in a short circuit current mode. The op-amp functions as a simple current to voltage converter, these structures are shown in Figure 1.22.

Figure 1.20- Cross section view a Photodiode

Figure 1.21 – Equivalent circuit of photodiode

| Parameters | Description                                                  | Unit      |

|------------|--------------------------------------------------------------|-----------|

| Id         | Dark current                                                 | Amps      |

| Is         | Light Signal<br>Current (Is=RPo)                             | Amps      |

| R          | Photodiode<br>responsivity at<br>wavelength of<br>irradiance | Amps/Watt |

| Ро         | Light power<br>incident on<br>photodiode active<br>area      | Watts     |

| Rsh        | Shunt Resistance                                             | Ohms      |

| In         | Noise Current                                                | Amps rms  |

| С          | Junction<br>Capacitance                                      | Farads    |

| Rs         | Series Resistance                                            | Ohms      |

| RL         | Load Resistance                                              | Ohms      |

Table 1.2 - PD equivalent circuit Parameters

Figure 1.22 – Conversion circuits of PD Current to Voltage

# **Optical Amplification**

### Overview

An optical amplifier is a device which receives some input signal and generates an output signal with higher optical power. Typically, inputs and outputs are laser beams, either propagating as Gaussian beams in free space or in a fiber. The amplification occurs in a so-called gain medium, which has to be "pumped" (i.e., provided with energy) from an external source. Most optical amplifiers are either optically or electrically pumped [18].

Important parameters of an optical amplifier include:

- the maximum gain, specified as an amplification factor or in decibels (dB)

- the saturation power, which is related to the gain efficiency

- the saturated output power (for a given pump power)

- the power efficiency and pump power requirements

- the saturation energy

- the time of energy storage (*—upper-state lifetime*)

- the gain bandwidth (and possibly smoothness of gain spectrum)

- the noise figure and possibly more detailed noise specifications

- the sensitivity to back-reflections

- the number of modes it can amplify

Different kinds of amplifiers differ very much e.g. in terms of saturation properties. For example, rare-earth-doped gain media can store substantial amounts of energy, whereas optical parametric amplifiers provide amplification only as long as the pump beam is present. As another example, semiconductor optical amplifiers store much less energy than fiber amplifiers, and this has important implications for optical fiber communications.

### EDFA

Erbium-doped fiber amplifiers are the by far most important fiber amplifiers in the context of long-range optical fiber communications; they can efficiently amplify light in the 1.5-nm wavelength region, where telecom fibers have their loss minimum.

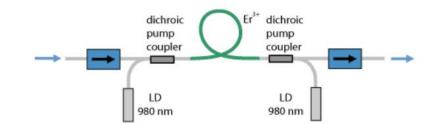

A typical setup of a simple erbium-doped fiber amplifier (EDFA) is shown in Figure 1.23. Its core is the erbium-doped optical fiber, which is typically a single-mode fiber. In the shown case, the *active fiber* is "pumped" with light from two laser diodes (bidirectional pumping), although unidirectional pumping in the forward or backward direction (co-directional and counter-directional pumping) is also very common. The pump light, which most often has a wavelength around 980 nm and sometimes around 1450 nm, excites the erbium ions ( $Er^{3+}$ ) into the <sup>4</sup>I<sub>13/2</sub> state (in the case of 980-nm pumping via <sup>4</sup>I<sub>11/2</sub>), from where they can amplify light in the 1.5-nm wavelength region via stimulated emission back to the ground-state manifold <sup>4</sup>I<sub>15/2</sub>.

Figure 1.23 - Schematic setup of a simple erbium-doped fiber amplifier. Two laser diodes (LDs) provide the pump power for the erbium-doped fiber. The pump light is injected via dichroic fiber couplers. Pig-tailed optical isolators reduce the sensitivity of the device to back-reflections.

The setup shown also contains two "pig-tailed" (fiber-coupled) optical isolators. The isolator at the input prevents light originating from <u>amplified spontaneous emission</u> from disturbing any previous stages, whereas that at the output suppresses lasing (or possibly even destruction) if output light is reflected back to the amplifier. Without isolators, fiber amplifiers can be sensitive to back-reflections.

Apart from optical isolators, various other components can be contained in a commercial fiber amplifier. For example, there can be <u>fiber couplers</u> and <u>photodetectors</u> for monitoring <u>optical</u> <u>power</u> levels, pump <u>laser diodes</u> with control electronics and <u>gain-flattening filters</u>. For particularly compact packages, various passive optical components can be combined into a <u>photonic integrated circuit</u> (*planar light wave circuit*).

Very high signal gains, as used, e.g., for the amplification of <u>ultrashort pulses</u> to high energies, are usually realized with <u>amplifier chains</u>, consisting of several amplifier stages with additional optical elements (e.g. isolators, <u>filters</u>, or modulators) in between.

EDFAs can serve various functions in systems for <u>optical fiber communications</u>; the most important applications are the following:

- The power of a data transmitter may be boosted with a high-power EDFA before entering a long fiber span, or a device with large losses, such as a <u>fiber-optic splitter</u>. Such splitters are widely used e.g. in cable-TV systems, where a single transmitter is used to deliver signals into many fibers.

- A fiber amplifier may also be used in front of a data receiver, if the arriving signal is weak. Despite the introduction of <u>amplifier noise</u>, this can improve the <u>signal-to-noise</u> <u>ratio</u> and thus the possible data transmission rate, since the amplifier noise may be weaker than the input noise of the receiver. It is more common, however, to use <u>avalanche photodiodes</u>, which have some built-in signal amplification.

- In-line EDFAs are used between long spans of passive transmission fiber. Using multiple amplifiers in a long <u>fiber-optic link</u> has the advantage that large transmission losses can be compensated without (a) letting the <u>optical power</u> drop to too low levels, which would spoil the signal-to-noise ratio, and (b) without transmitting excessive optical powers at other locations, which would cause detrimental nonlinear effects due to the unavoidable fiber <u>nonlinearities</u>. Many of these in-line EDFAs are operated even under difficult conditions, e.g. on the ocean floor, where maintenance would be hardly possible.

- Although data transmitters are normally not based on erbium-doped devices, EDFAs are often part of equipment for testing transmission hardware. They are also used in the context of optical signal processing.

These functions can be realized in the telecom C and L bands. Other types of fiber amplifiers, e.g. based on praseodymium, have been considered for other bands, but none can compete with erbium-based devices in terms of gain and gain efficiency.

A particular attraction of EDFAs is their large <u>gain bandwidth</u>, which is typically tens of nanometers and thus actually more than enough to amplify data channels with the highest data rates without introducing any effects of gain narrowing. A single EDFA may be used for simultaneously amplifying many data channels at different wavelengths within the gain region; this technique is called <u>wavelength division multiplexing</u>. Before such fiber amplifiers were available, there was no practical method for amplifying all channels e.g. between long fiber spans of a fiber-optic link: one had to separate all data channels, detect and amplify them electronically, optically resubmit and again combine them. The introduction of fiber amplifiers thus brought an enormous reduction in the complexity, along with a corresponding increase in reliability. Very long lifetimes are possible by using redundant down-rated pump diodes.

The only competitors to erbium-doped fiber amplifiers in the 1.5-µm region are <u>Raman</u> <u>amplifiers</u>, which profit from the development of higher power pump lasers. Raman amplification can also be done in the transmission fiber. Nevertheless, EDFAs remain very dominant.

#### SOA

A semiconductor optical amplifier is an optical amplifier based on a semiconductor gain medium. It is essentially like a laser diode where the end mirrors have been replaced with anti-reflection coatings; a tilted waveguide can be used to further reduce the end reflectivity's. The signal light is usually sent through a semiconductor single-mode waveguide with transverse dimensions of e.g. 1-2 nm and a length of the order of 0.5-2 mm. The waveguide mode has significant overlap with the active (amplifying) region, which is pumped with an electric current [20] [21]. The injection current creates a certain carrier density in the conduction band, allowing for optical transitions from the conduction band to the valence band. The gain maximum occurs for photon energies slightly above the bandgap energy.

In principle, one can also use a semiconductor optical amplifier where the end reflectivity's are not minimized. One has to operate such a *Fabry–Pérot amplifier* (*FP amplifier*) slightly below the laser threshold; in that regime, the output power depends strongly on the input power, i.e., one obtains a high effective signal gain. However, the available optical <u>bandwidth</u> is then very small, and the occurrence of strong reflections may be detrimental to the system in which such a device is used. For these reasons, in most cases one uses traveling-wave amplifiers, where the end reflectivity's are suppressed as far as possible.

The amplification is intrinsically polarization-sensitive, but amplifier designs have been developed which provide nearly polarization-independent characteristics. For example, one may use two identical amplifiers in series, where the second one is rotated against the first one by 90°. There are also configurations with two parallel amplifiers for the two polarization directions, with polarizing beam splitters before and after these amplifiers. Another possibility is to use a double pass through a single amplifier, where there is a <u>Faraday rotator</u> between the device and the reflecting mirror.

SOAs can be used in telecom systems in the form of fiber-pigtailed components (with either normal single-mode fibers or polarization-maintaining fibers), operating at signal wavelengths near 1.3 um or 1.5 um, and offering a gain of up to 30 dB, limited essentially by amplified spontaneous emission (ASE). The strong gain saturation in SOAs can be a problem for some applications, but it can also be exploited for nonlinear signal processing in telecom systems – for example, for channel translation in a wavelength division multiplexing system.

The technology of semiconductor amplifiers competes with that of erbium-doped fiber amplifiers (EDFAs). The main differences compared with EDFAs are:

- The setup is much more compact, containing only a small semiconductor chip with electrical and fiber connections. A compact housing may even contain additional polarization-insensitive Faraday isolators at the input, output, or both ports.

- The output powers are substantially smaller, particularly when comparing with high-power fiber amplifiers.

- The required operation power is also smaller; typical drive currents a few hundred milliamperes.

- The gain bandwidth can be similar. Devices operating in different wavelength regions can be made.

- The upper-state lifetime and thus the stored energy are much smaller, so that the gain reacts to changes in pump power or signal power within nanoseconds (instead of milliseconds). Changes in gain also cause phase changes (*linewidth enhancement factor*).

- SOAs exhibit much stronger nonlinear distortions in the form of self-phase modulation and four-wave mixing. These are often unwanted, but can also be used e.g. for optical signal processing (see below).

- The noise figure is typically higher.

- The amplification is intrinsically polarization-dependent, as far as that is not avoided with special designs (see above).

# **Optical filters**

#### Overview

An optical filter is usually meant to be a component with a <u>wavelength</u>-dependent (actually frequency-dependent) transmission or reflectivity, although there are also filters where the dependence is on polarization or spatial distribution, or some uniform level of attenuation is provided [21]. Filters with particularly weak wavelength dependence of the transmittance are called <u>neutral density filters</u>.

There are many different types of optical filters, based on different physical principles. Some examples of optical filters are:

- Absorbing glass filters, dye filters, and color filters are based on wavelength-dependent absorption in some material such as a glass dopant, dye, pigment or semiconductor. As the absorbed light is converted into heat, such filters are usually not suitable for high-power optical radiation.

- Various kinds of optical filters are based on interference effects, combined with wavelength-dependent phase shifts during propagation. Such filters exhibit wavelength-dependent reflection and transmission, and the light which is filtered out can be sent to some beam dump, which can tolerate high optical powers. An important class of interference-based filters contains dielectric coatings. Such coatings are used in dielectric mirrors (including dichroic mirrors), but also in thin-film polarizers, and in polarizing and non-polarizing beam splitters. Via thin-film design it is possible to realize edge filters, low-pass, high-pass and band-pass filters, notch filters, etc. The same physical principle is used in fiber Bragg gratings and other optical Bragg gratings such as volume Bragg gratings. Apart from step-index structures, there are also gradient-index filters, called *rugate filters*. That approach allows one to make high-quality notch filters, for example.

- Fabry–Pérot interferometers, etalons and arrayed waveguide gratings are also based on interference effects, but typically exploiting larger path length differences. Therefore, they can have sharper spectral features.

- Lyot filters involve wavelength-dependent polarization changes. Similar devices are used as birefringent tuners in tunable lasers.

- Other filters are based on wavelength-dependent refraction in prisms (or prism pairs) or on wavelength-dependent diffraction at gratings, combined with an aperture.

- There are acousto-optic tunable filters, where it is exploited that Bragg reflection at an acoustic wave works only within a narrow frequency range.

Concerning the shape of the transmission curve, there are:

- bandpass filters, transmitting only a certain wavelength range

- notch filters, eliminating light of a certain wavelength range

- edge filters, transmitting only wavelengths above or below a certain value (*high-pass and low-pass filters*)

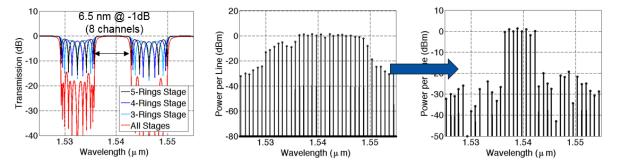

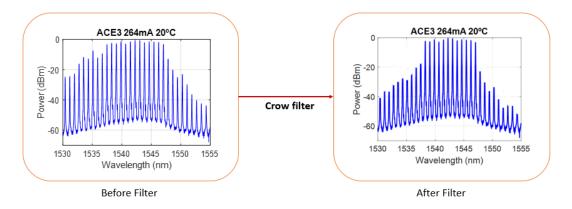

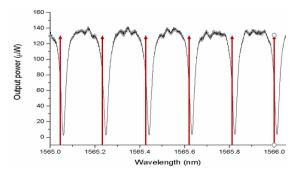

#### **Crow Filter**

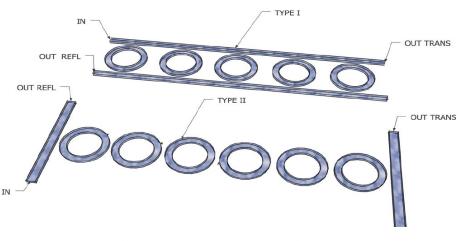

Coupled resonator optical waveguide devices (CROWs) are microscopic structures that are formed by cascading or putting in parallel a number of (micro) ring resonators (also called microcavities) - which are essentially waveguides shaped in the form of a ring - in a way that light can be coupled into the structure, resonates through the rings and is coupled out again at a different number of ports depending on the wavelength. Their basic functionality is that of an

Figure 1.24 - Schematic description of possible ring formations.

optical filter. Figure 1.24 shows two basic formations of how these rings can be put together. The structure above named Type I contains rings that aren't mutually coupled but coupled periodically to two parallel waveguides. Light can be inputted at the upper left of downright, and outputted at the down left or upright. This structure is comparable with a distributed feedback Filter. The second structure, Type II, shows and array of rings mutually coupled and connected at both ends to waveguide busses. Down left light can be put in, and extracted at the top-left or right-bottom. The direction in which the light is output at the right depends on the quantity of rings. This type of filter could be compared to a stack of reaction Bragg-mirrors or Fabry-Perot cavities. Because of the comparison with these types of filters with other already well-known Filter types, certain properties can be copied and applied those these filters. Take into account that a uniform shape of the ring resonators was assumed, this means all the rings have the same circumference.

# Multiplexer & De-Multiplexer

#### OADM

An **optical add-drop multiplexer** (**OADM**) is a device used in wavelength-division multiplexing systems for multiplexing and routing different channels of light into or out of a single mode fiber (SMF) [22]. This is a type of optical node, which is generally used for the formation and the construction of optical telecommunications networks. "Add" and "drop" here refer to the capability of the device to add one or more new wavelength channels to an existing multi-wavelength WDM signal, and/or to drop (remove) one or more channels, passing those signals to another network path. An OADM may be a specific type of optical cross-connect.

A traditional OADM consists of three stages: an optical demultiplexer, an optical multiplexer, and between them a method of reconfiguring the paths between the demultiplexer, the multiplexer and a set of ports for adding and dropping signals. The demultiplexer separates wavelengths in an input fiber onto ports. The reconfiguration can be achieved by a fiber patch panel or by optical switches which direct the wavelengths to the multiplexer or to drop ports. The multiplexer multiplexers the wavelength channels that are to continue on from demultiplexer ports with those from the add ports, onto a single output fiber.

All the light paths that directly pass an OADM are termed *cut-through lightpaths*, while those that are added or dropped at the OADM node are termed *added/dropped lightpaths*. An OADM with remotely reconfigurable optical switches (for example  $1 \times 2$ ) in the middle stage is called a reconfigurable OADM (ROADM). Ones without this feature are known as *fixed* OADMs. While the term OADM applies to both types, it is often used interchangeably with ROADM.

Physically, there are several ways to make an OADM. There are a variety of demultiplexer and multiplexer technologies including thin film filters, fiber Bragg gratings with optical circulators, free space grating devices and integrated planar arrayed waveguide gratings. The switching or reconfiguration functions range from the manual fiber patch panel to a variety of switching technologies including microelectromechanical systems (MEMS), liquid crystal and thermo-optic switches in planar waveguide circuits.

Although both have add/drop functionality, OADMs are distinct from add-drop multiplexers. The former function in the photonic domain under wavelength-division multiplexing, while the latter are implicitly considered to function in the traditional SONET/SDH networks.

Figure 1.25– Main Scheme of Optical Multiplexer and

# Motivation and goals of this project

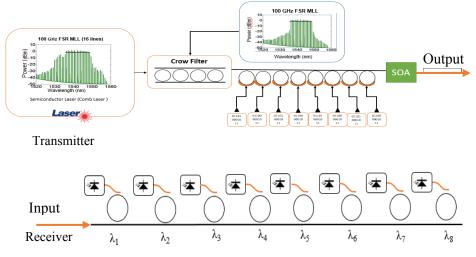

According to the defined project, we are dealing with an optical telecommunication system based on silicon photonic chips which is fabricated and mounted on a RF board as an interface of electrical and optical signals. This optical telecommunication system contains 8 optical transmitters, receivers and 3 filter which are related to the high frequency part of the system. Ideal performance of this system is modulation of the electrical signals to the optical signals by ring resonator modulators and transmitting data and then multiplexing the different channels by OADM and passing data through optical fibers. This modulated and multiplexed data will be amplified to be detected in receiver part of the high frequency system. By demultiplexing the modulated optical signal and detection by high frequency photodiodes, which convert optical signals to the electrical signals.

In an ideal situation, all the transmitted data should be received in the pair photodiode of the receiver. But in real world the wave length of the transmitter and receiver's ring resonators are not at the same wave length. Also, wavelengths of the ring resonators are not at the same and equal space from each other in wave length domain. To have equal space among the optical channels to avoid cross talk between the channels, and the same wave length of transmitter and receiver side we need an extra feedback control for controlling and tuning the wave length of the ring resonators which are in exposure of temperature fluctuation. Consequently, temperature fluctuation is affecting the wave length of the ring resonators by impact on refractive index of the material. Temperature fluctuation is caused by variation of the ambient temperature, power dissipation in the electronic circuits like delivers, applying data by data generator, etc.

Manipulation of the wave length in ring resonators are performed by fabrication of a micro heater on top of the ring resonators to change the temperature of the ring resonator which has effect in the refractive index of the material. By variation of the refractive index we will have shifting in the wave length of each ring resonator. This manipulation is observed by a low frequency photodiode which are coupled to wave guides and contain at most 3% of the light power inside the ring resonators. By power dissipation in the micro heaters, we have changes in the current generated by photodiodes.

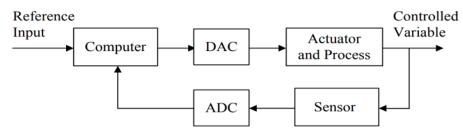

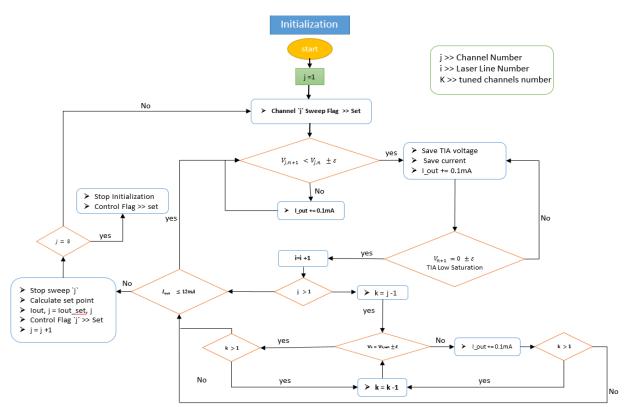

By observation of the monitoring PDs and controlling the power dissipation in the micro heaters, it is desired to control dynamically the wave length of an optical telecommunication system with 8 pair of transmitters and receivers. So main goals for the defined project can be according to:

- Monitoring the currents of the low frequency photodiodes

- Conversion of the analog signal to digital signal

- Processing data and generation of the control law

- Conversion of the generated digital control law to analog signal

- Applying power to dissipate in the micro heater to tune the optical channel

To reach the desired goals of the project, there is a need to design of compatible hardware based on micro controller to be able to process monitoring photodiode signals and generation of the control law for microheaters. Designing a hardware based on microcontroller causes to provide an optimized software to program the microcontroller. Since we need to monitor every channel as fast as possible and generate the control law in an appropriate time. In next section, we will discuss about the organization of the contents which will clarify the steps of the accomplishments during this project.

# **Organization of content**

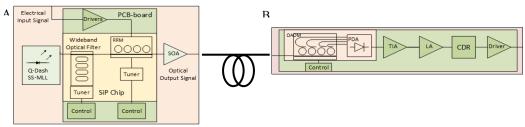

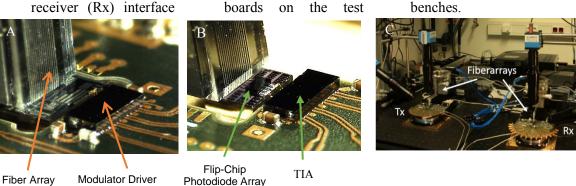

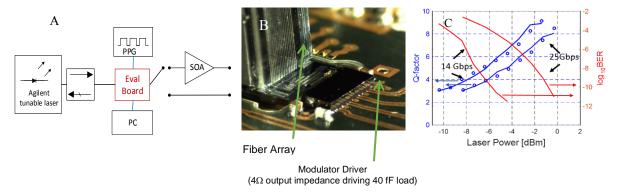

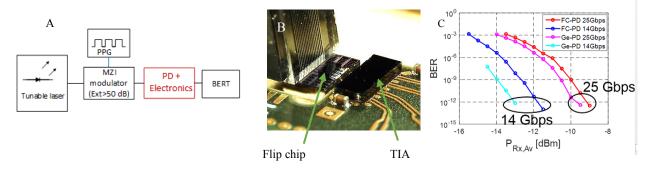

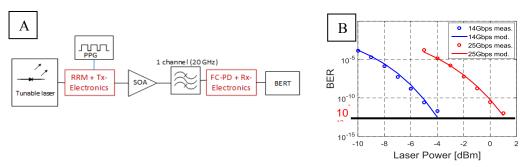

Regarding the definition of the steps for reaching the desires of the project, we will discuss first about the system which we are dealing with and much more details about it in chapter 2. In this chapter, we will have review on the dealt optical system, WDM system architecture, transmitter of the system which includes RRM, filter and OADM of the system. Moreover, in receiver section we will have discussion about the performance of OADM in receiver part and about the fabricated photodiodes (Ge PD) and flip chip PDs. Next section will be related to WDM control system and the tuning control PCB in the whole architecture of the optical telecommunication system. In this part, we will discuss about the lack of a control system and effect of it on the output signal in receiver part by considering the ideal performance of the other components of the system. Finally, in chapter 2 we will discuss about the solution of the problem raised by lack of control system and non-ideality of data modulation caused by it.

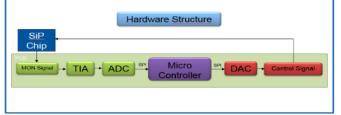

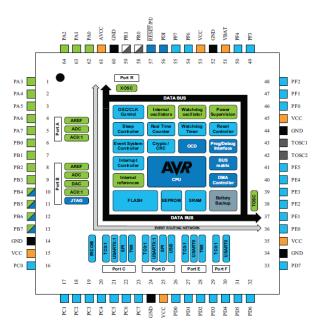

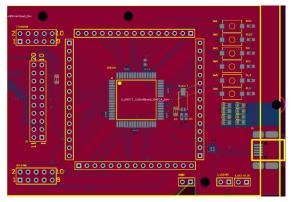

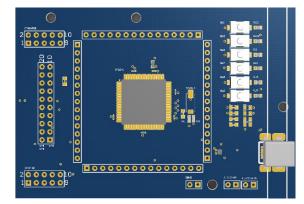

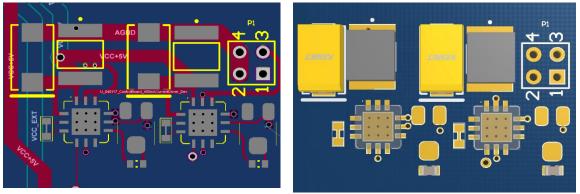

In chapter 3, we will discuss about the designed hardware which is compatible to acquire data, process and generation of control law for microheaters. Designed hardware contains transimpedance amplifier for conversion of photodiodes' current to voltage, an analog to digital convertor, a microcontroller to process data, a digital to analog convertor and finally an output buffer for supporting the power dissipation in micro heaters. In this chapter, there will be detailed discussions about every part and in case of possibility simulation of the designed hardware will be provided. The last part of this chapter will be about the manufactured and assembled hardware and summarization about it.

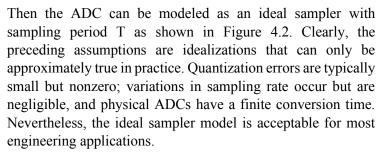

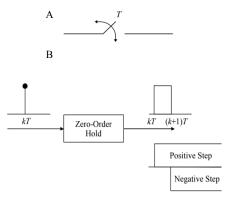

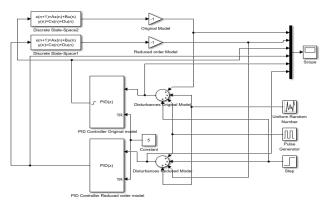

In chapter 4, the system under control will be studied in terms of control theory. Frist the control system will be defined in aspect of digital control theory and it will be attempted to model the whole system as first order system and the hardware limitations and features affecting on the controlling system will be discussed. Then a static model of the micro ring resonators and micro heaters will be provided then it will be attempted to provide a dynamic model of the system and response time of the system for suitable inputs will be discussed. A comparison of the modeled system in theory and experiments will be studied and the solutions and the approach will be discussed in next section which contains initialization and controlling the system. Final section in this chapter is allocated to the realization of the control solutions by hardware and preparing the driver codes and control codes of the system and implementation of them on the hardware.

In the chapter 5, the measurement result of the optical telecommunication system under control will be presented and will be discussed. Then, we will have summarization and conclusion of the project and the prospects of the project.

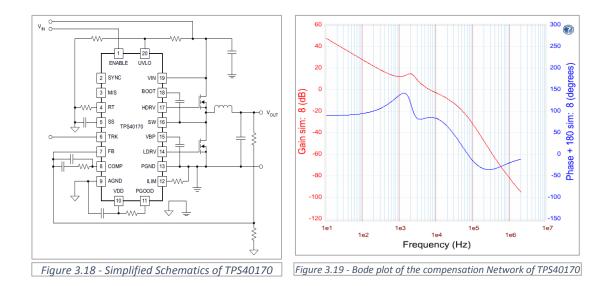

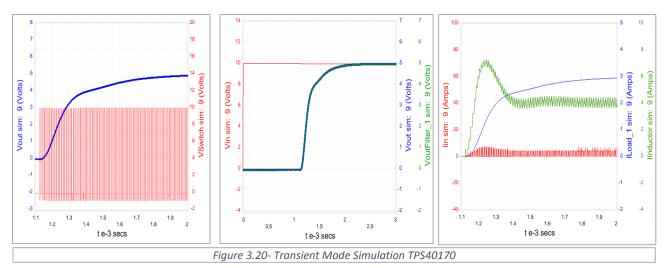

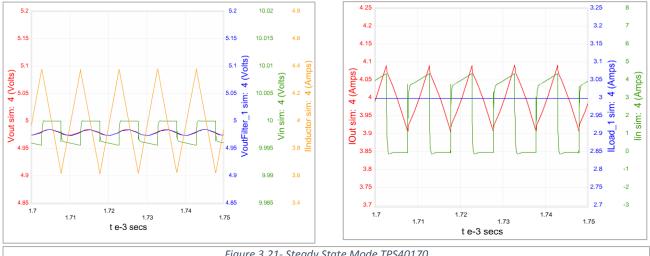

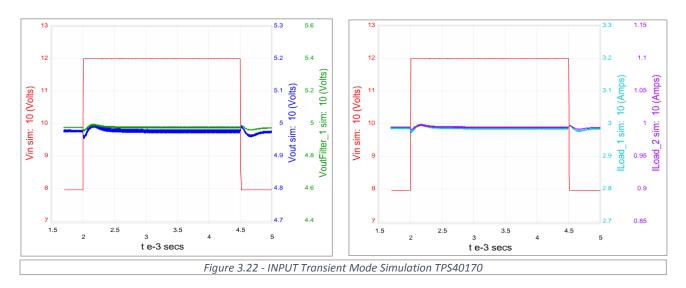

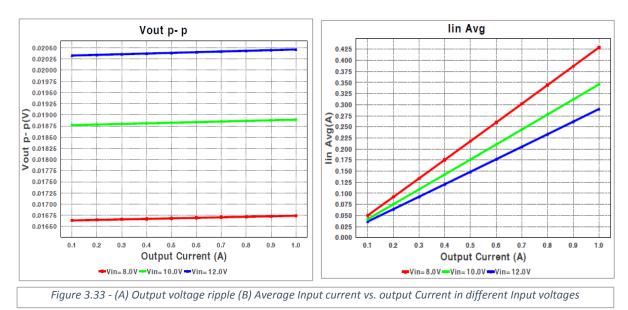

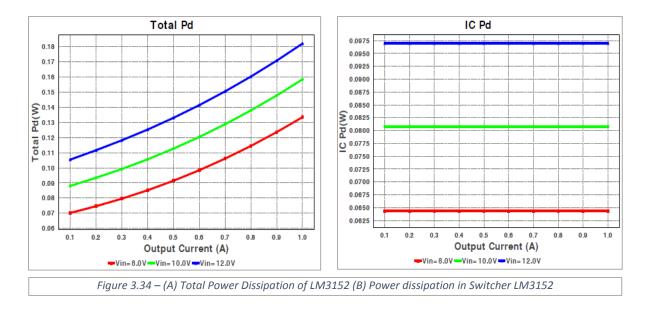

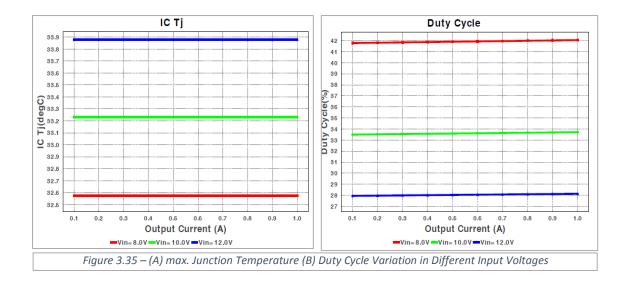

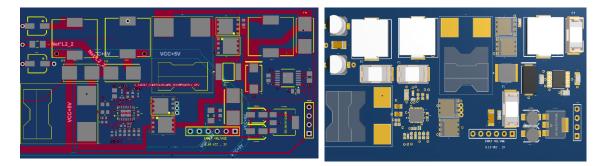

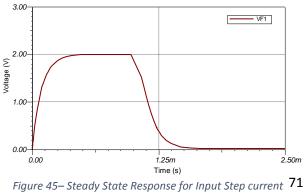

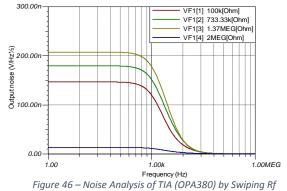

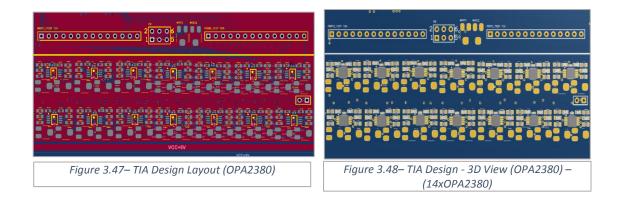

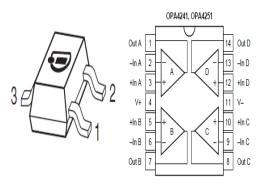

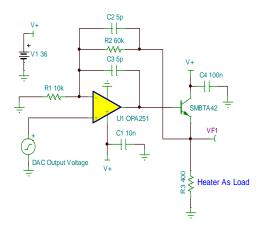

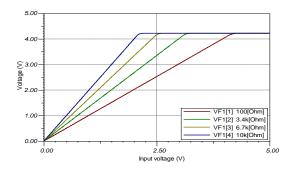

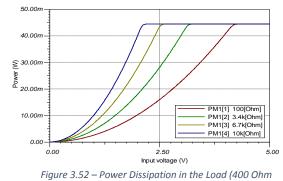

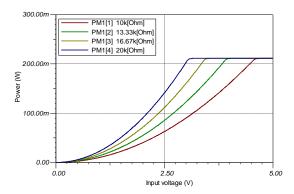

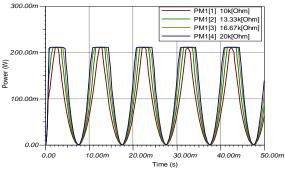

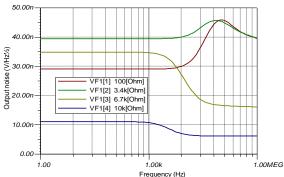

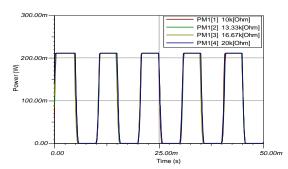

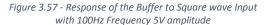

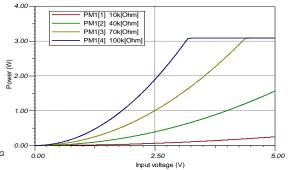

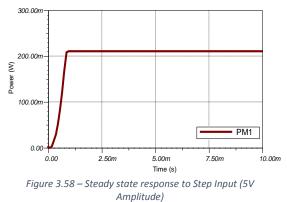

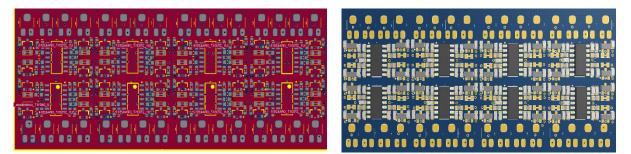

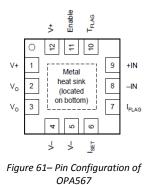

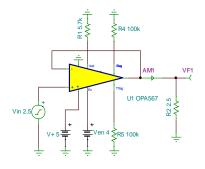

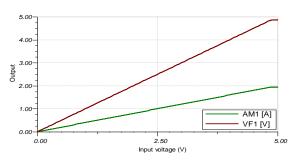

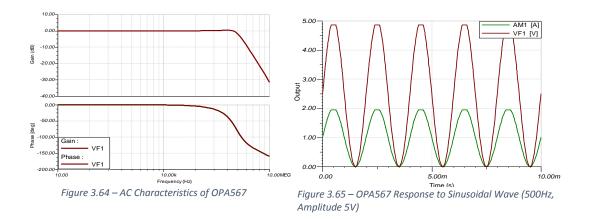

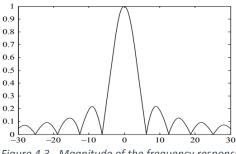

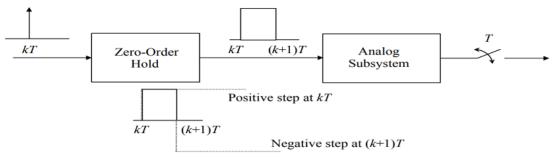

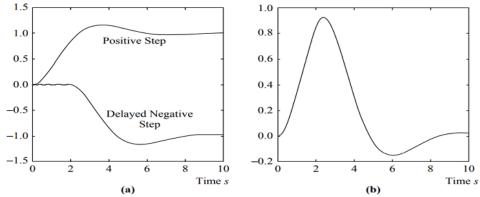

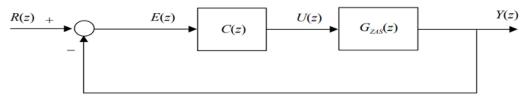

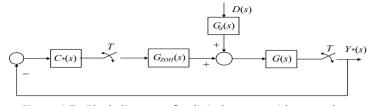

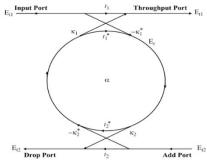

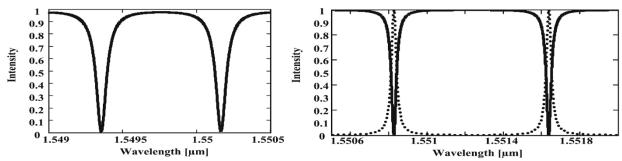

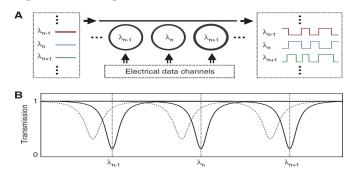

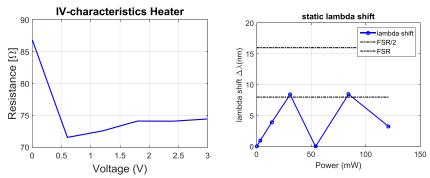

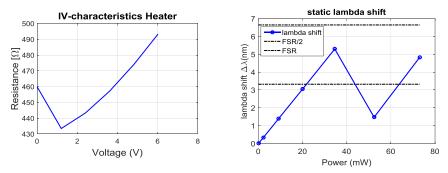

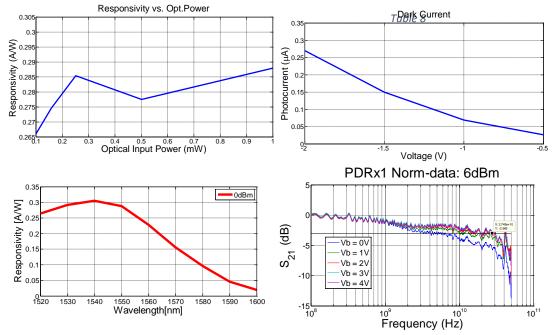

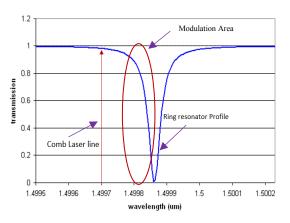

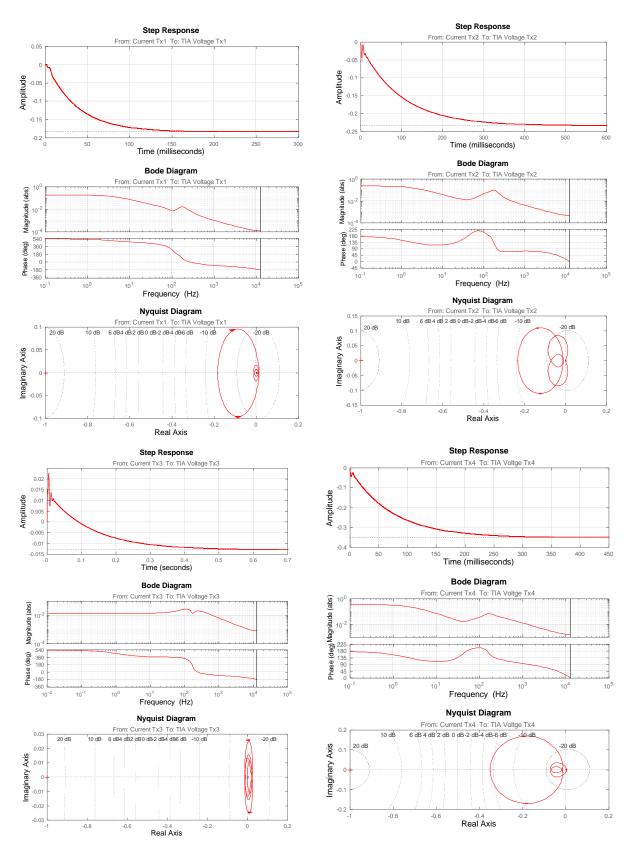

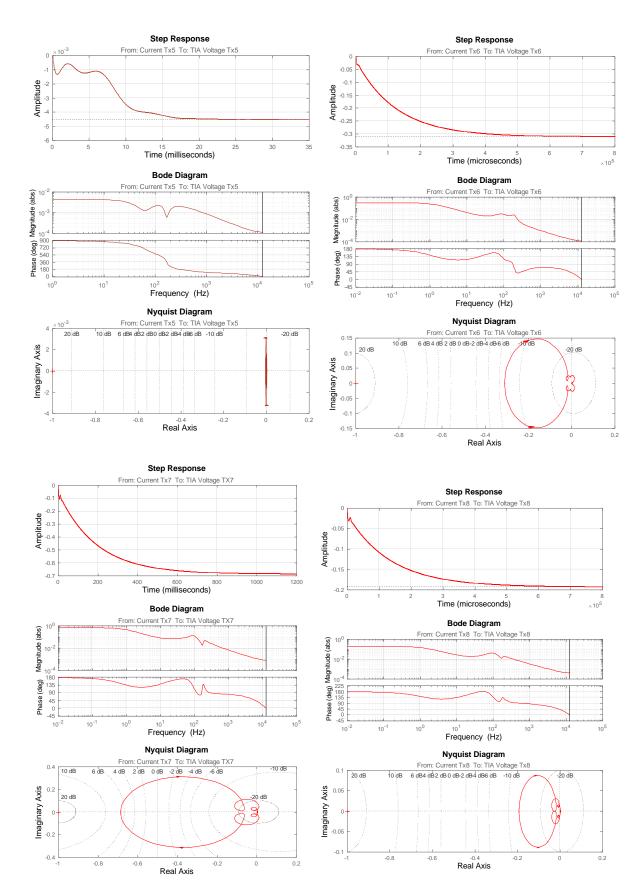

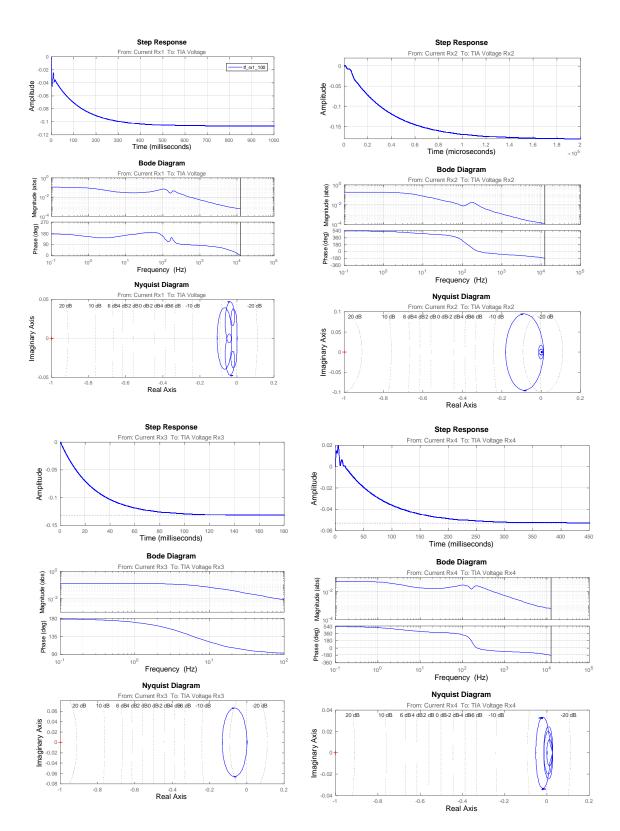

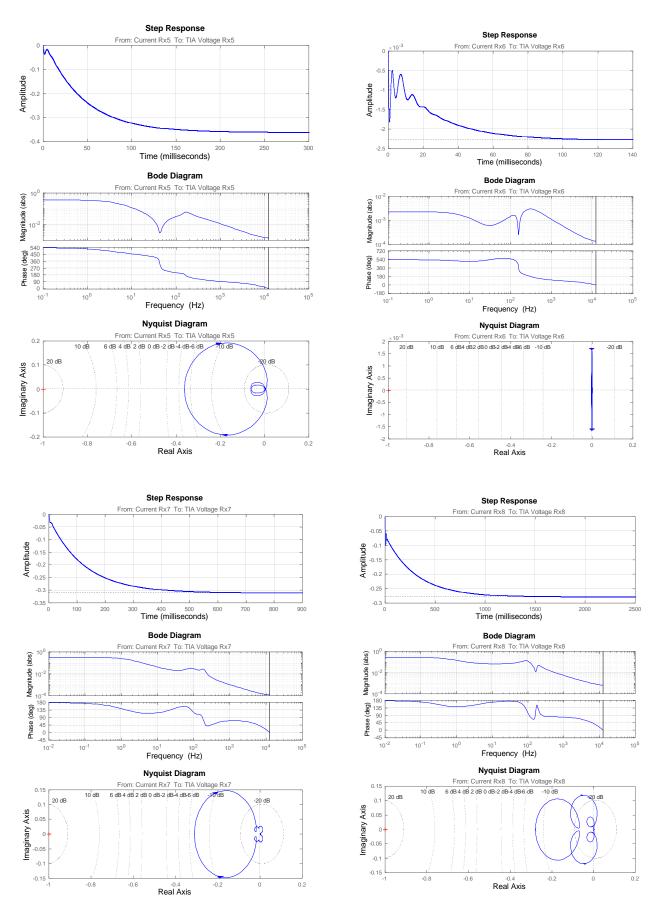

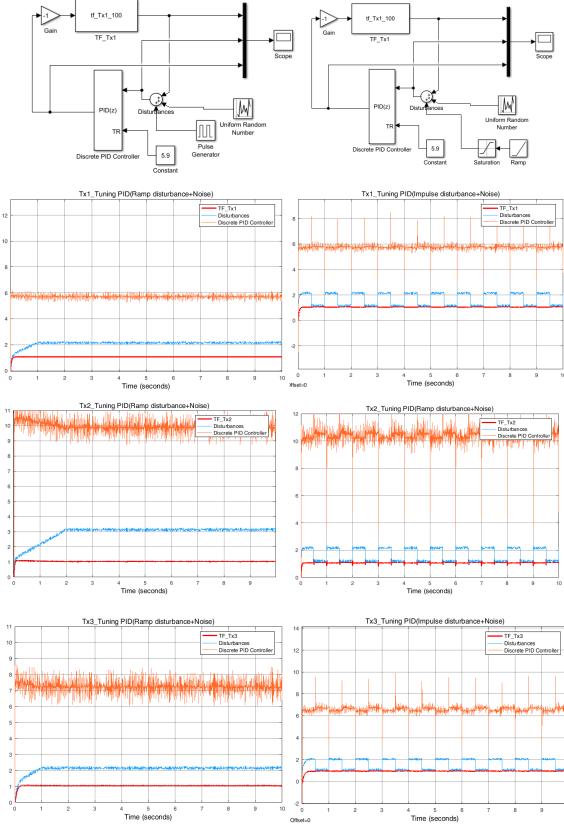

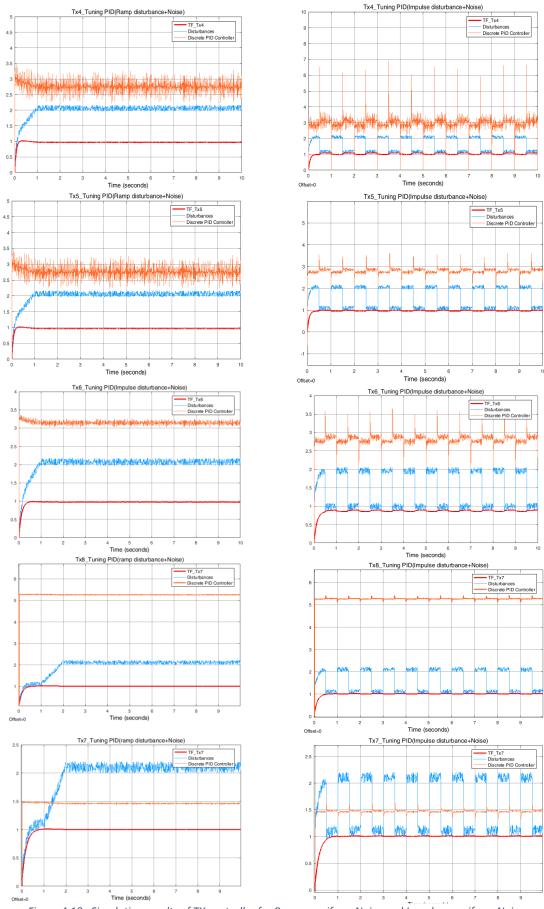

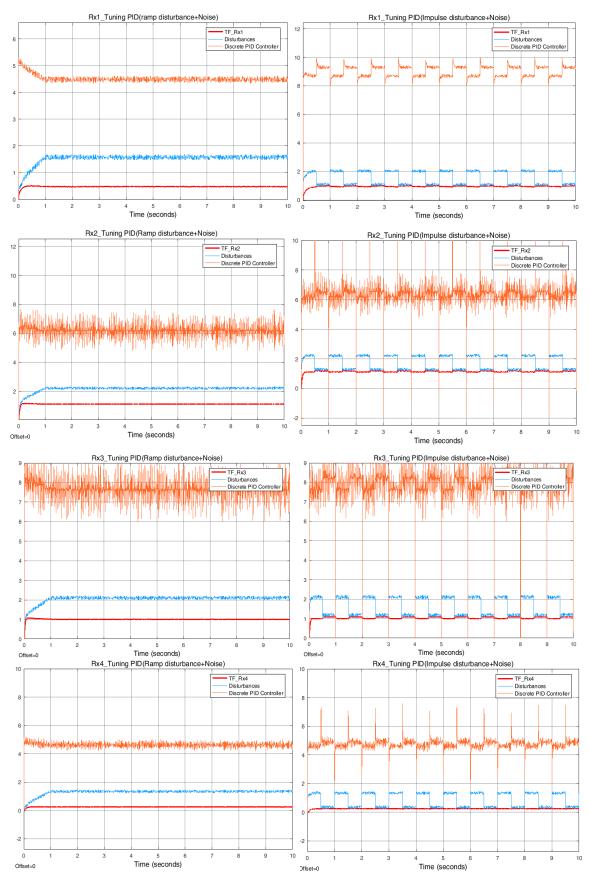

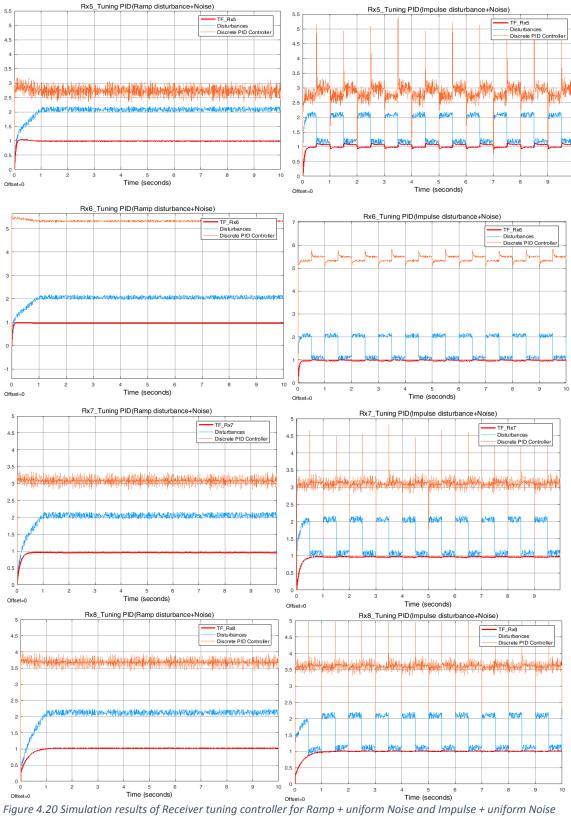

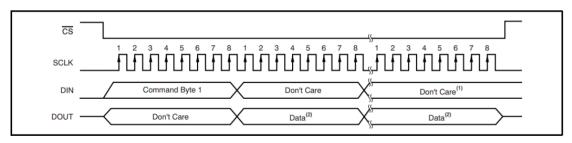

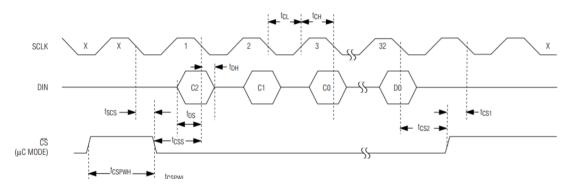

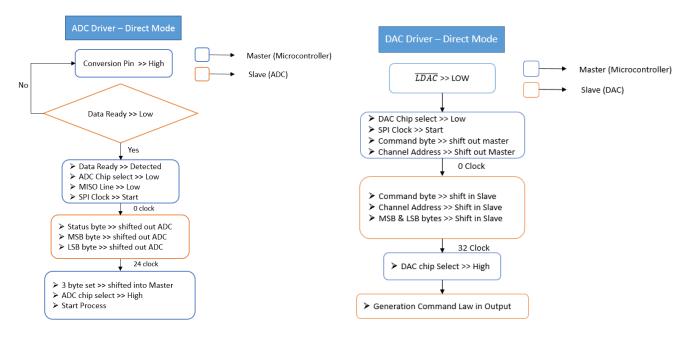

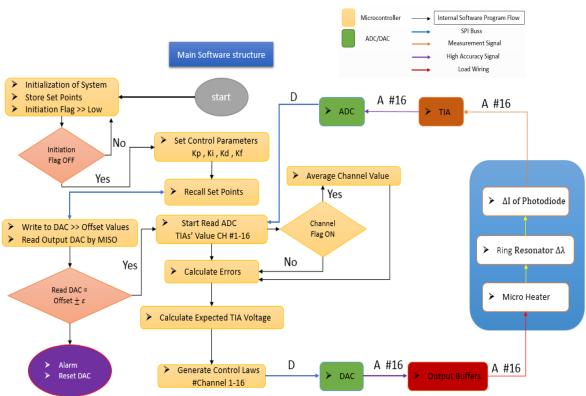

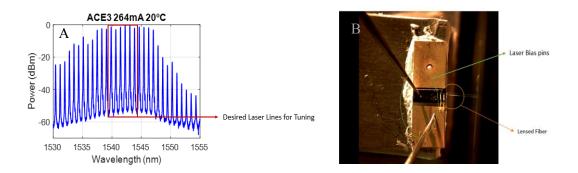

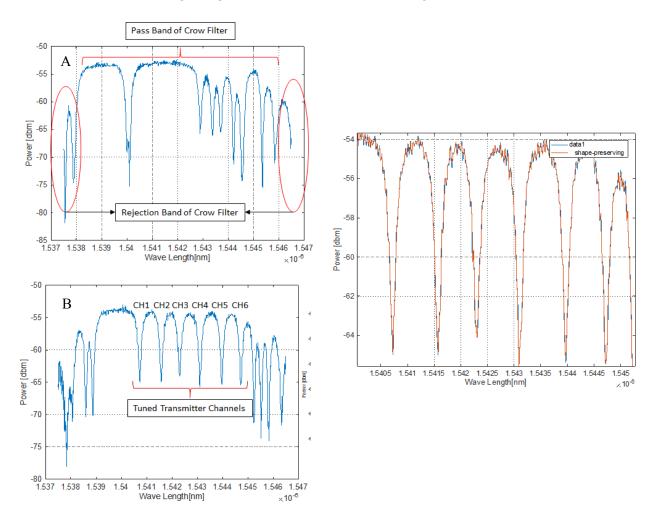

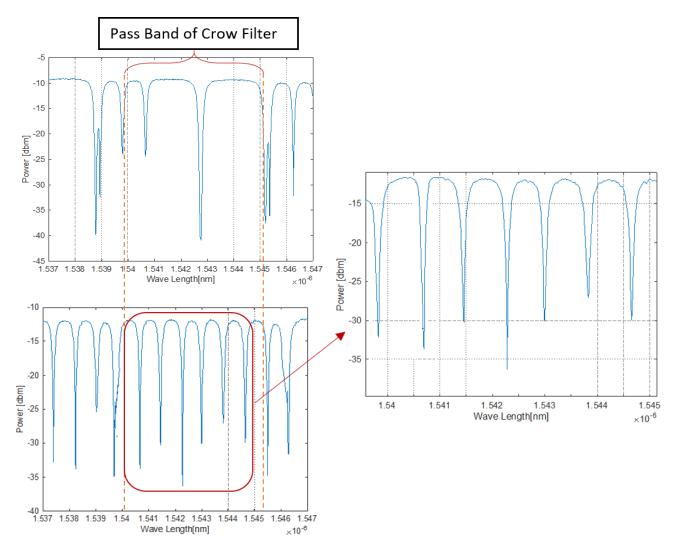

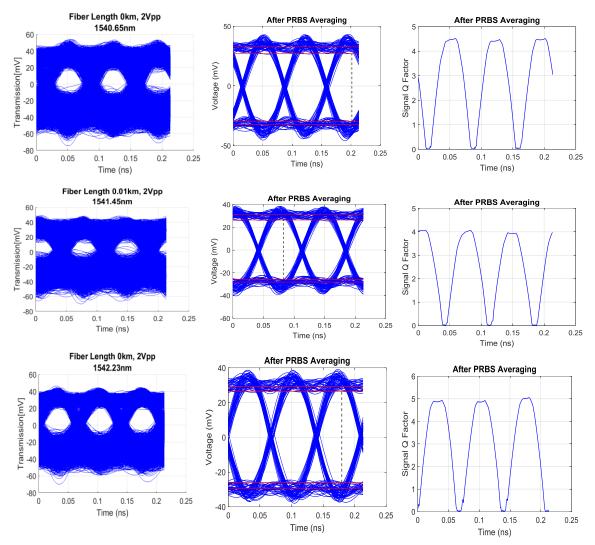

# II. Chapter 2: WDM System subject to control <u>Overview</u>