# POLITECNICO DI MILANO DIPARTIMENTO DI ELETTRONICA, INFORMAZIONE E BIOINGEGNERIA DOCTORAL PROGRAMME IN COMPUTER SCIENCE AND ENGINEERING

## Compiler Techniques for Binary Analysis and Hardening

Doctoral Dissertation of:

Alessandro Di Federico

Supervisor:

Prof. Giovanni Agosta

Tutor:

Prof. Andrea Bonarini

The Chair of the Doctoral Program:

Prof. Andrea Bonarini

XXX Cycle

# Contents

| Li | ist of | Figures                                                                  |

|----|--------|--------------------------------------------------------------------------|

| Li | ist of | Algorithms                                                               |

| Li | ist of | Listings                                                                 |

| Li | ist of | Tables x                                                                 |

| A  | bstra  | t xii                                                                    |

| In | itrod  | ction     xv       Binary Analysis     xv       Binary Hardening     xvi |

| Ι  | rev    | .ng: a unified binary analysis framework 1                               |

| 1  | Bac    | ground 3                                                                 |

|    | 1.1    | The Compilation Process                                                  |

|    | 1.2    | ELF                                                                      |

|    |        | 1.2.1 Object Files                                                       |

|    |        | 1.2.2 Executable Programs                                                |

|    |        | 1.2.3 Dynamic Loading                                                    |

|    | 1.3    | LLVM                                                                     |

|    |        | 1.3.1 The LLVM IR                                                        |

|    | 1.4    | QEMU                                                                     |

|    | 1.5    | Monotone Frameworks                                                      |

| 2  | Ar     | v.ng Overview 23                                                         |

|    | 2.1    | Requirements and design criteria                                         |

|    | 2.2    | revamb: a Static Binary Translator                                       |

|    |        | 2.2.1 Representation of the CPU State                                    |

|    |        | 2.2.2 Basic Block Identification                                         |

|    |        | 2.2.3 Organization of the Translated Code                                |

|    |        | 2.2.4 Handling of Operating System Interactions 28                       |

|    |        | 2.2.5 Identification of Function Calls                                   |

ii CONTENTS

|   | 2.3 | Advanced Features                                       | 30 |

|---|-----|---------------------------------------------------------|----|

|   |     | 2.3.1 Debugging                                         | 31 |

|   |     | 2.3.2 Dynamic Libraries Support                         | 32 |

|   |     | 2.3.3 Instrumentation                                   | 34 |

|   |     | 2.3.4 An Alternative Front-end: CGEN                    | 36 |

|   |     | 2.3.5 Extending Platform Support                        | 37 |

|   | 2.4 | Performance                                             | 37 |

| 3 | Bas | ic Block Identification                                 | 43 |

|   | 3.1 | Problem Statement                                       | 43 |

|   |     | 3.1.1 Identifying Code and Basic Blocks                 | 43 |

|   |     | 3.1.2 Challenges in Jump Target Recovery                | 45 |

|   | 3.2 | Harvesting Data and Code                                | 46 |

|   |     | 3.2.1 Global Data Harvesting                            | 46 |

|   |     | 3.2.2 Simple Expression Tracker                         | 46 |

|   | 3.3 | The OSR Analysis                                        | 47 |

|   |     | 3.3.1 OSR Tracking                                      | 50 |

|   |     | 3.3.2 BV Tracking                                       | 51 |

|   |     | 3.3.3 Load and Store Handling                           | 53 |

|   |     | 3.3.4 Integration with SET                              | 54 |

|   | 3.4 | Experimental Results                                    | 54 |

|   |     | 3.4.1 Functional Testing                                | 56 |

|   |     | 3.4.2 Basic Block Size                                  | 56 |

|   | 3.5 | Conclusions                                             | 59 |

| 4 | CFO | G and Function Boundaries Identification                | 61 |

|   | 4.1 | Challenges                                              | 62 |

|   |     | 4.1.1 Challenges in CFG Recovery                        | 62 |

|   |     | 4.1.2 Challenges in the Recovery of Function Boundaries | 63 |

|   | 4.2 | Design                                                  | 64 |

|   |     | 4.2.1 Handling of Reaching Definitions                  | 64 |

|   |     | 4.2.2 Function Boundaries Recovery                      | 67 |

|   | 4.3 | Experimental Results                                    | 70 |

|   |     | 4.3.1 Accuracy of the Recovered Function Boundaries     | 71 |

|   |     | 4.3.2 Case Study: the Buggy Memset                      | 76 |

|   | 4.4 | Conclusions                                             | 78 |

| 5 | Fun | ction Prototype Identification                          | 79 |

|   | 5.1 | Problem Statement                                       | 79 |

|   |     | 5.1.1 Calling Conventions Overview                      | 80 |

|   |     | 5.1.2 Code Outlining                                    | 81 |

|   | 5.2 | Design                                                  | 82 |

|   |     | 5.2.1 Assumptions                                       | 83 |

|   |     | 5.2.2 The Stack Analysis                                | 84 |

|   |     | 5.2.3 The Arguments Analyses                            | 87 |

|   |     | 5.2.4 The Final Output                                  | 90 |

CONTENTS iii

| 6  |      | clusio |                                 | 97  |

|----|------|--------|---------------------------------|-----|

|    | 6.1  |        | ations and Future Directions    |     |

|    | 6.2  | Relate | ed Works                        | 97  |

|    |      |        |                                 |     |

| II | C    | ompi   | ler-aided Binary Hardening      | 101 |

| 7  | Hex\ |        | a Variadic Function Sanitizer   | 103 |

|    | 7.1  | Introd | luction                         | 103 |

|    | 7.2  | Backg  | round                           | 105 |

|    |      | 7.2.1  | Variadic Functions              | 105 |

|    |      | 7.2.2  | Variadic Functions ABI          | 106 |

|    |      | 7.2.3  | Variadic Attack Surface         | 107 |

|    |      | 7.2.4  | Format String Exploits          | 108 |

|    | 7.3  | Threa  | t Model                         | 108 |

|    | 7.4  | Design | n                               | 109 |

|    |      | 7.4.1  | Analysis and Instrumentation    |     |

|    |      | 7.4.2  | Runtime Support                 |     |

|    |      | 7.4.3  | Challenges and Discussion       |     |

|    | 7.5  | Imple  | mentation                       |     |

|    | 7.6  | -      | ation                           |     |

|    |      | 7.6.1  | Case Study: CFI Effectiveness   |     |

|    |      | 7.6.2  | Exploit Detection               |     |

|    |      | 7.6.3  | Variadic Functions Statistics   |     |

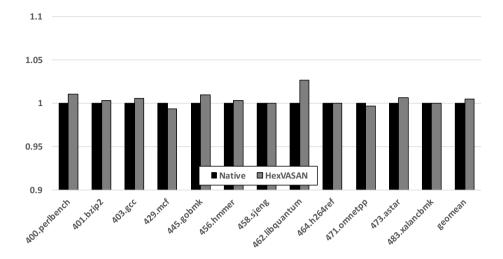

|    |      | 7.6.4  | SPEC CPU2006                    |     |

|    | 7.7  | Relate | ed Works                        |     |

|    | 7.8  |        | usions                          |     |

| 8  | leak | less:  | Bypassing Link-time Hardenings  | 127 |

|    | 8.1  | Introd | luction                         |     |

|    | 8.2  |        | ed Works                        |     |

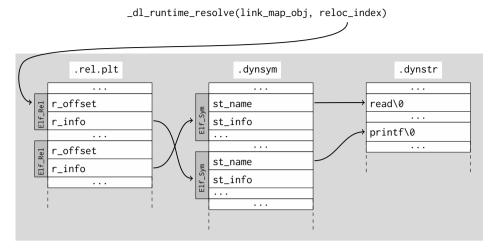

|    | 8.3  |        | Oynamic Loader                  |     |

|    |      | 8.3.1  | The ELF Object                  |     |

|    |      | 8.3.2  | Dynamic Symbols and Relocations |     |

|    |      | 8.3.3  | Lazy Symbol Resolution          |     |

|    |      | 8.3.4  | Symbol Versioning               |     |

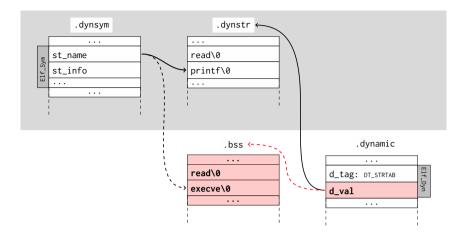

|    |      | 8.3.5  | The .dynamic Section and RELRO  |     |

|    | 8.4  |        | attack                          |     |

|    | 0.1  | 8.4.1  | The Base Case                   |     |

|    |      | 8.4.2  | Bypassing Partial RELRO         |     |

|    |      | 8.4.3  | Corrupting Dynamic Loader Data  |     |

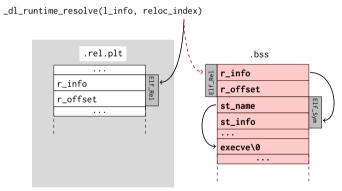

|    |      | 8.4.4  | The Full RELRO Situation [149]  |     |

|    | 8.5  |        | mentation                       |     |

|    | 0.0  | 8.5.1  | Required Gadgets                |     |

|    | 8.6  |        | ation                           |     |

|    | 0.0  | 8.6.1  | Dynamic Loaders                 |     |

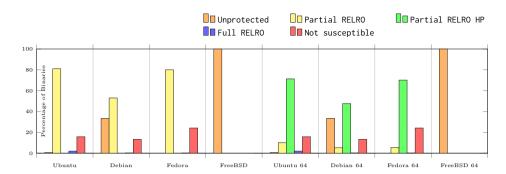

|    |      | 8.6.2  | Operating System Survey         |     |

|    |      | 0.0.2  | operating system survey         |     |

iv CONTENTS

|              |       | 8.6.3   | Case Study: Wireshark           | . 145 |

|--------------|-------|---------|---------------------------------|-------|

|              |       |         | Case Study: Pidgin              |       |

|              |       | 8.6.5   | ROP Chain Size Comparison       | . 146 |

|              | 8.7   | Discus  | sion                            | . 147 |

|              |       | 8.7.1   | leakless Applications           | . 148 |

|              |       | 8.7.2   | Limitations                     |       |

|              |       | 8.7.3   | Countermeasures                 | . 149 |

|              | 8.8   | Conclu  | ısion                           | . 151 |

|              |       |         |                                 |       |

| Co           | nclu  | sions   |                                 | 153   |

| ъ.           |       | ,       |                                 | 120   |

| Вı           | bliog | graphy  |                                 | 153   |

| A            | Sym   | abol Ve | ersioning Challenges            | 169   |

|              | ·     |         | raints due to Symbol Versioning |       |

|              |       |         | Tuge Page Issue                 |       |

|              | 11.2  | 1110 11 | 450 1 450 10040                 | . 110 |

| $\mathbf{B}$ | Dal   | Vange   | elo secondo LLVM                | 173   |

# List of Figures

| 1.1 | Overview of the Compilation Process                       |

|-----|-----------------------------------------------------------|

| 1.2 | Architectures Supported by QEMU                           |

| 1.3 | Graphs Representing Two Simple Programs                   |

| 2.1 | Overview of the Static Binary Translation Process         |

| 2.2 | gdb Stepping Through LLVM IR                              |

| 2.3 | Dispatcher Hindering Optimization                         |

| 3.1 | Example of the SET Algorithm                              |

| 3.2 | FSM Representing the BV Signedness State Transitions 52   |

| 3.3 | LLVM IR Generated by Two ARM Instructions                 |

| 4.1 | LLVM IR Example of the Need for Path-sensitive Merging 65 |

| 4.2 | ARM Instructions Sharing the Same Predicate               |

| 4.3 | ARM Example of Skipping Jumps 69                          |

| 4.4 | uClibc ARM Implementation of memset                       |

| 5.1 | Graphs of the Argument Analyses                           |

| 7.1 | Overview of the HexVASAN Compilation Pipeline             |

| 7.2 | Run-time Overhead in the SPECint CPU2006                  |

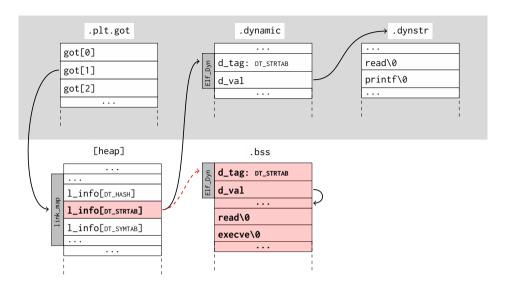

| 8.1 | Data Structures Involved in Symbol Resolution             |

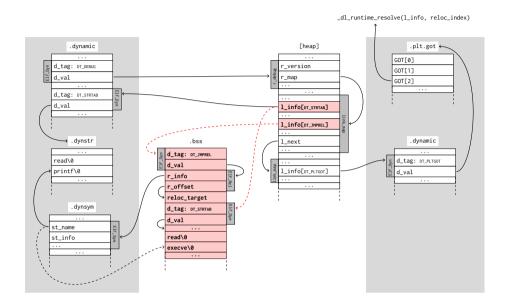

| 8.2 | Illustration of some of the Presented Attacks             |

| 8.3 | Example of the Attack Presented in Section 8.4.3 139      |

| 8.4 | Example of the Attack Presented in Section 8.4.4 140      |

| 8.5 | Classification of the Binaries of Target Distributions    |

# List of Algorithms

| 1.1 | The MFP Solution Algorithm                           | 21  |

|-----|------------------------------------------------------|-----|

| 3.1 | The Simple Expression Tracker Algorithm              | 49  |

| 4.1 | The Path-sensitive Merging Algorithm for Constraints | 72  |

| 7.1 | The Instrumentation Process                          | 111 |

| 7.2 | hashType                                             | 113 |

# List of Listings

| 1.1 | Key Parts of an Object File                                |

|-----|------------------------------------------------------------|

| 1.2 | Example of PIC Code Employing the PLT                      |

| 1.3 | Simple C Function and Corresponding LLVM IR                |

| 1.4 | Tiny Code Instructions Generated from a x86 call 16        |

| 2.1 | Example of the Dispatcher                                  |

| 2.2 | Code Generated by a x86-64 Call Instruction                |

| 2.3 | Example of Handling of a Dynamic Function Call 40          |

| 2.4 | C++ Code Generated by CGEN                                 |

| 3.1 | ARM and an x86-64 switch Statement                         |

| 5.1 | Prologue and Epilogue Outlining in Hexagon and ARC 82      |

| 5.2 | Stack Analysis Tracking Values of a Slot                   |

| 5.3 | Example of the Relevant Code for each Argument Analysis 89 |

| 5.4 | C++ Code Generated for URVOF                               |

| 7.1 | Example of a Variadic Function in C                        |

| 7.2 | Instrumented Version of Listing 7.1                        |

| 7.3 | Error Message Reported by HexVASAN                         |

| 7.4 | Exploit Detection in sudo                                  |

| 7.5 | Variadic Violation in omnetpp                              |

| 8.1 | Example PLT and GOT                                        |

| 8.2 | The Pidgin Attack                                          |

# List of Tables

| 2.1 | revamb, Pin, QEMU and Valgrind Performance Comparison 42       |

|-----|----------------------------------------------------------------|

| 3.1 | Effect of Composing an OSR with a Constant 51                  |

| 3.2 | Statistics Concerning the Translation of coreutils Binaries 58 |

| 4.1 | IDA Pro, rev.ng, BAP, and angr Experimental Results 73         |

| 4.2 | Analyses Performance                                           |

| 7.1 | Detection of Illegal Variadic Function Calls                   |

| 7.2 | Statistics of Variadic Functions for Different Benchmarks 125  |

| 8.1 | Entries of the .dynamic Section                                |

| 8.2 | Gadgets Required for the Various Approaches                    |

| 8.3 | Size of ROP Chains Produced by ROPC and leakless 147           |

# Abstract

Despite the growing popularity of interpreted or byte-compiled languages, C/C++ and other languages targeting native code are still dominantly used for system programming. Programs compiled to native code present a set of challenges compared to alternatives. In particular, in this work we focus on how they can be efficiently analyzed, how existing security measures (known as binary hardening techniques) perform, and how new ones can be introduced to secure features that have received little attention.

We propose rev.ng a binary analysis framework based on QEMU, a popular dynamic binary translator and emulator, and LLVM, a mature and flexible compiler framework. rev.ng can easily handle a large number of architectures and features a set of analyses to recover basic blocks locations, function boundaries and prototypes in an architecture- and ABI-independent way. rev.ng can be used for instrumentation, debugging, decompilation, retrofitting of security features and many more purposes. Our prototype encompasses about 17 kSLOC of C++ code and has been publicly released under a Free Software license.

The core component of rev.ng is revamb: a static binary translator which can accurately identify all the basic blocks, and, in particular, the targets of indirect jumps for switch statements. Along this work, we will make heavy use of analysis techniques popular in the compiler literature, such as Monotone Frameworks, to recover an accurate control-flow graph, identify function boundaries and the number and location of function arguments and return values.

We will also discuss how rev.ng can handle native dynamic libraries, how it can be easily employed for instrumentation purposes, how it can be extended to handle even more architectures and how its performance compares to tools with analogous purposes such as QEMU, Valgrind, Pin and angr.

We also study two often overlooked features of C/C++ programs: variadic functions and the RELRO link-time protection mechanism. We propose HexVASAN, a sanitizer for variadic functions to ensure that the number and type of arguments used by the variadic function match those passed by the caller, and leakless, an exploitation technique to bypass the RELRO protection in its several forms.

# Introduction

Despite the growing popularity of interpreted languages, such as Python and Ruby, and languages that compile to some form of byte-code, such as C# or Java, a large part of the software is still being written in languages directly targeting *native code*, such as C and C++. Such languages are popular for performance critical software, system level software, bare metal software, kernels and embedded systems in general.

Compared to languages targeting interpreters or byte code, they generally provide better performance but carry with them a series of challenges. In this work we will focus on two challenging aspects in particular: reverse engineering and safety of native code.

On the reverse engineering side, which in the native world takes the name of binary analysis, we face many issues: native code is not intended to be read by a human or even a compiler. It's a final product, ready to be run, which is not supposed to be further manipulated (e.g., for optimization purposes) or read. Native code is composed of low level instructions which provide basically no abstraction whatsoever. A loop might be completely unrolled, common strings of assembly instructions might be factored out in a function, arithmetic or logical operations might be turned into different but semantically equivalent instructions and so on.

On the safety side, languages targeting native code often do not provide full memory safety, which makes it harder to write secure software. Therefore, along the years, a wide range of countermeasures have emerged. Many of such protection mechanisms can be automatically applied during the compilation process without further action on the developer side. Some of the most popular ones include ASLR, CFI, stack canaries, W^X and many others. These techniques, which involve the compiler, the linker, the dynamic loader, the kernel and other components of the operating system, are collectively know as binary hardening techniques.

### Binary Analysis

Digital devices have become a key part of our everyday life, carrying a large amount of benefits, and risks. In fact, for each software platform gaining enough popularity, a set of malicious software (malware) to abuse them is developed.

To be able to effectively oppose them, understanding their behavior and how they're built is of critical importance. For this reason, a series of tools for analyzing software for which source code is not available is fundamental. Such tools are often xvi INTRODUCTION

known as reverse engineering or static binary analysis tools. In certain situations, the reverse engineering effort can be aided by not only analyzing the program, but also running it with certain changes to better understand its behavior. Such an activity is known as dynamic binary analysis.

Information learned through static analysis is generally applicable but runs into precision issues while dynamic analysis has better precision, as an actual instance is being evaluated, but is limited to existing test cases, i.e., the code must be *executed* in a run-time setting to be analyzed.

Reverse engineering tools can also be employed to analyze ordinary software, typically provided by third parties which do not release the source code. The analysis of non-malicious software enables the assessment of the security of components outside the control of their users. For instance, companies or public entities dealing with sensitive data might want to analyze software provided by third parties to investigate the presence of bugs or, even worse, backdoors. To these ends, the most useful reverse engineering tool is a *decompiler*, a tool able to recover a representation of the program's behavior that is close to the original source code, and therefore easier to understand with respect to low level machine code which is produced by disassemblers.

While several reverse engineering tools are available, they have been lacking in innovation, usability and the diversity of the hardware platforms they are able to handle. In fact, existing tools either develop a set of ad-hoc heuristics to handle each new architecture (IDA Pro [72]) or, if the tool employs an intermediate representation for its analyses, it has to create a new front-end to handle each new architecture. Examples of the latter case are BAP/ByteWeight [20, 11] (x86 and ARM only), MC-Semantics [152] (x86 only) and LLBT [139] (ARM only).

The diversity aspect is of particular relevance in a world being progressively dominated by IoT devices. In fact, the IoT ecosystem has historically paid little to no attention to security aspects and often employs unusual architectures, which makes the software running on them harder to analyze due to the lack of tools for those architectures. Therefore, the analyst is left with severely insufficient analysis capabilities. This is particularly important in the context of eHealth devices which are critical for the life of an always growing number of people and often employ little known, ultra-low power CPUs (e.g., RISC-V [175]).

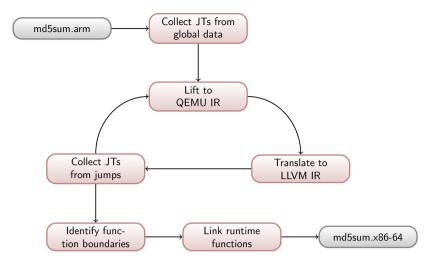

In this work we propose rev.ng, a unified system for binary analysis which employs a set of principled techniques rather than architecture-specific heuristics for its analyses and that, unlike existing works, defers the burden of providing a reliable front-end for a wide range of architectures to existing tools. In our prototype we rely on QEMU to provide such a front-end. QEMU is a dynamic binary translator that lifts binary code into a custom intermediate representation (IR) for 17 different architectures, including x86, x86-64, MIPS, ARM, and AArch64. As a tool aiming at full system emulation, QEMU supports even the most sophisticated ISA extensions. For instance, it already supports the recently introduced Intel MPX ISA extensions. Moreover, the large community and industry interest around QEMU virtually guarantees that new architectures and ISA extensions are supported promptly (e.g., RISC-V [129]).

The main benefit of this approach, besides the vastly reduced effort in handling

a large number of ISAs, relies on the fact that all the supported architectures are first-class citizens. Even more importantly, all the analyses built on top of the QEMU IR have to be designed in an ISA-agnostic way. In practice, when handling ISA-specific peculiarities, such as MIPS delay slots or ARM predicate instructions, the approaches are equally effective, respectively, on OpenRISC delay slots and x86-64 conditional move instructions. Many of the analyses that we will present apply techniques well known in the compiler field, such as data-flow analysis.

In our implementation, rev.ng, we translate the IR provided by QEMU into LLVM IR, an environment that facilitates further analyses. On top of this, rev.ng does not only allow the analyst to understand what a piece of software does, but also to alter its behavior in an easy way and introducing a low overhead compared to alternative tools. Therefore rev.ng also provides a unified framework for both static and dynamic analysis.

In the context of binary analysis, when dealing with C/C++ programs stripped of debugging information, there are a series of challenging tasks. In Part I, after providing the necessary background (Chapter 1), in Chapter 2, we will introduce rev.ng, our static binary analysis framework. In Chapter 3 we will focus on the identification of all the basic blocks in the code. In Chapter 4 our approach for the recovery of an accurate control-flow graph for the program and the detection of the boundaries of the original functions will be presented. Chapter 5 will introduce the rev.ng function prototype detection algorithm, i.e., the recovery of function arguments and return values. This information is vital for any reverse engineering efforts, and to build additional tools such as a decompiler. Part I will conclude with a review of related works (Section 6.2).

#### **Binary Hardening**

In Part II, we analyze two often overlooked aspects of the security of a binary program: the RELRO link-time hardening and variadic functions.

RELRO is a protection mechanism applied by the linker which comes in two flavors: partial and full. Its purpose is protecting data structures used by the dynamic loader to resolve functions. In fact, such data structures can be abused by an attacker able to run code (e.g., through a ROP chain) in the target process to call any library function. This is particularly interesting for the attacker since it reduces the complexity of the attack and allows him to call library functions such as system or functions more involved in the behavior of the specific program. In Chapter 8 we will describe and exploit several key design flaws in RELRO and suggest countermeasures.

The other key aspect of binary programs we focused our attention on are variadic functions. They are a popular feature of C/C++ programs which offers great flexibility. The most popular variadic function is the printf function. Such a flexibility comes at the cost of a non-negligible loss in terms of type safety. This is true at the point that a large part of a whole class of vulnerabilities, format string attacks, is due to this unsafety.

Variadic functions accept an arbitrary number of arguments of arbitrary types. If an attacker is able to provide arguments in an unexpected number or type, it can corrupt the integrity of the execution environment, with possibly serious security

xviii INTRODUCTION

consequences. In Chapter 7, we design and test the effectiveness of a compiler-based countermeasure for such attacks. The countermeasure is implemented as an LLVM sanitizer which instruments the code of variadic functions and variadic function calls, so that, at run-time, before accessing each argument, a check is performed to ensure that such an argument has actually been provided, and that the expected type corresponds too.

Apart from these two aspects, in terms of binary hardening, we also introduce a static binary translator based on the binary analysis framework presented in the previous section. Binary translation is a technique that, given an executable program (or a portion of it) compiled for a certain architecture (e.g., ARM), aims to translate it into a different one (e.g., x86-64). Binary translation can be performed statically or dynamically. The dynamic version is essentially a type of emulation technique where the emulation, usually a slow process, is sped-up by translating instructions into the host machine code at run-time. The static version is a much more complex endeavor, and it is aimed at building a full executable program which can then be executed autonomously. The motivation for developing a binary translator is provided by a wide range of applications. Historically, legacy code performance portability was the key motivation. Indeed, binary translation techniques have been employed to provide binary compatibility for new platforms, such as the Transmeta Crusoe [45] which achieves better performances than an emulator. In our cases, one of the main use cases consists in retrofitting binary hardening countermeasures, absent in the original binary, such as CFI [173, 156, 118, 170].

Static binary translators are particularly interesting because they do not impose a run-time overhead as significant as other approaches, and they can be used to generate new binaries that are completely independent of the translation system. However, they pose a number of additional challenges which must be solved in order to produce a standalone binary program.

In particular, discovering and identifying code in a binary object is a non-trivial task. Ideally, one would start from the entry point of the program, follow all jump and call to subroutine instructions to identify the starting points of all reachable code segments. However, this is made more complex by the usage of function pointers, virtual functions and, most importantly, switch statements. Chapter 2 and Chapter 3 describe our approach to these issues.

# Part I

rev.ng: a unified binary analysis framework

# Chapter 1

# Background

In this chapter we will present the key concepts and tools required to have a proper understanding of the rest of Part I. Specifically, we will first provide an overview of the compilation process, in general, and, specifically, for the ELF image format. Understanding the compilation process is fundamental, since our final aim is to reverse it. Then we will dig into the LLVM compiler framework (and its IR in particular) and the QEMU internals since they constitute the mainstays of rev.ng. The chapter ends with a section introducing Monotone Frameworks, a key theortical tool for building many of the analyses we will present to recover abstractions from binary code.

## 1.1 The Compilation Process

A large part of this work is devoted to the analysis of binaries. It's therefore of great importance to understand how such binaries are produced. In this section we will offer an overview of how a modern compiler works, from the source code down to the final executable binary.

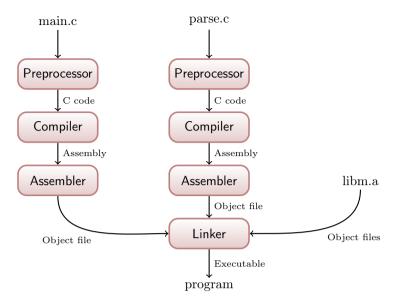

As shown in Figure 1.1, the compilation toolchain for languages such as C and C++, our main focus, is typically divided in four major components: the preprocessor, the compiler, the assembler and the linker.

**The preprocessor.** The preprocessor is the component responsible for, given an input file, removing comments, enabling or disabling certain portions of code (through the #ifdef directives) and, most importantly, expanding its body with all the included files (#include directives) and macros (#define directives). The final output is pure C code suitable to be fed to the compiler, which is not supposed to handle the above mentioned directives.

**The compiler.** The compiler is the core component of the compilation toolchain. It takes as input a preprocessed source file, also known as *translation unit*, and produces an assembly file, containing data and functions almost in their final form, i.e., instructions for the target CPU. Internally, modern compilers are divided in three further components: the *front-end*, the *mid-end* and the *back-end*. The *front-end* is programming language-specific: it parses the input file, builds an AST and

produces an intermediate representation (IR) which is independent from the input language and mostly independent of the targeted machine. The *mid-end* performs a set of "high-level" optimizations that are independent from the target architectures, such as loop unrolling, inlining and outlining of functions and many more. Finally, the *back-end* transforms the IR into a target-specific representation (i.e., where the functions contain instructions that are specific for a certain architecture) and performs another set of low-level optimizations that make sense or are beneficial only for the target CPU.

The assembler. The assembler takes as input a file with a textual representation of the functions, instructions and global data and encodes them into their binary representation, often referred to as *machine code*, that the CPU can understand. The output file is known as the *object file*. Note that the code is not in its final form. In fact, references to external variables or functions, and, in certain conditions, even references to the parts of functions defined in the current translation unit, are left pending, since only the linker can know their final value.

The linker. The linker is the component responsible to collect multiple object files, decide how their data and code is laid out (e.g., the code of the second object file is appended to the one of the first one), and fix references to code and data, left pending by the assembler, with their final value. In fact, the final position of each function or piece of data is known exclusively by the linker, which is the only component of the toolchain which has global visibility on all of the object files composing the program being compiled. The linker is allowed to leave some references pending, in case the corresponding function or data are available in a dynamic library. Another component, the dynamic loader, will finish the linking process upon program startup.

#### 1.2 ELF

ELF (Executable and Linkable Format) is an image format for object files, executable programs and dynamic libraries. It's the standard image format on GNU/Linux and many other unix-like operating systems (with the notable exception of macOS) and for embedded systems. In this section we will provide an in-depth description of it, since it's the main image format we consider in this work. Note however that other binary formats (such as Mach-O) have analogous features and extending a tool to support them is primarly engineering work.

Each ELF file starts with the ELF header. The ELF header contains the following information: a magic byte sequence used to easily identify the file as an ELF image, its the endianess, the target architecture, whether it's a 32-bit or 64-bit, the target operating system and ABI, the type of ELF image and a couple more fields.

The ELF format is defined (in terms of the data structure it contains and their layout) independently from the target architecture, except for two characteristics: the endianess and whether the target architecture is 32- or 64-bit. Therefore, depending on the size and the endianess used to encode integers, there are four different type of ELF formats: ELF32BE, ELF32LE, ELF64BE, ELF64LE. Except for this, and other minor differences, they are analogous.

There are five different types of image formats that can be encoded in ELF:

1.2. ELF 5

Figure 1.1: Overview of the compilation process.

**Object files (ET\_REL)** Relocatable object files, as emitted by the compiler/assembler. They typically have a .o extension.

**Executable programs (ET\_EXEC)** Executable programs, linked and ready to be run. They usually have no extension.

**Shared objects (ET\_DYN)** A dynamic library, linked and ready to be loaded by an executable program. They typically have a .so extension.

Core files (ET\_CORE) Images of a process that was running, written on disk for debugging purposes.

Unknown (ET\_NONE) An ELF file of an unspecified type.

In the following, we'll provide an overview of the key features of object files, executable programs and we'll conclude with an overview of how dynamic libraries and the dynamic loading process works.

### 1.2.1 Object Files

As previously mentioned, the assembler produces object files. ELF object files are primarily composed by three parts:

**Sections.** A section is a portion of the ELF object file that can contain either code or data. They are described by a *section header* that contains an offset within the file where the section begins, its size, a type and a series of flags. The most interesting sections to our ends are:

.text The core section containing the code of the object file. This section contains relocatable (i.e., with unresolved pending references) machine code.

- .data The writeable global data of the translation unit.

- .rodata The read-only global data of the translation unit.

- .bss The writeable global data of the translation unit. This section differs from .data in the fact that data here is "uninitialized", which means, automatically initialized to zero. Since the content of this section is implicitly all zero, it's not associated to any data in the object file. Therefore, its starting offset in the file has no real meaning and the size is just an indication of how much space will be needed (and zero-initialized) at run-time.

**Symbol table.** Another key section of object files is .symtab, which contains all the *symbols* of the translation unit. A symbol is a label for a portion of data or code, with an optional size. In practice, a symbol typically represents either a global variable or a function. If the symbol is defined in the current translation unit, then the symbol is also associated to an offset within the object file where it starts. Otherwise, if the symbol is used but not defined in the current translation unit, it is marked as undefined.

**Relocations.** The last core component are relocations. A relocation is basically a directive for the linker instructing it to write the value (i.e., address) of a certain symbol in a certain position within a section. Each one of the sections listed above can be associated with a section containing a sequence of relocations that apply to it. Such sections have the same name as the target section with a .rel prefix (e.g., relocations for .text will be in the .rel.text section).

Depending on the architecture, a relocation could also include a constant addend to add to the value of the symbol. In such cases, the relocations will have a .rela prefix.

It is important to understand that a relocation doesn't always write the address of the associated symbol in the same way. For example, in certain situations a relocation might instruct the linker to write the full 32-bit address of the symbol in a certain position, while in other situations it might require the value to be written as an offset from the destination address. This is particularly useful to encode the offset of a PC-relative jump instructions.

Listing 1.1 shows the relevant parts of an object file.

## 1.2.2 Executable Programs

As illustrated in Section 1.1, the linker is responsible to produce the final executable, performing the following steps:

Lay out the program. The linker parses all the input object files, and decides how the various sections have to be laid out in the final program. In practice, it groups the input sections into *segments* based by their attributes, such as being writeable, readable or executable. For instance, this means that .data and .bss will be grouped together since they are both writeable but not executable. Then, it concatenates all the input sections with the same name from the various input object files. Such an operation is fundamental to be able to assign a final address to each symbol.

1.2. ELF 7

```

$ gcc main.c -c -o main.o

$ readelf -S main.o

There are 7 section headers, starting at offset 0x130:

Section Headers:

Off

[Nr] Name

Type

Addr

Size

ES Flg Lk Inf Al

Γ 21 .text

PROGBITS 00000000 000040

00002f 00

AX

0

0

16

[ 3] .rel.text REL

00000000 0000e0

000008

6

2

[ 6] .symtab

SYMTAB

00000000 0000a0 000040 10

2

$ readelf -s main.o

Symbol table '.symtab' contains 4 entries:

Num:

Value

Size Type

Bind

Vis

Ndx Name

2: 00000000

0 NOTYPE

GLOBAL DEFAULT

UND function

3: 00000000

47 FUNC

GLOBAL DEFAULT

2 main

$ objdump -d main.o

Disassembly of section .text:

00000000 <main>:

1e:

89 04 24

DWORD PTR [esp], eax

mov

21:

e8 fc ff ff ff

22 < main + 0 \times 22 >

call

26:

8d 44 06 03

lea

eax,[esi+eax*1+0x3]

$ readelf -r main.o

Relocation section '.rel.text' at offset 0xe0 contains 1 entries:

Offset

Info

Type

Sym. Value

Symbol's Name

00000022

00000202 R_386_PC32

0000000

function

```

Listing 1.1: Key parts of an object file. main.o is the C example in Listing 1.3 compiled for x86 to an object file. Note that in the main function we had a call to function, which was not defined in the given source file. readelf -S lists the sections contained in the object file. We can see the symbol table (.symtab), the code section (.text) and its relocations (.rel.text). readelf -s lists the symbols defined in the symbol table. Note that the main symbol is defined at offset 0 from section 2 (.text), while the function symbol is marked as undefined (UND). objdump -d shows the relocatable assembly code of the main function. Note that the address of the target of the call function is not available. readelf -r lists the relocations. The only relocation is relative to the (undefined) symbol function, it's PC-relative (R\_386\_PC32) and targets the offset 22 of .text section, i.e., the 4 bytes representing the target of the call instruction.

Creation of the global symbol table. The linker collects all the symbol tables of the input object files and merges them. For instance, if an object file has an undefined symbol called "fibonacci", and another object file defines a symbol with the same name, they will be merged, and the symbol will be assigned the address assigned to the section containing it plus the offset specified in the defining symbol. The linker also checks that each symbol is defined no more and no less than once.

Fix of the relocations. At this point the linker has all the necessary information to execute all the directives encoded in the object files: the relocations. The address of the symbol associated to the relocation is taken, encoded as requested (e.g., absolute address or relative to destination address) and written at the specified position.

The global symbol table is emitted in the final executable in the .symtab section, mostly for debugging purposes. In fact, just as the section list, after the linking process it is irrelevant. What really matters for execution purposes are *segments*. As mentioned, segments group sections with similar characteristics. More specifically, a segment represents a portion of the program which will be mapped in memory exactly as found in the file with a certain set of permissions. This is the reason why .data and .bss will end up in the same segment: they both require to be loaded in writeable, readable but not executable memory pages.

Typically, a program contains two segments: one for writeable data (such as the one just described) and one for executable (non-writeable) data. The latter segment will contain .text and .rodata. Note that, despite the fact that .rodata doesn't need to be executable, it's often mapped by the linker in an executable page. While it would be possible to map it in a read-only, non-executable page, this would introduce a cost in terms of memory.

The ELF format describes a segment in terms of a start offset in the file, the virtual address where it should be loaded, its permissions and the size it has in the file and the size it should have in memory. The size in the file and in memory can differ, due to the fact that the sections containing exclusively zeros (i.e., .bss) are not serialized into the file, but are just taken into account as extra size at the end of a segment.

When the program execution is requested, the operating system, or more specifically, the kernel, will parse the list of segments in the program and map the specified portions of the file in memory as requested, zeroing out the difference between the file segment size and the memory segment size.

### 1.2.3 Dynamic Loading

So far, we've been describing the process to produce a so called *static* binary, i.e., a program that uses no dynamic libraries, and whose code and data has to be loaded at a fixed address. In this section we will see how the concepts presented so far can be extended to support dynamic libraries, and the process to load them in memory at run-time: *dynamic loading*.

In ELF-based systems, dynamic libraries offer a series of crucial benefits: they allow to have a single copy of a set of functions used by multiple programs on

1.2. ELF 9

the disk and in memory. In fact, dynamic libraries are designed in such a way that they can be loaded anywhere in the address space (i.e., not at a position determined at compile time) without changes. Code with this property is known as position independent code (PIC). Thanks to this feature, the operating system can have the same portion of the dynamic library file mapped multiple times, in different processes, at pages located at different addresses, but all mapped to the same physical page. This means that, despite the fact that a library, say the C standard library, can be used by hundreds of different applications at the same time, it will effectively be loaded in physical memory only once.

Therefore, a dynamic library, is similar to an executable file, except for the fact that all of its code is compiled as PIC, and the segment at the lowest address starts at address zero. The dynamic loader, a user space component (for Linux x86-64 usually located at /lib64/ld-linux-x86-64.so.2), will then load them where they fit best.

However, support for dynamic libraries is not limited to shared objects and PIC code. The linking process must be extended to allow the executable and dynamic libraries to have pending symbols even after the linking is finished. It will then be responsibility of the dynamic loader to fix them.

Therefore the concept of *visibility* of a symbol has been introduced. A symbol that has external visibility can be left pending at link time (as long as it is defined in a dynamic library specified on the linker command line), so that the dynamic loader will handle it.

The dynamic loader will complete the work left undone by the linker. In practice, this means that executables and dynamic libraries will have a dynamic symbol table (.dynsym section) and a list of dynamic relocations (.rel.dyn or .rela.dyn section). The main difference between normal relocations and dynamic relocations lies in the fact that dynamic relocations are not tied to a specific section (section are relevant exclusively in object files) but to a virtual address.

The dynamic loader will find all the information it needs in the .dynamic section, which contains the address and size of the dynamic symbol table and dynamic relocation table, plus the list of dynamic libraries the current executable/dynamic library depends on.

The problem at this point is: what are the targets of the relocations? Is is possible to have a relocation targeting an address in a read-only segment? The answer is no, in fact such a relocation would either trigger a segmentation fault or require the dynamic loader to temporarily map the containing page as writeable. Even ignoring the cost of such an operation, writing the page would trigger the copy-on-write mechanism of the operating system, which would create a new copy of the page, nullifying the above mentioned benefits of PIC code. To circumvent this problem, the GOT (Global Offset Table) and the PLT (Program Linkage Table) have been introduced.

**The GOT.** The Global Offset Table was introduced to handle accesses to global variables with external visibility (in most cases, defined in some dynamic library). The GOT is a table, stored in the .got section, containing an entry for each externally visible global variable. Each entry is the target of a dynamic relocation associated to the corresponding symbol.

```

$ objdump -d main

08048460 <main>:

804847e: 89 04 24

DWORD PTR [esp],eax

mov

8048481: e8 1a fe ff ff

call

80482a0 <function@plt>

8048486: 8d 44 06 03

lea

eax,[esi+eax*1+0x3]

080482a0 <function@plt>:

80482a0: ff 25 0c a0 04 08 jmp

DWORD PTR ds:0x804a00c

80482a6: 68 00 00 00 00

push

0 x 0

80482ab: e9 e0 ff ff ff

8048290 <_init+0x1c>

jmp

$ objdump -j .got.plt -s main

Contents of section .got.plt:

804a000 3c9f0408 00000000 00000000 a6820408

804a010 b6820408

$ readelf -r main

Relocation section '.rel.plt' at offset 0x264 contains 2 entries:

Sym. Value

Symbol's Name

Offset

Info

Type

0804a00c

00000107 R_386_JUMP_SLOT

00000000

function

```

Listing 1.2: Example of PIC code employing the PLT. We can see that the call to function (which is defined in an external library) has been fixed by the linker to point to function@plt. The PLT stub jumps indirectly to the content of its .got.plt entry (0x0804a00c), which, as shown by objdump -s contains 0x080482a6 encoded in little endian. Therefore, the first time the PLT stub will be invoked, the indirect jump will proceed to the next instruction, which will push on the stack the identifier of the dynamic relocation 0 and invoke the dynamic loader. The dynamic loader will then resolve the relocation (targeting the function .got.plt entry at 0x0804a00c) and from then on, the PLT stub will jump directly to function bypassing the dynamic loader.

1.3. LLVM 11

Basically, instead of patching the instruction performing the memory access in .text, the code doesn't perform a direct access but first loads the address of the global variable from the corresponding GOT entry and then performs the load or store through the pointer in the GOT.

The net effect is that, at the cost of performing an extra memory access, the segment containing the code doesn't need to be patched.

The PLT. The method described above could work for calls to functions with external visibility as well. However, a program having externally visible symbols could take a long time to launch, since all the relocations would have to be resolved each time. This is particularly unsatisfying when functions that are never used during the regular execution of the program need to be resolved. The abort function, for example.

For this reason, the lazy loading mechanism has been introduced. Basically, a new GOT, employed exclusively for functions, is introduced and placed in the .got.plt section. In practice, when the program needs to call an external function, it performs a call to a small code stub in the Program Linkage Table (.plt section). The stub jumps to the address contained in the entry corresponding to the target function in the .got.plt. However, unlike the .got, relocations targeting .got.plt are not resolved at startup, instead their initial value is left. The initial value is a pointer to the instruction next to the above mentioned jump, which writes in a register the identifier of the relocation associated to the target function and then transfer control to the dynamic loader. The dynamic loader will resolve the requested relocation, and from then on, when the PLT stub is invoked, it will jump directly to the correct address.

Such a mechanism is known as *lazy loading*, since the relocation associated to a certain function is resolved the first time it is called, or it is never resolved, in case it's never called.

Listing 1.2 shows an example of PIC code employing the PLT.

#### 1.3 LLVM

LLVM (formerly Low Level Virtual Machine) is an open source compiler framework which has gained popularity in recent years. The main reasons for its popularity lie in the fact that it is written in modern C++, well engineered, fast and simple to use. One of the most appreciated features is the simplicity and clearness, compared to its competitors, of its only intermediate representation: the LLVM IR. It is also very easy to write optimizations and analyses, known as passes, both for the mid-end and the back-end. Moreover, since its inception, LLVM was designed to be usable as a library, which allows, for instance, to merge the compilation and assembly phase (without ever having to serialize the assembly in textual form) and makes it particularly suitable to be employed as Just-In-Time (JIT) compiler. On top of this it has a great and active community and a less restrictive license compared to its main competitor, GCC.

The most popular LLVM front-end is clang, a front-end for C and all of its main derivative languages (including C++, Objective-C and OpenCL). Other front-ends

are available, with different maturity degrees, for many other popular programming languages such as Rust, Fortran, Ruby, Java, Python and D.

Since in this work we will be working extensively with the LLVM IR, in the following we will provide a brief introduction to its main characteristics. Unless otherwise noted, we will be working with LLVM version 3.8.

#### 1.3.1 The LLVM IR

The LLVM IR is an intermediate representation, typically emitted by a compiler front-end, suitable for being manipulated and optimized before begin passed on to the compiler back-end. In this section, we will briefly describe the LLVM modules, their structure and the LLVM type system.

The compiler works on a single translation unit. A translation unit in LLVM is represented by a *module*. A module is composed by a series of *global objects*, i.e., global variables and functions. A global object can be thought as a pointer to the storage associated to that object, that is either the code of the function or the actual data of the global variable. In fact, as we will see, global variables have pointer type.

Functions are basically a container of basic blocks. The order in which basic blocks appear in a function doesn't matter, except for the first one, which is elected as the entry basic block. This is due to the fact that each basic block has no fallthrough basic block, but each successor (if any) is explicitly specified.

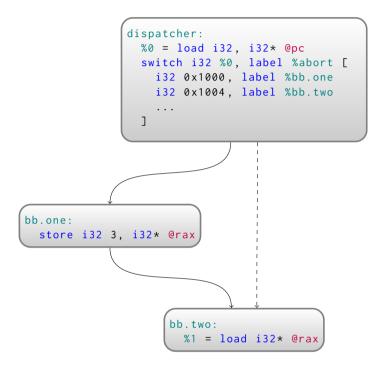

In turn, basic blocks are composed by one or more *instructions*. Each basic block must be terminated by a *terminator instruction*, such as a branch (direct or indirect, conditional or unconditional), a switch instruction (analogous to the C switch statement) or an *unreachable* instruction, which has no successors and represents the fact that execution should never reach that point.

Before proceeding in the description of the other instruction types it is important to understand one of the key features of the LLVM IR: the SSA form. The Static Single Assignment form, is a form of IR where each variable can be assigned at most once. The concept of *variable* in the LLVM IR is translated into the concept of *value*. In practice most LLVM instructions produce a value (e.g., the result of an addition), implicitly creating a new *variable*. After the creation of the value, it can be only used (i.e., read) and never assigned again. The SSA representation of the code makes certain analyses or optimizations very easy. For instance, identifying an instruction whose result is never used is straightforward (its use list is empty).

In the following we list the LLVM instructions most relevant to our ends, many of which are exemplified in Listing 1.3.

**Arithmetic**/logic instructions. They represent the classic arithmetic/logic instructions. They typically have two operands and produce an output of the same type. Only the specified operation is performed, with no side effects.

**alloca.** Reserves a certain amount of space on the stack and returns a pointer to it. This the typical way in which front-ends emit local variables. Later passes, such as scalar replacement of aggregates (SROA), if possible, will try to

1.3. LLVM 13

promote them to SSA values. Apart from the above mentioned benefits, SSA values are also candidates for being assigned to registers during the register allocation phase.

- **call.** A function call. It can have one or more arguments and a return value. It can be direct, when the target function is a known function, or indirect in case the destination is known at run-time only.

- **load/store.** Given an address, they perform a load or store from memory. Global variables and local variables associated to an alloca instruction are read or written through memory stores.

- **icmp.** Perform a comparison between two integers for equality, inequality, greater than and so on. Their result is a boolean (a 1-bit integer) which is typically employed as a condition in a conditional branch instruction.

- br. The branch instruction can either be direct, if the destination address is explicitly identified in the code, or indirect, in case the target address is the result of some computation. Moreover a branch can either be unconditional or conditional. Conditional branches have three operands: two references to basic blocks and a single-bit integer which represents the condition based on which the former or the latter basic block should be executed next.

- **switch.** Similar to the br instruction, it can have multiple successors. The taken successor is chosen depending on the value assumed at run-time of a certain SSA value. Similarly to the C switch statement, a list of possible constant values is listed, along with the corresponding target basic blocks.

- **phi.** Phi nodes have an operand for each predecessor, representing the value to produce in case the current basic block is reached through that predecessor. This instruction is rarely emitted by front-ends, since its need typically emerges due to the promotion of a local variable to the SSA value status. Since, in this thesis, we focus on a front-end, we will rarely discuss it.

Another key component of the LLVM IR relevant for our purposes are *metadata*. A *metadata* is a piece of information that can be associated to an instruction and can carry any type of information: it's a general purpose tool to decorate an instruction with additional information. Each instruction can be associated to multiple *kinds* of metadata, each one of them identified by a name.

A metadata node can contain other metadata nodes, integers and strings. It is therefore possible to build sophisticated structures of information. Debug information are encoded in LLVM IR in a special form of metadata (the !dbg kind).

It is important to understand that optimization passes are not required to preserve metadata, they can more or less be freely dropped, debug information included.

```

|22 = |DILocation(line: 4, column: 14, scope: |7)

%7 = phi i32 [ %6, %true ], [ 1, %entry

br i1 %3, label %true, label %epilogue

%5 = call i32 @function(i32* %2)

store i32 3, i32* %2, !dbg !22

define i32 @main(i32, i8**)

declare i32 @function(i32*)

%3 = icmp sgt i32 %0, 3

= add i32 %4, %5

%4 = add i32 %0, 3

br label %epilogue

alloca i32

ret i32 %7

epilogue:

9%

result = 3 + argc + function(&local_variable);

int main(int argc, char *argv[]) {

int result, local_variable =

int function(int *);

return result;

if (argc > 3)

result = 1;

```

Listing 1.3: Example of a simple C function and corresponding LLVM IR. %2 corresponds to local\_variable, which, unlike result, could not be promoted to SSA value since its address is passed to another function. local\_variable is initialized to 3 a phi instruction: in case the epilogue basic block was reached from true the value %6 is used, otherwise, if it was reached by the store instruction. The if statement is implemented through an icmp instruction (where %0 represents the first argument) and a conditional branch. In the true branch, the return value is computed through two additions and a function call. The call to function has as first and unique argument a pointer to local\_variable (%2). Finally the value to return, %7, is chosen through from entry, the constant 1 is employed. Note the !dbg metadata associated to the store instruction: it's a debug information describing the line, column and context from which it was generated. 1.4. QEMU 15

Finally, it is important to understand how the LLVM type system works. Each global variable, function, SSA value and constant is associated to a type. The most relevant types available are:

**IntegerType** an integer type of a fixed size in bit.

**PointerType** a pointer to another type.

**StructType** a type composed by a sequence of other types.

**ArrayType** a type composed by a finite number of elements of a certain type.

**FunctionType** a type describing the prototype of a function (return value type and zero or more arguments). A function type can also be variadic, in which case it can have a statically unknown number of arguments after those explicitly listed.

## 1.4 **QEMU**

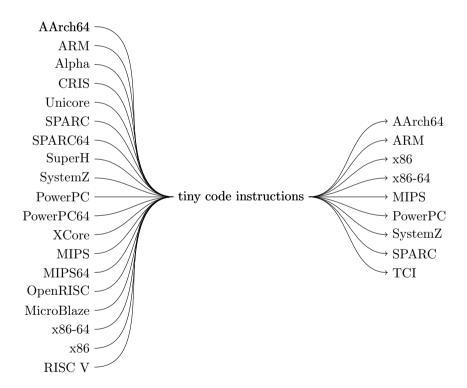

Figure 1.2: Architectures supported by QEMU. On the left, we have the front-ends, on the right, the back-ends.

QEMU is a dynamic binary translator (DBT). Given a program, it emulates it, one basic block at a time. Given an address, QEMU starts to decode the instructions at that address until a branch is found (i.e., the end of the basic

```

movi_i32 tmp0, $0x1005

movi_i32 tmp1, $0x4

sub_i32 tmp2, esp, tmp1

qemu_st_i32 tmp0, tmp2, leul,0

mov_i32 esp, tmp2

movi_i32 eip, $0x2000

```

Listing 1.4: Tiny code instructions generated from a x86 call instruction. The call instruction is located at address 0x1000, it's 5 bytes long (therefore the return address is at 0x1005) and it's performing a call to a function at address 0x2000. The return address is first materialized into tmp0, the constant 4 is put in tmp1, then the difference between the current value of esp and tmp1 is computed and put in tmp2. Then, the value of tmp0 is stored at the address represented by tmp2 and the value of esp is then updated with tmp2. This code is basically pushing the return address on the top of the stack. Finally, the program counter eip is updated with the address of the target function.

block). Then the instructions are translated from the input architecture to a set of equivalent instructions of the host architecture. For instance, if the user wants to run an ARM program on a x86 machine, the ARM instructions will be translated one by one in a set of equivalent x86 instructions, which will be then executed.

What is interesting in the QEMU design is the fact that it decouples the process of interpreting what a certain input instruction does from emitting the equivalent code using instructions of the host architecture. In practice, this means that, just as compilers do, QEMU doesn't directly translate an input instruction into equivalent instructions for the host, but first goes through an intermediate representation.

The intermediate representation is composed by *tiny code instructions*, and the component taking care of transforming them into code that the host can run is the *tiny code generator*.

In this sense, as shown in Figure 1.2, QEMU has a *front-end*, the part interpreting input instructions and emitting tiny code instructions, and a *back-end*, the part emitting instructions for the target architecture. This decoupling is particularly beneficial, since if we want to introduce a new input (target) architecture, it is enough to implement a front-end (back-end) and it will be automatically able to operate with all the existing back-ends (front-ends).

In Listing 1.4 a snippet of the tiny code instructions generated due to an x86 call instruction is presented. The code is similar to the intermediate representation of a compiler. Instructions have no side effects, therefore, the behavior of the input instruction is made completely explicit. Note also how QEMU employs temporary variables (tmp#) for temporary computations and global variables to represent the CPU state (e.g., the esp and eip registers)

Another key feature of QEMU are its two modes of operation:

**System mode.** Full hardware emulation. Suitable for booting a whole operating system or running bare metal code. Peripherals, MMU and all other hardware

components are emulated.

User mode. Emulation of the operating system only. This mode of operation allows, e.g., ARM binaries for Linux to be run on an x86 Linux host. Only the interfaces with the operating system are emulated, such as syscalls, signals and so on. This is possible thanks to a layer, that we call the *QEMU Linux subsystem* that forwards, with the appropriate changes, syscall arguments for the emulated system to the host system. In practice, an open syscall will be forwarded as is to the host operating system.

The user mode will be of greatest interest for us. In practice, the user mode allows Linux binaries to be run on Linux installations for a different architecture. The same is possible for FreeBSD. However, support for it it's currently broken in QEMU.

In terms of tiny code instructions syscalls are handled by calling an external function, written in C, which will perform the necessary operations. Such functions are known as *helper functions*. *Helper functions* are not limited to handling interactions with the operating system, they are also employed to translate instructions that would be too complicated to be implemented in terms of tiny code instructions. An example is the floating point division.

### 1.5 Monotone Frameworks

A Monotone Framework is a way to define a data-flow analysis in a general and effective way. A data-flow analysis associates a *value* to the entry and exit of each program *label*, typically, an instruction or a basic block. The value at the exit of a *label* is the value at the entry after the effects of the code in the *label* have been applied. These effects are different depending on the content of the *label* and are modeled by a *transfer function*. On the other hand, the value at the entry of a *label* is obtained by *combining* all the values at the exit of the predecessors' labels.

As an example, consider the even-odd analysis, which tries to track if the value of a certain variable, in a certain program point, is even or odd. We will have three possible values: EVEN, ODD or ANY. The initial state will be ANY. It's easy to formulate a transfer function by laying out some simple rules: 1) if the variable is assigned to an even (odd) constant, we move to the EVEN (ODD) state, 2) if we multiply the variable by 2, we go to EVEN, 2) if currently the variable is in EVEN (ODD) state and we add 1 we move to ODD (EVEN). It's also easy to define how values should be combined: suppose we have an if statement where the value after the true branch is EVEN, and after the false-branch is ODD, the common successor of the two branches will have to take into account both possibilities, producing the state ANY. If, on the other hand, both branches were to give the same result, say EVEN, then the common successor would be associated to EVEN too. Figure 1.3 illustrates this example. From the figure, we can derive the following set of equations:

$$n_{\bullet} = f_n(n_{\circ})$$

Figure 1.3: Graphs representing two simple programs. Each box represents a basic block.

$$a_{\bullet} = f_a(a_{\circ})$$

$b_{\bullet} = f_b(b_{\circ})$

$c_{\circ} = a_{\bullet} \sqcup b_{\bullet}$

where  $f_{\ell}$  represents the transfer function of label  $\ell$ ,  $\ell_{\circ}$  the data-flow value at the entry of label  $\ell$ , and  $\ell_{\bullet}$  the value at its exit.  $\sqcup$  is the operator that combines two data-flow values, producing a new value which is more generic than the two input ones. In this case  $f_n$  would be defined as producing ODD if its argument is EVEN, EVEN if its argument is ODD or ANY if its argument is ANY. On the other hand,  $f_a$  and  $f_b$  would produce ODD and EVEN respectively, no matter what their argument is.

Therefore, supposing  $n_{\circ} = \text{Odd}$ , a valid assignment for the variables of the set of equations above would be:  $n_{\bullet} = \text{Even}$ ,  $a_{\bullet} = \text{Even}$ ,  $b_{\bullet} = \text{Odd}$  and  $c_{\circ} = \text{Any}$ . Such a set of assignments are said to be *solutions* of the data-flow equations.

The presented analysis can track three possible different values. Note however that the set of possible different values in a data-flow analysis can be infinite, but they have to be part of a partial ordering relation. The partial ordering needs to have a top  $(\top)$  element and a bottom  $(\bot)$  element. The ordering between *elements* of the lattice, denoted as  $a \sqsubseteq b$ , can be read as "b is more generic than a", "b is less informative than a", or "b contains a". In our previous example, ANY is more generic than ODD. If ANY, ODD and EVEN are thought in terms of set of natural numbers, then ANY also contains ODD:  $\{1,3,5,7,\ldots\}\subseteq\{1,2,3,4,5,\ldots\}$ . On the other hand, ODD is more informative, in the sense that it can tell us something more specific about the value of the variable we are tracking, compared to ANY. In this specific case, therefore, ANY represents  $\top$ .

Consider the set of assignments of variables of the data-flow equations composed exclusively by  $\top$ . It would be correct (supposing we replace = with  $\sqsubseteq$ ), but very little informative, or, to be more precise, it would provide no information at all. The idea of the data-flow analysis is to obtain the most informative solution for the equations, without compromising its correctness.

**A more formal definition.** The data-flow information is represented by the property space L, i.e., the set of all the possible values that we can associate to a label. In a Monotone Framework, L must be combined with a partial ordering operator  $\sqsubseteq: L \times L \to \{true, false\}$ , i.e.,  $\sqsubseteq$  is reflexive, anti-symmetric and transitive.

We call  $(L, \Box)$  a partially ordered set.

In a Monotone Framework, the partially ordered set  $(L, \sqsubseteq)$  must have finite height. This means that all subsets Y of L where all the elements can be compared according to  $\sqsubseteq$ , must be finite. Or, in symbols:  $\forall Y \subseteq L : \forall l, l' \in Y, (l \sqsubseteq l') \lor (l' \sqsubseteq l), Y$  has a finite number of elements. This is the so called Ascending Chain Conditions [105].

$(L, \sqsubseteq)$  must also form a complete lattice. To define the concept of lattice we have to introduce the concepts of upper bound and least upper bound. Given a subset Y of L, an element  $l \in L$  is said to be an upper bound of Y if it is greater than any other element  $l' \in Y$ , or in symbols,  $\forall l' \in Y, l' \sqsubseteq l$ . On the other hand, if l' is an upper bound of Y and it is lower than or equal to all the other upper bound elements of Y, then it's said to be the least upper bound of Y. If a subset Y has a least upper bound, then it's unique and it can be denoted as  $\coprod Y$ . The concepts of lower bound and greatest lower bound can be easily defined by duality. A complete lattice is a partially ordered set  $(L, \sqsubseteq)$  such that all subsets of L have least upper bounds and greatest lower bounds. A complete lattice is therefore defined by the following elements:

```

L a set of elements. \sqsubseteq the partial ordering operator. \bigsqcup the least upper bound operator. \bigsqcup the greatest lower bound operator. \bigsqcup the top element \bigsqcup L. \bot the bottom element \bot = \bigsqcup \varnothing.

```

If we are computing the least upper bound of two elements  $\bigsqcup\{l_1, l_2\}$ , then we can also use the combine operator  $\sqcup : L \times L \to L$  defined as  $l_1 \sqcup l_2 = \bigsqcup\{l_1, l_2\}$ .

The data-flow equations can be therefore be defined as follows:

$$\begin{aligned} \operatorname{Analysis}_{\circ}\left(\ell\right) &= \begin{cases} i & \text{if } \ell \in E \\ \bigsqcup \left\{\operatorname{Analysis}_{\bullet}\left(\ell'\right) \mid \left(\ell',\ell\right) \in F\right\} & \text{otherwise} \end{cases} \\ \operatorname{Analysis}_{\bullet}\left(\ell\right) &= f_{\ell}\left(\operatorname{Analysis}_{\circ}\left(\ell\right)\right) \end{aligned}$$

where:

$\mathbf{Analysis}_{\circ}(\ell)$  represents the value (solution) associated to the entry of label  $\ell$ .

**Analysis** $_{\bullet}(\ell)$  represents the value (solution) associated to the exit of label  $\ell$ .

E represents the *extremal labels*, i.e., the set of entry point labels.

i represents the *extremal value*, i.e., the value associated with the entry point(s) of the program E.

$\bigsqcup$  is the *least upper bound operator*, as defined before.

F represents the set of edges of the control flow in the form  $(\ell', \ell)$  where  $\ell'$  is the source of the edge and  $\ell$  the destination.

$f_{\ell} \in \mathcal{F}$  is the transfer function for the label  $\ell$ , where  $\mathcal{F}$  is the set of all the transfer functions. Note the transfer functions have to be monotone [105].

**The MFP solution.** Once all the equations have been set out, we need to obtain a (non-trivial) solution to them. The Maximal Fixed Point (MFP) solution is the most popular approach to obtain a solution for a Monotone Frameworks since it provides good solutions and termination guarantees.

Algorithm 1.1 presents the MFP solution for Monotone Frameworks. The algorithm works on a queue (Worklist), initialized with all the edges  $(\ell,\ell') \in F$  of the control-flow graph. The idea of MFP is to start from a base solution which is then iteratively refined. The temporary result is stored in an associative array tmp mapping labels to elements of L. tmp holds the data-flow information at the beginning of the label (analogously to Analysis<sub>o</sub>) and is initialized with i for all the entry labels  $\ell \in E$  and with  $\perp$  for all the others.

After the initialization phase, the algorithm pops an edge  $(\ell,\ell')$  from Worklist, takes the last result produced for  $\ell$  (i.e.,  $tmp[\ell]$ ) and applies to it the transfer function for the label  $\ell$  ( $f_{\ell}$ ). If the result is lower than or equal to the last result produced by the successor of  $\ell$  currently being considered  $tmp[\ell']$ , then we are not producing any new information. Otherwise, we update the last result for  $\ell'$  merging into it the result of the transfer function ( $f_{\ell}$  ( $tmp[\ell]$ )). Then, since we changed the information associated to  $\ell'$ , we re-enqueue all of its successors  $\ell''$  such that ( $\ell', \ell''$ )  $\in F$ .

Once all of this process is finished, we emit the final solution as  $MFP_{\bullet}$  (the solution at entry of a label) and  $MFP_{\bullet}$  (the solution at exit of a label). The former is simply a copy of tmp, while the latter is tmp after applying to each element  $tmp [\ell]$  the respective transfer function  $f_{\ell}$ .

While proving the termination of the algorithm is outside the scope of this work, it's interesting to get an intuition of why it always terminates. The only possible source of non-termination relies in the possibility of re-enqueuing an edge an infinite number of times. Due to the algorithm structure, an edge can be re-enqueued only if the temporary result for the successor  $tmp \, [\ell']$  does not contain the result at the end of the current label  $f_{\ell}$  ( $tmp \, [\ell']$ ). If this happens the temporary result of the successor is updated to include  $f_{\ell}$  ( $tmp \, [\ell']$ ). However, since at each iteration  $tmp \, [\ell']$  will move closer to  $\top$ , and since the lattice is guaranteed to have a finite height (thanks to the Ascending Chains Condition), this can happen only a limited number of times. The termination of the algorithm is therefore guaranteed.

It is also interesting to note that the presence of  $\bot$  in the lattice is required only to initialize the values associated to non-entry labels, so that they will absorb directly whatever value is propagated first by their predecessors (since  $\forall l \in L, l \sqcup \bot = l$ ). Apart from this, having a bottom element is not required, and, in fact, in our *even-odd analysis* we didn't have it. In such cases, the  $\bot$  element can be artificially introduced in the lattice.

An alternative approach popular to build a data-flow analysis is *abstract inter*pretation. For information about its relationship with Monotone Frameworks, see [147].

```

Data: A Monotone Framework (L, \mathcal{F}, F, E, i, f)

Result: MFP_{\circ}, MFP_{\bullet}

/* Initialization

*/

Worklist = \{\};

tmp = \{\};

foreach (\ell, \ell') \in F do

Worklist.enqueue((\ell, \ell'));

end

foreach \ell \in E do

|tmp [\ell] = i;

end

foreach \ell \in F \setminus E do

|tmp[\ell] = \bot;

end

/* Iterative refinement of the solution

*/

while not Worklist.empty() do

(\ell, \ell') = Worklist.pop();

if f_{\ell}(tmp[\ell]) \not\sqsubseteq tmp[\ell'] then

tmp [\ell'] = tmp [\ell'] \sqcup f_{\ell} (tmp [\ell]);

foreach \ell'' such that \exists (\ell', \ell'') \in F do

Worklist.enqueue ((\ell', \ell''));

end

end

end

/* Finalization

*/

for

each \ell \in F do

MFP_{\circ}[\ell] = tmp[\ell];

MFP_{\bullet}[\ell] = f_{\ell}(tmp[\ell]);

```

**Algorithm 1.1:** The algorithm to obtain the Maximum Fixed Point solution for a data-flow problem.

# Chapter 2

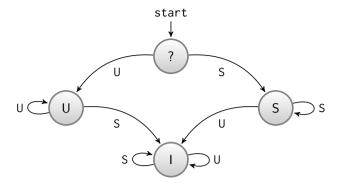

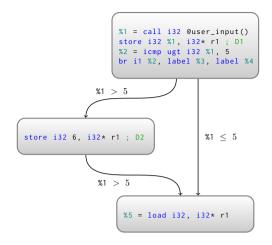

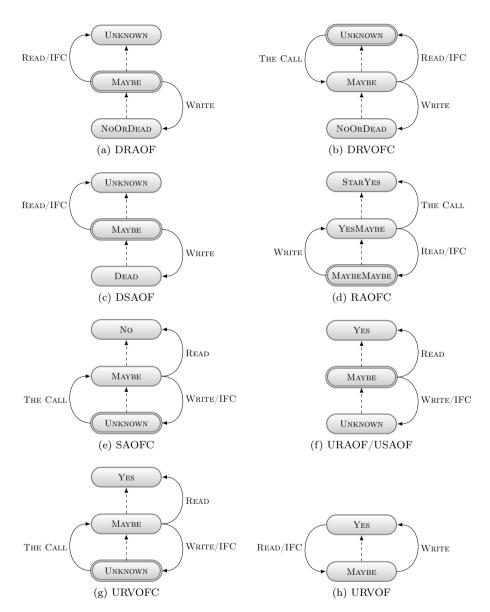

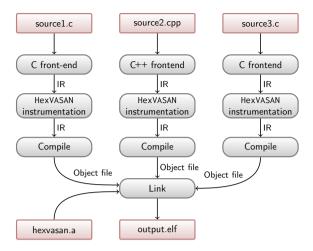

# A rev.ng Overview