Scuola di Ingegneria Industriale e dell'Informazione Dipartimento di Elettronica, Informazione e Bioingegneria Corso di Laurea Magistrale in Electronics Engineering

#### A Measurement-Based Approach for Interference Assessment on Multi-Cluster Parallel Processors

Advisor:

Prof. William Fornaciari - Polimi

Co-advisor:

Federico Reghenzani - Polimi

External-Advisors:

Dr. Luis J. de la Cruz Llopis - UPC

Dr. Jaume Abella Ferrer - BSC

Master thesis of: **Lorenzo Giuseppe Toscano** Matr. 884758

Academic Year 2018-2019

# Acknowledgements

I would like to dedicated this page to thank many people that I met during my Master thesis period that made this experience unforgettable.

Firstly, I want to thank Jaume Abella Ferrer, my advisor at BSC, for the helps that he gave me. He followed me during all my the Master thesis period, giving me the materials that were needed to study for the purpose to achieve. Thanks for the patient that he had to answer all my questions and my doubts that arisen during this experience at BSC, for his kindness and for the time that he dedicated to help me.

I'm grateful to Mikel Fernández, engineer at BSC, for his help and for the tips that he gave me about the several new programming languages that I had to deal with. Thanks for his patient, for the time he spent to explain me clearly new concepts about my work, speeding up all the work that I had to do, and to repeat some of them that I didn't understand the first time.

Particularly thanks go to Dr. Enrico Mezzetti, which help me a lot with many tips about programming languages and technical documents, and to the PhD student Suzana Milutinovic, which helped me to understand some new concepts during my work. I'm grateful to Dr. Francisco J. Cazorla, leader of this group, which introduced me to all the CAOS team members the first day that I arrived, and to Dr. Leonidas Kosmidis for his advises and helps that he gave me during my path to conclude this work. Thanks very much to Matteo Fusi for his help and the contribution that he gave for this Master thesis.

Thanks to the whole CAOS team, which embraces me in their team with great politeness and congeniality, making feel me part of it from the first week that I started to work.

Last thanks are dedicated to my friends and to my family, from my parents to my grandfathers, which believed in me and they supported me each day, cheering me up when problems seemed to be too much difficult to be overcame.

Thank you all, Lorenzo

### Abstract

Nowadays, microcontrollers used in critical real-time embedded systems use mostly one core, but are being replaced with more powerful hardware platforms that implement multicore systems. Among the latter, it is possible to identify in the space domain, for instance, the Cobham Gaisler NGMP developed for the European Space Agency (ESA), which is built with a SPARC quad-core processor that has a two-level cache hierarchy. For what concerns automotive and avionics environments, very flexible platforms like the Zynq UltraScale+ EG one has been regarded as a very powerful platform for these high-performance safety-critical systems. In fact, the aforementioned Zynq board implements two multicore clusters, namely an ARM dual-core Cortex R5 and an ARM quad-core Cortex A53, as well as a GPU and an FPGA. Due to the industrial trend towards the deployment of autonomous driving in the automotive domain and unmanned vehicles in the avionics domain, boards with such multicore systems are very promising.

The use of multicores brings a concern related to contention (interference) in the access to shared hardware resources, which challenges timing verification needed to prove that all critical real-time tasks will execute by their respective deadlines. In particular, Worst-Case Execution Time (WCET) estimates for tasks need to account for the impact in execution time that contention in shared resources may have. While such analysis has been performed on relatively-simple multicores, like the NGMP, it needs to be carried out on the more powerful and complex Zynq UltraScale+ EG platform. In particular, it is required to analyze the different sources of interference for the multicore clusters and how tasks need to be consolidated so that resource sharing is performed efficiently across tasks, thus minimizing the impact on execution

time for the most critical real-time tasks.

In this Master thesis work, the measurement-based methodology developed at Barcelona Supercomputing Center (BSC) to quantify the interference that arises across cores due to contention in shared hardware resources, is ported from the (simple) NGMP platform to each of the computing clusters of the Zynq UltraScale+ EG platform. Such methodology consists in the use of small microbenchmarks that aim at stressing specific shared hardware resources to create very high contention. Hence, this thesis investigates how to produce high contention in the shared hardware resources of the Zynq UltraScale+ EG platform, thus integrating those concepts working on the SPARC V8 instruction set of the NGMP to the ARM v7 and ARM v8 instruction sets of the Zynq platform. This requires porting and adapting microbenchmarks written partly in assembly code, verifying the Performance Monitoring Unit, and analyzing the sources of contention. As final step, guidelines are devised to properly consolidate software to be implemented on the target platform in order to contain as much as possible interference on critical tasks.

### Sommario

Oggigiorno, i microcontrollori utilizzati nei sistemi conosciuti come critical real-time embedded systems utilizzano principalmente un core, ma tendono sempre di più ad essere sostituiti con piattaforme hardware più potenti che implementano sistemi multicore. Tra questi ultimi, è possibile identificare nel dominio spaziale, per esempio, il NGMP Cobham Gaisler sviluppato per l'European Space Agency (ESA), che è stato sviluppato con un processore quad-core SPARC con una gerarchia di cache a due livelli. Per quanto riguarda l'ambiente automotive e quello avionico, piattaforme molto flessibili come quella denominata Zynq UltraScale + EG sono state considerate come piattaforme molto potenti per questi specifici sistemi embedded dal punto di vista della sicurezza ad alte prestazioni. Infatti, la Zyng board menzionata precedentemente implementa due cluster multicore, cioè un ARM dual-core Cortex R5 e un ARM quad-core Cortex A53, oltre a una GPU e un FPGA. A causa della tendenza industriale verso lo sviluppo della guida autonoma nel settore automobilistico e dei veicoli senza conducente nel settore dell'avionica, le piattaforme con tali sistemi multicore sono molto promettenti.

L'uso di multicore pone un problema legato alla contesa, ovvero legato all' interferenza, nell'accesso alle risorse hardware condivise, il quale mette in discussione la verifica dei tempi necessaria per dimostrare che tutte le attività che necessitano di essere calcolate in tempo reale (critical real-time tasks) verranno eseguite rispettando le rispettive scadenze. In particolare, le stime del Worst-Case Execution Time (WCET) per le attività devono tenere conto dell'impatto nei tempi di esecuzione che può avere la contesa nelle risorse condivise. Mentre tale analisi è stata eseguita su multicores relativamente semplici, come il NGMP, essa deve essere eseguita anche sulla più potente

e complessa piattaforma Zynq UltraScale+ EG. In particolare, è necessario analizzare le diverse fonti di interferenza per i cluster multicore e come le attività (tasks) devono essere consolidate in modo che la condivisione delle risorse sia eseguita in modo efficiente tra le attività, riducendo così l'impatto sui tempi di esecuzione per le attività più critiche in tempo reale.

In questo lavoro di tesi di Master, la metodologia basata sulla misurazione sviluppata presso l'azienda Barcelona Supercomputing Center (BSC) per quantificare l'interferenza che si genera tra i core a causa della contesa nelle risorse hardware condivise, viene portata dalla (semplice) piattaforma NGMP a ciascuno dei cluster di calcolo della piattaforma Zynq UltraScale+ EG. Tale metodologia consiste nell'uso di piccoli microbenchmark che mirano a stressare specifiche risorse hardware condivise per creare una controversia molto alta. Quindi, questa tesi indaga su come produrre alta contesa nelle risorse hardware condivise della piattaforma Zynq UltraScale+ EG, integrando così quei concetti che lavorano sul set di istruzioni SPARC V8 dell'NGMP ai set di istruzioni ARM v7 e ARM v8 della piattaforma Zynq. Ciò richiede il porting e l'adattamento dei microbenchmark scritti in parte in codice assembly, la verifica dei Performance Monitoring Counters e l'analisi delle fonti di conflitto. Come passo finale, sono state ideate delle linee guida per consolidare correttamente il software da implementare sulla piattaforma di destinazione al fine di contenere il più possibile l'interferenza nelle attività critiche.

# Contents

| A            | cknov | wledgements                                            |  |   |      | I |

|--------------|-------|--------------------------------------------------------|--|---|------|---|

| $\mathbf{A}$ | bstra | act                                                    |  |   | V    | Ţ |

| Sc           | omma  | ario                                                   |  |   | VI   | Ι |

| Li           | st of | Figures                                                |  |   | хv   | 7 |

| m Li         | st of | Tables                                                 |  | 3 | (VI  | Ι |

| Li           | st of | Algorithms                                             |  |   | XIX  | _ |

| 1            | Intr  | roduction                                              |  |   | 1    | L |

|              | 1.1   | Higher complexities in architectures implementations . |  |   |      | 1 |

|              | 1.2   | Complex architectures in safety-critical systems       |  |   |      | 2 |

|              |       | 1.2.1 Real-time systems                                |  |   |      | 3 |

|              | 1.3   | Multi-cores: benefits and drawbacks                    |  |   |      | 4 |

|              | 1.4   | Thesis Objectives                                      |  |   | . !  | 5 |

|              |       | 1.4.1 Measurement-based approach                       |  |   | . !  | 5 |

|              |       | 1.4.2 Zynq platform: targets                           |  |   | . (  | 6 |

|              |       | 1.4.3 Designing specialized benchmarks                 |  |   | . (  | 6 |

|              | 1.5   | Master thesis structure                                |  |   | . ,  | 7 |

| 2            | Bac   | ekground                                               |  |   | (    | 9 |

|              | 2.1   | Timing analysis                                        |  |   | . (  | 9 |

|              | 2.2   | Cache memory                                           |  |   | . 12 | 2 |

|              |       | 2.2.1 Cache structure                                  |  |   | . 14 | 4 |

|              |       | 2.2.2 Cache policies                                   |  |   | . 15 | 5 |

| XII | CONTENTS |

|-----|----------|

|   | 2.3<br>2.4 |         | C instruction set                                           | 18<br>20 |

|---|------------|---------|-------------------------------------------------------------|----------|

| 3 | Stat       | e of th | ne art                                                      | 23       |

|   | 3.1        | Perfor  | mance Stressing Benchmarks                                  | 23       |

|   | 3.2        | Power   | and Thermal Stressing Benchmarks                            | 27       |

| 4 | Met        | hodolo  | ogy                                                         | 29       |

|   | 4.1        | Microl  | oenchmarks                                                  | 31       |

|   | 4.2        | Perfor  | mance Monitoring Counters                                   | 32       |

|   |            | 4.2.1   | Common events                                               | 34       |

|   |            | 4.2.2   | Architecture-specific events                                | 35       |

|   | 4.3        | Tools   |                                                             | 36       |

| 5 | Imp        | lemen   | tation                                                      | 39       |

|   | 5.1        | Main f  | unction                                                     | 39       |

|   | 5.2        | Experi  | ments                                                       | 40       |

|   |            | 5.2.1   | Cache read operations: Load instructions                    | 41       |

|   |            | 5.2.2   | Cache write operations: Store instructions                  | 48       |

|   |            | 5.2.3   | Data prefetcher                                             | 54       |

|   |            | 5.2.4   | Events counting: PMCs                                       | 58       |

| 6 | Res        | ults    |                                                             | 61       |

|   | 6.1        | Experi  | ments in Isolation                                          | 61       |

|   |            | 6.1.1   | Cortex-A53 laboratory results                               | 62       |

|   |            | 6.1.2   | Cortex-R5 laboratory results                                | 78       |

|   | 6.2        | Experi  | ments with contenders                                       | 90       |

|   |            | 6.2.1   | List of experiments                                         | 90       |

|   |            | 6.2.2   | Task analysis: main core of the Cortex R5 cluster $$ . $$ . | 90       |

|   |            | 6.2.3   | Task analysis: main core of the Cortex A53 cluster $$       | 92       |

|   |            | 6.2.4   | Final results and Research Observations                     | 95       |

| 7 | Con        | clusio  | ns                                                          | 105      |

|   | 7.1        | Future  | development                                                 | 106      |

| CONTENTS     | XIII |

|--------------|------|

| Bibliography | 107  |

# List of Figures

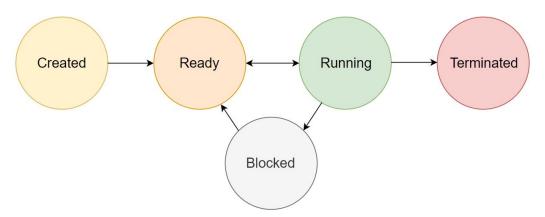

| 2.1 | State diagram of most typical primary process states. Possible   |    |

|-----|------------------------------------------------------------------|----|

|     | transitions from one state to the other one are pointed out with |    |

|     | arrows                                                           | 10 |

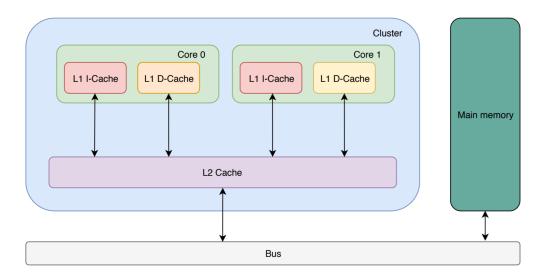

| 2.2 | Typical cache memory arrangement of modern processors            | 13 |

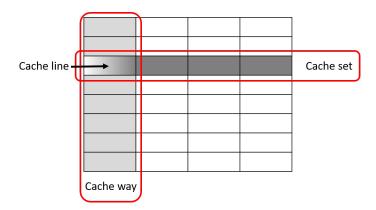

| 2.3 | structure of 4-way set associative cache                         | 16 |

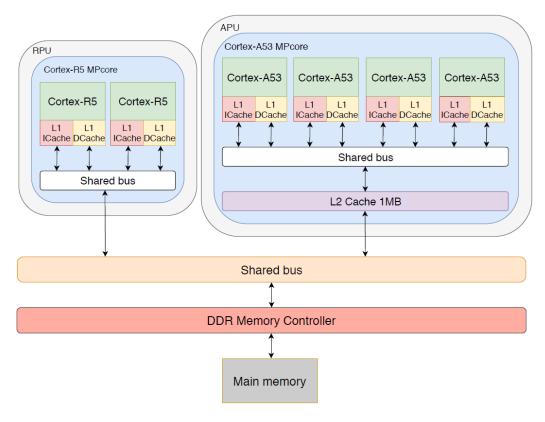

| 2.4 | Zynq UltraScale+ platform structure: APU and RPU embed-          |    |

|     | ded blocks with their relative processors                        | 19 |

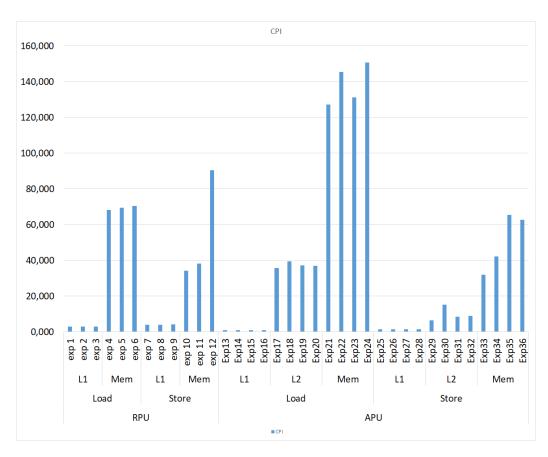

| 6.1 | Cycles per instruction plot of the experiments with contenders   | 98 |

# List of Tables

| 6.1  | L1 read cache hits accessing different sets - A53_0                      | 66 |

|------|--------------------------------------------------------------------------|----|

| 6.2  | L1 read cache misses accessing different sets - A53_0                    | 69 |

| 6.3  | L1 read cache misses accessing the same set - A53_0 $\ldots$             | 71 |

| 6.4  | L1 write cache hits - A53_0                                              | 74 |

| 6.5  | L1 write cache misses - A53_0 $\dots$                                    | 77 |

| 6.6  | L1 read cache hits accessing different sets - R5_0                       | 79 |

| 6.7  | L1 read cache misses accessing different sets - R5_0 $\ \ldots \ \ldots$ | 81 |

| 6.8  | L1 read cache misses accessing the same set - R5_0 $\ \ldots \ \ldots$   | 83 |

| 6.9  | L1 write cache hits - R5_0 $\dots$                                       | 86 |

| 6.10 | L1 write cache misses - R5_0 $\dots$                                     | 89 |

| 6.11 | Task analysis for main core of Cortex R5 cluster - Microbench-           |    |

|      | marks executed in each experiment by each core                           | 91 |

| 6.12 | Task analysis for main core of Cortex A53 cluster - Mi-                  |    |

|      | crobenchmarks executed in each experiment by each core only              |    |

|      | based on load instructions                                               | 94 |

| 6.13 | Task analysis for main core of Cortex A53 cluster - Mi-                  |    |

|      | crobenchmarks executed in each experiment by each core only              |    |

|      | based on store instructions                                              | 94 |

| 6.14 | CPU cycles and instructions performed in each experiment                 | 96 |

| 6.15 | Cycles per instruction results                                           | 97 |

# List of Algorithms

| 1  | General structure of the implemented microbenchmarks | 33 |

|----|------------------------------------------------------|----|

| 2  | Main function                                        | 41 |

| 3  | Array initialization using pointer chasing           | 43 |

| 4  | Microbenchmark based on Load instructions            | 45 |

| 5  | Microbenchmark to access the same set                | 47 |

| 6  | Microbenchmark for store hits - Cortex A53           | 51 |

| 7  | Microbenchmark for store hits - Cortex R5            | 52 |

| 8  | Microbenchmark for store misses - Cortex A53         | 54 |

| 9  | Microbenchmark for store misses - Cortex R5          | 55 |

| 10 | Disabling Data Prefetcher - A53                      | 57 |

| 11 | Disabling Data Prefetcher - R5                       | 58 |

| 12 | Performance Monitoring Counter function              | 60 |

# Chapter 1

## Introduction

Nowadays, the demand of high-performance systems is increasing consistently in automotive and avionics domains since industry needs applications able to perform increasingly complex functionalities in real-time. For instance, those functionalities related to autonomous driving in automotive and unmanned vehicles in avionics require capabilities for object detection, trajectory prediction, navigation and routing among others, and those capabilities have strict (real-time) deadlines.

In this chapter, an overall introduction of the motivation and the work done for this Master thesis is given, focusing on the current challenges that this thesis is trying to address. Afterwards, the Master thesis' structure is presented, highlighting in details each chapter content.

# 1.1 Higher complexities in architectures implementations

The complexity of the architectures of the high-performance systems is increasing since that the programs that have to be performed by such systems are becoming more and more complex as well. This problem is due to technological barriers like [1]:

• Breakdown Dennard scaling, which pushed CPU manufactures to use multi-core processors. In fact, since 2006 MOSFET scaling is not improving the overall circuit power consumption. The number of tran-

sistors is growing up without any issues, but the overall performance is growing slower.

- Single-core performance barrier, due to the impossibility of increasing clock frequency and, consequently, dissipating the additional power.

- Dark silicon, referring to specific circuitry of integrated circuits (ICs) that cannot be turned on due to power design constraints.

Indeed, CPU architectures are more complex, leading to increase the throughput and the number of pipelines, cache and processors to be implemented. For these reasons, real-time systems show issues for what concerns the Worst-Case Execution Time (WCET) analysis, since that the classic one is not suitable for such complex architectures. Many of those systems can be classified as Safety critical systems, meaning that a failure in those systems can cause casualties (or severe injuries), harm the environment or compromise the integrity of the system itself [2]. Timing analysis issues are addressed in details in Section 2.1.

# 1.2 Complex architectures in safety-critical systems

In such Critical Real-Time Embedded Systems (CRTES), it is critical and mandatory to ensure the satisfaction of real-time constraints. Due to the need of increasing high performance, multi-core processors have been adopted to perform all those critical activities within expected deadlines since they provide sufficient levels of performance. However, several challenges arise on the timing behavior due to the effect of inter-task interference in such systems. In fact, when two or more cores access the same hardware shared resources, contention is experienced, reducing the overall performance of the system.

This contention has a direct effect on the execution time of tasks, possibly increasing both the average execution time and the WCET. Hence, real-time systems running on complex platforms must undergo a validation step to assess to what extent execution time may grow. The timing non-determinism

caused by hardware and software must be systematically assessed and, in particular, an upper-bound to the timing interference in necessary to provide the WCET estimation [3].

So far, such assessment has been performed mostly on relatively simple multicores such as the Infineon AURIX TC27x architecture for the automotive domain or the Cobham Gaisler LEON4 processor for the space domain. However, autonomous navigation in avionics and automotive requires the adoption of further complex platforms with larger core counts and heterogeneous computation resources (e.g. time-predictable cores, high-performance cores, accelerators).

#### 1.2.1 Real-time systems

The board studied in this Master thesis belongs to the class of real-time operating systems (RTOS), which are employed in fields where it is mandatory to know the response time of a specific system. In fact, the system has to be deterministic, namely it is well specified in such system the real-time elaboration of specific processes in both best and worst case [4].

In practice, real-time systems have to guarantee that specific tasks respect deadlines constraints. Therefore, it is important for such systems to know the Task Execution Time (TET), which is a measure of the time required to execute specific real-time tasks. Such tasks can be classified according to their critically:

- soft real-time, when the task does not respect the prefixed deadline, the system is damaged, but it can be repaired.

- hard real-time, which corresponds to the previous statement about soft real-time, but with the important difference that the system cannot be repaired any more.

- "best effort", tasks that do not depend on real-time constraints.

From these definitions, it is possible to understand that real-time systems can be divided in two categories:

• hard systems, which are able to handle both hard and soft real-time tasks.

• soft systems, which can handle only soft real-time tasks.

#### 1.3 Multi-cores: benefits and drawbacks

Before going into deep details of the work developed in this Master thesis, it is important to recall issues that lead to the use of multicore system and the tradeoffs involved in their implementation.

The best choice in terms of complexity and efficiency is to employ cores that are devised exclusively to perform the specific tasks they are intended to execute, but typically real systems end up executing a large variety of tasks. Hence, even if many commercial multicores use general-purpose processing cores, those cores may be specialized to some extent so that some cores prioritize performance over power or vice versa, or limit complexity, etc. Such heterogeneous cores can be also deployed together in the same platform [5] so that end users (or some software layers on their behalf) can offload their applications on those cores that are expected to maximize the metric of interest (e.g. performance, power).

In multicores processors, the resources with high utilization are replicated replicate across cores in order to increase performance, whereas those resources with a typically lower utilization are shared across cores for the sake of efficiency. For instance, the utilization of some large cache memories and memory bandwidth is relatively low for many applications. Therefore, it is common setting up processors with multiple cores that, beyond a given level of the cache hierarchy, share the rest of the hierarchy (e.g. L2 cache and main memory access channels).

Sharing some resources, despite being an efficient solution in terms of resource utilization, creates a new issue: access arbitration due to contention. This is a relevant challenge since multiple cores may attempt to access a given shared resource simultaneously, and arbitration policies must provide balanced choices or, at least, configurable arbitration so that the user can decide the most convenient way to share the resource. Policies like round-robin are often used to grant access to shared resources, so that all cores are granted access to the shared resource periodically. Still, if the amount of requests to access this shared resource is high (at least during some time

5

periods), requests may get delayed, thus leading to lower performance that would be obtained on a single core architecture.

#### 1.4 Thesis Objectives

In the following subsections, the Master thesis objectives are presented. Firstly, we address goals and experiments performed on the target board with the measurement-based approach used in this work.

#### 1.4.1 Measurement-based approach

In this Master thesis, a measurement-based methodology is proposed to define how much interference can affect execution times in a specific platform, aiming to find the maximum execution time values in different scenarios. The aforementioned methodology has the following objectives:

- Assessment of interference from the quantitative standpoint without employing complex analyses, namely based on the results obtained experimentally by timing measurements.

- Comparison between two different versions of the same processor, in order to assess which one is the best suitable for real-time purposes.

- Estimating the effect on execution time of the contention on the access to shared hardware resources to understand whether it is a suitable platform (and for what type of applications), and how software must be consolidated to make an effective use of the platform.

- Generating as much pressure as possible on specific resources of the platform under study with stressful workloads provided by specific programs that are devised for such purpose. Such workloads are intended to expose how much execution time grows when accessing different shared hardware resources with different types of assembly operations. In order to maximize the stress on these specific resources, different types of operations and parameters tuning are needed to be employed and the details are addressed in Chapter 5.

#### 1.4.2 Zynq platform: targets

The methodology proposed so far is applied to the Zynq UltraScale+ EG platform studied in this thesis, which is a high-performance platform of the interest for several CRTES domains. In the context described in Subsection 1.2, the goal of this Master thesis is to assess whether such platform fits the needs to execute safety-critical real-time software. For this reason, the target of this thesis is to assess how much such inter-task interference (contention) can affect the performance of the Zynq UltraScale+ EG platform, focusing on the memory hierarchy of both Cortex A53 and Cortex R5 processors, which are implemented in the aforementioned multi-core system. Therefore, execution time has been studied and observed under specific experiments, which aim to stress the cache levels and memory implemented in the target processor emulating potential contention scenarios that may arise when consolidating tasks onto this processor.

#### 1.4.3 Designing specialized benchmarks

The proposed benchmarks are perfectly suitable for the approach described so far and for this reason they are the ones used in this work. Specialized microbenchmarks are designed for the Zynq UltraScale+ EG board to optimize the measurements, as in the case of NGMP Multi-core Processor [6], since that they can be more compact and precise to stress just some specific resources of the target platform w.r.t. the benchmarks of state-of-the-art, which can bring to imprecise or, in the worst case, to unreliable results.

In order to achieve the objectives explained above, some requirements have to be fulfilled by these benchmarks:

- Algorithms have to be written in C and assembly programming languages. This improves the speed and the quality of binary generation, guaranteeing that binaries perform exactly their intended activities, i.e. they stresses each components as expected. Such type of fine control would be very difficult to obtain using high-level programming languages.

- Simplicity and flexibility, i.e. they can easily be implemented in other processor architectures with minimal modifications and, as done in this

thesis, can be ported to multi-core systems with different cache hierarchies with negligible additional effort.

• The amount of memory used by the algorithms must be minimized in order to reduce the space occupied in the different cache levels, leaving the major part of the cache memory free for data. In this way, the contention can be then studied with the data patterns accessed without side effects caused by the code footprint.

#### 1.5 Master thesis structure

The second chapter presents some background needed to understand the key aspects of this thesis. This includes details on how timing validation is performed for CRTES, a brief introduction on cache memories structure and their mechanisms, as well as an overview of the main features of the processor architecture employed by the Zynq UltraScale+ EG platform. For what concerns the third chapter, it is addressed the state-of-the-art on micro-benchmarks, with particular emphasis on those devised to stress specific timing behavior relevant for timing analysis.

The fourth chapter focuses on describing the methodologies chosen to perform the experiments on the target platform. In particular, this chapter explains the general working principle for which the micro-benchmarks are devised, followed by the detailed description of the ones employed in this work. The concept of Performance Monitoring Counters (PMCs) is introduced, following the example of the ARM architecture and then moving the discussion on the ones relevant for this thesis use-case, i.e. the PCMs defined in the Zynq UltraScale+ EG platform.

In the fifth chapter, the main parts of the developed benchmark codes used for single-core experiments are described in details. How to exploit the PMCs implemented in the aforementioned ARM architectures is presented, together with the full description of their use in the employed algorithms.

The sixth chapter shows the results obtained of all the performed ex-

periments, considering both the single-core and the multi-core scenarios. Subsequently, the chapter describes how to analyze and draw conclusions from the obtained results, using the Zynq use case results as clarifying examples.

Finally, in the last chapter, the conclusions are presented with some proposal for possible future works.

9

# Chapter 2

# Background

In this chapter the relevant background theory for this work is presented. We start with Timing Analysis in Section 2.1, which describes generally how WCET of real-time programs can be estimated and problems related with such estimation. Subsequently, typical cache memories employed in modern processors are described, focusing on cache structure and policies used by ARM processors implemented in the target platform. Section 2.3 presents the most important instructions of SPARC instruction set, which are very similar to the ARM ones, concluding with Section 2.4 where Zynq UltraScale+ platform structure is described in detail focusing on the specific processor structures.

#### 2.1 Timing analysis

The estimation of the WCET of real-time programs has been investigated for decades. Two main paradigms can be found in the literature on how to estimate the WCET: Static Timing Analysis (STA) and Measurement-Based Timing Analysis (MBTA). STA relies on the availability of a timing model of the processor on which to calculate the overall timing needed for the whole program to execute each instruction, without requiring a simulation of it. In particular, the timing model of the target processor architecture is built identifying each hardware component, as well as their behavior and relationships regarding to timing behavior. The representation of the source code of the program (in the form of assembly instructions) is analyzed to

model both, the execution path flow and the data flow of the program, so that STA can account for the behavior of the different execution paths and potential data values.

In general, abstract interpretation builds upon unknown information, such as unknown input data values, which may affect memory access patterns and execution paths. This leads to an explosion of potential states that can be reached after the execution of every instruction. Such states are used to understand the behavior of processes in a specific computer system and to identify in which "state" the process is located. The most typical primary process states are described in the following and they are presented in the state diagram (2.1), noting that such processes are "stored" in the main memory.

Figure 2.1: State diagram of most typical primary process states. Possible transitions from one state to the other one are pointed out with arrows.

- Created It states a new process, i.e. when a process is created for the first time and never executed.

- Ready Right after the "Created" state, there is the "Ready" or "Waiting" one, which indicates that the process has been loaded into main memory. In this condition, there can be many processes and a ready queue is used to make CPU able to execute each of them one at a time.

- Running It is the running state and it defines when a process is executed by CPU.

- Blocked When a process is waiting for an event and it requires an external operation to trigger such event, it is "blocked" until an external operation is applied. This is the case when an I/O device is not available, like DVD, HDD and printer.

- Terminated A process is moved to the "terminated" state if either its execution is completed or it is killed.

STA makes the problem tractable by making "safe" (i.e. pessimistic) assumptions that allow merging different states into few ones that lead to the highest execution times possible. For instance, if the address accessed by a given load instruction cannot be determined, instead of modelling all potential states corresponding to all potential addresses that could be fetched, STA typically assumes that the access is a miss, that no useful data is fetched into cache, and that some cache contents are evicted (either a cache line or a full cache way). Overall, STA trades complexity for pessimism to keep computational cost tractable. A survey on timing analysis, with particular emphasis on STA, can be found in [7].

STA has increasing difficulties with increasingly complex hardware, as analyzed in [8], and simplifying the analysis process by merging states leads to potentially high pessimism. In general, the higher the hardware complexity (e.g. by using cache memories and multicores), the larger the number of potential states and execution time variation across states, and the higher the pessimism to merge states. It is important to point out that processor timing models are typically derived from processor specifications that may have thousands of pages. Manuals with very high number of pages make more difficult to perfectly define correct timing models of a specific processor, possibly jeopardizing their reliability. Moreover, those specifications are often subject to errata, further increasing the uncertainty on the reliability of STA [8].

On the other hand, MBTA is an hybrid approach that combines execution time measurements of the program under analysis on the target hardware platform with static program analysis techniques to estimate the WCET. MBTA approaches have also several sources of uncertainty due to the difficulties to guarantee that the execution conditions, inputs and processor states, are stressing the worst-case scenarios. Only in such conditions the WCET can be observed. For instance, generating inputs that trigger the

highest number of loops iterations, the worst paths in conditional constructs (e.g. if-then-else, switch), the worst memory patterns, etc. is in general out of reach for end users. The facts that measurement collection is affordable and the tightness of WCET estimates makes MBTA attractive for industrial uses [9]. Commonly, the inputs used for functional test of the software, which typically trigger the different operation modes of software, can be reused to obtain execution times relevant for WCET estimation. To increase the reliability of WCET estimates, some approaches can be followed: by adding an engineering factor to the maximum observed execution time (MOET) (e.g. MOET+20%) or by applying more sophisticated logic (e.g. using some static information about path analysis as done by tools like RapiTime [10]). Measurement-based analyses are a hot research topic, because of several challenges that are still open [11] and some methods are controversial [12]. However, while MBTA has been proven to be quite reliable for single-core

However, while MBTA has been proven to be quite reliable for single-core processors, multicore processors bring new difficulties due to the potential contention that the task under analysis can experience in the access to shared hardware resources. Thus, specific microbenchmarks causing high levels of contention have been considered to obtain execution time measurements relevant for WCET estimation in multicores [6].

#### 2.2 Cache memory

The access to memories is often a bottleneck for all modern processors since they generate latencies in the overall system. To reduce this problem, cache memories are implemented in processors to achieve very low latencies, since they are fast enough to serve data and code at high speed. Unfortunately, cache memories have to be small enough to achieve such speed and their cost is quite high, which brings to many technological issues. For this reason, one of the most important parameters to evaluate the performance of a processor is the memory latency. The introduction of cache memory reduces both power consumption and the number of external memory accesses performed by the system to the main memory, avoiding slow downs in the overall system [13].

Typically, the cache hierarchy implemented in modern processors is composed

of several layers, as represented in Figure (2.2), in order to achieve high performances.

Figure 2.2: Typical cache memory arrangement of modern processors

In such Figure, two cores are represented with two levels of cache, which are the first level (L1) and the second one (L2). Note that L1 cache is divided into Instruction Cache (I-Cache) and Data Cache (D-Cache), namely a modified Harvard architecture within which instruction and data buses are separated in order to reduce interference among them building on the fact that instruction and data access streams are naturally decoupled in program execution. Such buses are internal since they are used for connecting and interacting with internal components and they are not intended to communicate with external components like the main memory. The L2 cache is a resource typically implemented on multi-core, which are structures used to speed up the performance and they group several cores sharing both instruction and data.

When a memory location is accessed for the first time, there is no improvement in terms of access time to the memory. In fact, it is not yet present in the cache hierarchy and must be fetched from the main memory block, and it goes through the interconnection network (e.g. an AMBA AHB processor bus in the case of ARM Cortex-A53) to reach the most internal level cache, typically being stored first in the shared L2 cache and then in the L1 Cache.

Subsequent accesses to the same data memory location are much faster since the data is already available in the internal cache and there is no need to fetch it from the main memory [13].

Depending on the fact that data is found or not in the cache, the two previous cases can be distinguished as follows:

- Read cache hit: the data is available in the cache, enabling a rapid access to it.

- Read cache miss: the data is not available in the cache and it has to be sought in higher cache levels or directly in the main memory. Then, such data has to be copied in the cache. These steps lead to slow memory accesses, reducing system performance.

Cache hit and cache miss for writing operations change depend on the write policies of the cache implemented in a specific system and they are described in Cache policies section (2.2.2).

#### 2.2.1 Cache structure

The traditional types of cache structures are:

- Cache Fully Associative, thanks to which each location in main memory can be stored in any position of the cache. In general, allowing any data to be placed in any cache location requires expensive searches upon an access to determine whether the data is available in cache or not. Hence, this type of caches is expensive and used only for small caches.

- Cache Direct Mapped, which is the opposite of the previous cache structure. In fact, in this case, each location in main memory can be mapped in just one cache entry. Hence, searching for a given data is a cheap process since a single location needs to be checked. Thus, such structure is very convenient for large caches. However, the fact that each data has a predetermined location leads to cache conflicts where few data contend for the same cache entry despite large parts of the cache are empty.

• N-way Set Associative cache is a combination of direct-mapped and fully-associative caches. Each address is placed to a predetermined cache set, as in direct-mapped caches, but in each set there are multiple entries (the same number in each set) and the data can be freely allocated in any line within their set, as in fully-associative caches. Hence, the degree of associativity (number of entries per set) determines the performance and efficiency of these caches. In general, they are the preferred choice for large caches since they allow obtaining most of the benefits of fully-associative caches with costs close to those of direct-mapped ones.

The N-way set associative cache is the structure mainly implemented in almost all ARM processors [13]. In fact, in this thesis all the cache levels of the considered processors are N-way set associative caches. For this reason, the following paragraph describes in details such cache structure.

#### N-way set associative cache

A N-way set associative cache structure is conceptually arranged into S sets (rows) and N columns (ways), as shown in Figure (2.3). Each cell represents a cache line. Each location in main memory can be mapped to one and only one set, but its content can be placed in any of the cache lines (ways) in that set. Therefore, the lookup of a specific data is made in a group of N cache lines (those within the corresponding set).

Cache lines have a specific size (in bytes). In general, for the sake of implementation efficiency, all parameters are powers-of-two, and the size of the cache is determined as the product of the number of ways (N), the number of sets (S) and the cache line size (B). For instance, a 4-way cache with 128 sets and 64-byte cache lines is a 32 kB cache.

### 2.2.2 Cache policies

The replacement of cache lines is governed by several policies. This Section provides insights on those relevant to this thesis: replacement policies and write policies.

Figure 2.3: structure of 4-way set associative cache

Focusing on the replacement policies, there are two quite popular approaches employed in many systems:

- Least-Recently-Used (LRU), which aims to replace the data of a cache line that is the least recently used out of all those in the set. This policy leverages the time-locality, i.e. the fact that there is a high change to access the same location in a short time-span.

- (Pseudo-)Random, which ensures that on a miss event, a cache way in the corresponding set is randomly evicted to make room for the new cache line [14]. Since this policy is used in some platform considered in this thesis, we analyze it later in detail.

#### Regarding the write policies:

- Write-back (WB), which updates the main memory just when a cache line is evicted in the cache [13]. Thus, on a write operation, if the data is already present in the cache, it is only updated in the cache and not in memory unit. This policy is quite convenient in terms of performance, since many memory accesses are avoided, but it is more complex to implement since delayed memory writes need to be managed.

- Write-through (WT), which aims to update both the cache and the main memory of the system upon a write operation [13]. Vice versa to the previous case, this policy is less efficient but very easy to implement.

#### Pseudo-Random Replacement policy

If in a N-way set associative cache a Random Replacement policy is implemented, the probability that a specific cache line will be evicted is equal to  $\frac{1}{N}$  for each set [14]. Hence, cache hits or misses are, in theory, truly probabilistic within the cache set. It has been shown in [14] that the hit probability  $(P_{hit})$  for a specific access, for instance  $A_j$ , in an access sequence to its cache set like  $A_i, B_{i+1}, ..., B_{j-1}, A_j >$  is obtained using the following equation:

$$P_{hit_{A_j}} = \left(\frac{N-1}{N}\right)^{\sum_{k=i+1}^{j-1} P_{miss_{B_k}}}$$

(2.1)

where  $A_i$  and  $A_j$  are accesses to the same cache line,  $B_k$  corresponds to the accesses that are performed to cache lines different from the one where is present A and  $P_{miss} = 1 - P_{hit}$  is the probability to have a miss for any access.  $P_{hit_{A_j}}$  is the probability that A is survived after all evictions caused by  $B_k$ , while the probability that A is survived when one random eviction occurs is equal to  $\frac{N-1}{N}$ . Therefore, increasing the number of evictions in the cache set, increases the probability to evict A as well [14].

While this is the theoretical behavior of random replacement policies, actual implementations in processors may use poor pseudo-random number generators that do not produce fully random replacements. As shown later in the evaluation section, experimental evidences show that the random replacement policies implemented in the target platform may not be effectively random.

#### 2.3 SPARC instruction set

In order to correctly devise the microbenchmarks for the ARM processor architectures, we initially studied the microbenchmarks employed for the Next Generation MicroProcessor (NGMP). This architecture implements a SPARC V8 quad-core processor, which was developed by Cobham Gaisler for the future European Space Agency (ESA) missions [6]. For this reason, we analyzed some instructions provided by the SPARC V8 instruction set in detail [15]. In this section, we present the most important ones of the instruction set, in particular the memory write and read operations, since they

are specular to the ones in the ARM instruction set that produce analogous access patterns:

• 1d stands for *load*, which has the following syntax:

$$1d [r_s], r_d \tag{2.2}$$

where  $r_s$  is the source register and  $r_d$  is the destination one.

This is a memory read operation and it fetches from the main memory the data that is stored in the memory address specified in the register  $r_s$ . Afterwards, the fetched content is saved in the register  $r_d$ .

• st stands for *store*, which has the following syntax:

st

$$r_s$$

,  $[r_d + \text{offset}]$  (2.3)

where the same notation used for (2.2) is employed.

The store instruction is a memory write operation, which has the goal to deliver into a specific memory address defined in the register  $r_d$  of the main memory the value of the register  $r_s$ . Note that it is possible to specify an *offset* value, which is a constant number added to the variable register value. This feature is very useful for programs that perform many store operations in sequential memory addresses.

# 2.4 Zynq Ultrascale+

Development of specific microbenchmarks is the focus of this Master thesis to help WCET estimation of the target hardware platform that brings increasing difficulties due to the use of multiple and heterogeneous core clusters. However, such platform offers high computation power, which is of high interest for many industries such as those in the avionics and railway domains among others.

The Xilinx<sup>®</sup> UltraScale multiprocessor system-on-chip (MPSoC) implements in the same device both a processing system (PS) and user-programmable logic (PL).

For what concerns the PS, it features three main processing units:

- Cortex-A53 application processing unit (APU)

- Cortex-R5 real-time processing unit (RPU)

- Mali-400 graphics processing unit (GPU)

In the target platform structure represented in Figure (2.4) the first two individual blocks are presented, which are the ones of interest for the work in this Master thesis. In particular, the Zynq UltraScale+ board includes two clusters of processors that feature two different architectures: the ARM v8 architecture-based 64-bit for the APU and the ARM v7 architecture-based 32-bit for the RPU. Instead, the GPU is not subject of this work.

Figure 2.4: Zynq UltraScale+ platform structure: APU and RPU embedded blocks with their relative processors.

In the following subsections, Cortex-A53 and Cortex-R5 cache features are described in detail.

#### 2.4.1 ARM Cortex-A53 Processor

The APU of this platform consists of four Cortex-A53 MPCore processor cores and a L2 Cache, which is a shared resource among these four processor cores.

The Cortex-A53 processor has a modified Harvard architecture with internal different buses both for instructions and data. For this reason, the private Level-1 (L1) cache is divided in Instruction cache (I-cache) and Data cache (D-cache), both implemented as Set associative caches. Instead, the external bus is still a Von Neumann architecture, which delivers both instruction and data.

Subsequently, we describe the main features of the APU:

- ARM v8-A architecture instruction set.

- Possibility to choose either A64 instruction set in 64-bit mode or A32/T32 instruction set in 32-bit mode.

- I-Cache and D-Cache are separated.

- Cache size of both L1 caches is 32 KB.

- Cache line size is fixed to 16 words, which corresponds to 64 bytes, both for L1 I-Cache and L1 D-Cache. Hence, each of those caches has 512 cache lines of 64 bytes each.

- L1 I-Cache is implemented as a 2-way Set associative cache, whereas the L1 D-Cache is implemented as 4-way Set associative cache. Hence, the L1 I-cache has 256 sets with 2 cache lines each, whereas the D-cache has 128 sets with 4 cache lines each.

- Level-2 (L2) Cache size is equal to 1 MB.

- The replacement policy implemented for L1 caches is the Pseudorandom one, while for L2 cache we do not have any information from the processor specifications.

- For what concerns the cache update policies, the L1 Data and L2 caches use write-back policy. Since the I-cache does not modify the code stored, it does not need any write policy.

21

#### 2.4.2 ARM Cortex-R5 Processor

The RPU is a cluster that includes a dual-core Cortex-R5 for real-time processing. Also in this case the internal structure has a modified Harvard structure and N-way set associative caches.

The main features of this processor are:

- ARM v7-R architecture instruction set.

- The available instruction set is A32/T32.

- Instruction and data caches are separated thanks to the implemented Harvard architecture. The access to the main memory is instead performed through an external bus employed for both instruction and data.

- Cache size of both L1 caches corresponds to 32 KB.

- Cache line size is fixed to 32 bytes, which corresponds to 8 words of 4 bytes each, both for instruction and data caches. Hence, each cache has 1,024 cache lines.

- L1 Instruction and Data caches are 4-way Set associative. Hence, they have 256 sets with 4 cache lines each.

- Level-2 (L2) cache is not present in this cluster.

- Caches of the Cortex-R5 cores implement Pseudo-random replacement policy, which is the same implemented in Cortex-A53.

- The write-back policy is implemented in the Cortex-R5 L1 Data cache.

# Chapter 3

# State of the art

As explained before, some industries rely on MBTA for WCET estimation, and some approaches based on the use of microbenchmarks to model multicore contention have been found appropriate. Hence, in this section we review some of the main works in the area of microbenchmark development to induce high stress conditions in multicores. In particular, approaches generating stressful scenarios consider not only performance stressful conditions, but also power and temperature conditions as a means to assess relevant nonfunctional metrics of processors and applications. Due to their importance, these last banchmarks are discussed briefly in the last section of this chapter even if they are not in line with this Master thesis.

# 3.1 Performance Stressing Benchmarks

In the context of critical real-time systems, and with particular emphasis on commercial off-the-shelf (COTS) multicore processors, software testing has been largely exploited to test functional and non-functional properties of software. In particular, those tests are run during the analysis phase of the system, in early design stages, when many applications are still under development. In the case of WCET estimation, the objective is obtaining WCET estimates during the single task testing (i.e. when the task under analysis has been implemented), without the need of waiting for other tasks (e.g. tasks that will run concurrently) to also be implemented. This allows assessing whether execution time budgets allocated to tasks suffice to run

them and, if this is not the case, address this issue as soon as possible. Detecting timing violations during late design stages incurs high costs and may impact time-to-market.

Therefore, since tasks running concurrently are unknown during WCET estimation, assumptions need to be made on the contention those tasks can generate. Usually, this has been accounted for using simple programs, called microbenchmarks, that place specific amounts of contention on specific shared hardware resources. For instance, one may develop a microbenchmark by reading constantly from memory to generate high contention in the access to memory to measure how sensitive the task under analysis is to such contention.

Several strategies to create contention relevant for WCET estimation exist. Some authors created those types of microbenchmarks to study the impact of contention on high-performance Intel and AMD processors [16]. While those processors are generally regarded as inappropriate for critical real-time embedded systems due to the large number of hard-to-control sources of execution time variation, the strategy followed to develop microbenchmarks has been later reused to evaluate more appropriate processors. In particular, authors developed microbenchmarks with simple loops sufficiently small to fit in L1 Instruction caches, but sufficiently large so that the overhead to increase the loop counter and jump was negligible. Then, those loops contain a sequence of instructions of the same type accessing a specific shared resource (e.g. the second level, L2, cache) with the aim of creating the highest contention possible.

A similar strategy was applied on the Cobham Gaisler LEON4 processor [6], whose target is the Space domain. Experiments performed with microbenchmarks revealed that an early design of the LEON4 allowed to cause 20x slowdowns on a 4-core multicore. Microbenchmarks showed that, by using a non-split bus, the worst contention impact occurred when the task under analysis was performing sustained L2 hits whereas all other contenders were performing L2 misses. Upon an access to L2, the non-split bus gets locked by the accessing task and it is not released until the transaction completes. Hence, each (short) L2 hit of the task under analysis may have to wait for 3 memory accesses (L2 misses) caused by each of the 3 contender tasks. This behavior turned to be particularly exacerbated for store operations whose

latency for L2 hits is very low, whereas sustained store L2 misses caused 2 memory accesses each: one to evict a dirty line modified by previous stores and another to fetch the line accessed by the store itself.

While maximum stress contention scenarios are relevant for WCET estimation, they may be overly pessimistic for some platforms and applications. Hence, some authors extended microbenchmarks for the LEON4 platform to consider specific amounts of contention [17]. Authors build upon the concept of partial time composability instead of full time composability, meaning that the obtained contention bounds are only valid under specific amounts of contention. In particular, authors show how to account for specific access counts to each shared hardware resource so that the obtained contention bounds are valid as long as contenders do not exceed those access count bounds. This approach is particularly useful when some information about contenders is available, so that specific access count bounds can be set with the aim of upper bounding real access counts but without having to account for the maximum number of accesses possible. This approach builds on the use of maximum stress microbenchmarks to derive per-resource latencies, which are later used to statically model the maximum contention possible under specific loads. Also, this work devises microbenchmarks performing specific access counts as a mean to verify that the statically estimated contention bounds match the worst-case observed values.

A similar approach has been followed for the Infineon AURIX TC27x processor family [18]. Due to the particular characteristics of this platform to count events, an Integer Linear Programming (ILP) model has been developed to obtain upper and lower bounds to the values of PMCs counting the stall cycles. On the other hand, microbenchmark technology to measure maximum latencies and to create contention scenarios is the same of the previous work [17].

Such strategy has also been considered for the Qualcomm SnapDragon 810 processor within the framework of the H2020 SAFURE project [19]. Such processor has been regarded as appropriate for the telecommunications domain and used in many embedded systems such as the Sony Xperia smartphone. While the strategy followed for this platform has been analogous to that for the LEON4 and AURIX processors, results showed that the architectural documentation is incomplete and inaccurate for this platform [20].

In particular, the prefetcher could not be disabled and events monitored by PMCs were insufficient to estimate contention with meaningful accuracy. Thus, this platform has been regarded as inappropriate unless an improvement of available documentation so that the platform can be mastered to a sufficient extent.

Other authors attempted to model the contention in the interconnection network of the NXP P4080 processor – relevant for avionics and railway domains – by developing similar microbenchmarks [21, 22]. Their work revealed that contention is not linear with the number of cores, thus exposing that, while this 8-core architecture may seem to be symmetric, it is not. In particular, experiments revealed that contention caused by some cores was higher than that caused by others, thus exposing the fact that the interconnection network organizes cores into two different clusters, and contention between cores of the same cluster may be higher than across clusters. Further analysis of the NXP P4080 has been carried out with microbenchmarks assessing other types of execution time interference across cores, and revealing that, for instance, some asymmetric behavior is caused by cache coherence protocol, even in case tasks do not share any data [23].

Other approaches have focused on performing some forms of stochastic analysis of contention with the aim of identifying typical timing behavior under high contention on shared hardware resources, but without explicitly considering the worst case, thus providing a family of testing techniques building on the correlation of PMCs [24]. Those approaches build also upon the use of microbenchmarks to expose dependencies across events which, ultimately, requires the creation of some microbenchmarks producing high contention to reveal dependencies in the access to shared hardware resources. A similar approach building on similar types of microbenchmarks have been devised with the aim of applying statistical techniques such as principal component analysis to predict the worst contention bounds of critical real-time tasks on multicores [25].

Finally, some authors have attempted to model contention at late design stages by running simultaneously tasks that may contend against each other, modifying their time alignment (i.e. their relative starting time) to account for the worst – yet realistic – contention that specific tasks can cause on each other [26].

# 3.2 Power and Thermal Stressing Benchmarks

Stressing benchmarks have been used in other contexts with the aim of predicting other non-functional metrics such as power and temperature. Next we provide few illustrative examples of those applications of microbenchmarks. Thermal analysis by means of software-based solutions has been mostly considered for post-silicon validation of processors with the aim of identifying the Thermal Design Power (TDP), which is the maximum sustained temperature that a processor can produce. A proper identification of the TDP is key for chip manufacturers to size the cooling solution needed to keep the processor under specific temperatures. Triggering the TDP typically requires the development of the so-called power virus programs, which create sustained high-power activities [27, 28]. For instance, floating point operations have been shown to consume high energy, while allowing virtually executing one such operation per cycle per core. Hence, microbenchmarks building on those types of operations are often used to trigger specific high-temperature scenarios.

In essence, benchmarks intended to trigger high execution times (due to contention) or high temperature have similar structures (loops with specific patterns that repeat many times) varying the type of operation that is executed sustainedly depending on whether the objective is to create high contention or high temperature.

So far, we presented the benchmarks given by state-of-the-art, which are widely developed for many platforms, but they are not suitable to study aspects of the platform that we want to address. For this reason, we proceed presenting and explaining in details the development a new set of benchmarks together with a new measurement-based approach to study with more accuracy features of the target multicore system that cannot be addressed with the ones described in this chapter.

29

# Chapter 4

# Methodology

In this chapter, the methodology used for the experiments performed is explained in detail, explaining why and how such experiments are performed in order to achieve the expected objectives. In particular, different microbenchmarks and functions devised both in C and assembly programming languages are described in details, focusing on their features and their ability to detect the sources of unpredictability.

The proposed methodology consists of designing specific microbenchmarks to collect empirical evidence directly measuring the considered metrics on the target platform. Those microbenchmarks are executed in two scenarios: (1) in isolation and (2) together with co-running microbenchmarks (either identical or different) onto other cores. The results of these experiments are collected reading the PMCs available in the platform under study. In order to increase the results reliability, the following steps have been followed:

• Interference-free run: These tests are performed with all the cores (except the one where the microbenchmark runs) in power-down mode, in order to avoid any type of inter-core interference. In this way, it is possible to verify that both the microbenchmark and the target main core are properly working. Moreover, it is possible to verify if the features represented in the corresponding manuals are correct or not. The rationale behind these experiments is that microbenchmarks have a known behavior on the specific hardware: approximate values for some metrics such as executed instructions, cache accesses, memory accesses, etc. are known a priori and can be used as baseline values for

subsequent analyses.

- Study of PMCs behavior, understanding if they work properly, i.e. if the results obtained with measurement-based approach are the ones expected from the PMCs features reported in manuals. When the measurements performed show that PMCs are behaving differently as expected by the reading of manuals, PMCs are not working properly. It is carried out also the evaluation of how much noise and other type of disturbances can affect the behavior of PMCs. In this way, it is possible to assess that such counters are reliable enough to be used for achieving the goal of providing an useful and representative metric. This is an important step since it is not unusual having documentation where PMC description is scarce, so that their definition is ambiguous. In fact, manuals do not give always all PMCs information and many times they provide "IMPLEMENTATION DEFINED control" [29], compromising the complete study of the PMCs profile. A possible example is when PMCs have an unexpected poor accuracy that is shown by the results obtained using the measurement-based approach while instead they should be accurate. Also, since PMCs are not part of the functional behavior of the system, they are often less debugged that other parts of the processor and may have unexpected behavior.

- Collecting PMCs data when all cores are active, thus verifying that all PMCs can be interfaced properly even when all cores in both clusters are running their own private workloads. This is important to verify that events corresponding to shared hardware resources can be counted on a per-core basis, thus avoiding interference on PMC values themselves.

- Run several experiments with all the cores in running mode, using the same microbenchmarks devised before. Each experiment is distinguished among the other ones since that different microbenchmarks are executed in parallel. Therefore, there are processor cores behaving as "contenders" and one processor core that is the "task under-analysis". Contenders are the processor cores that can generate inter-task interference due to the contentions that arise in the hardware shared resources

with the main core under observation. These are the most relevant experiments since they represent the worst-case scenario that a given critical real-time task may experience in the system during operation.

• Collecting data of the PMCs results when all the processors are executing simultaneously, comparing them with the ones obtained for single cores. While the previous set of experiments exposes the actual behavior in terms of execution time, this set of experiments shows why execution time in parallel operation differs from that in single core operation. Thus, from the results of this set of experiments it is possible to detect what type and degree of interference occurs in each shared hardware resource. Such information is crucial to understand what the most convenient way to consolidate tasks is. In fact, based on the comparison between PMCs results obtained for all cores and for single cores, it is possible to define guidelines on which type of instruction is better to use among the other ones to get the lowest achievable execution time of specific tasks. Following these guidelines, software can be consolidated with the best performance achievable, by distinguishing in each scenario the instructions that guarantee the lowest number of contentions in shared hardware resources.

### 4.1 Microbenchmarks

As explained before, microbenchmarks can be used to evaluate performance of multi-core architectures. Reasons of such statement are confirmed from the fact that they are developed in C/C++ programming language, which is simpler than assembly and than high-level programming languages that can stress more the resources. Also, industry preference for quantitative evidence on the target platform is also a plus for this approach since that microbenchmarks are suitable to make measurements and collecting quantitative results. The size of each microbenchmark (in terms of code footprint) should be small enough to fit in the instruction cache, in order to avoid the shared resource interference caused by the instruction fetches from the higher cache levels or the main memory. The experiments are mainly focused on generating different loads in the memory hierarchy by controlling the amount and rate of

data transfers.

Algorithm 1 represents the conceptual schematic employed for the microbenchmarks proposed in this Master thesis. The parameters A and B represent the input arguments of the microbenchmark, where A depends on the type of operations performed, while B is the number of iterations of the main loop to be executed. Afterwards, benchmark-specific memory allocation and initialization procedures take place. In some experiments, memory initialization requires setting specific contents in memory so that the main loop of the microbenchmark maximizes the number of accesses per cycle. To this aim, it is employed the *pointer chasing* technique, which is addressed in details in the next chapter.

Finally, the loop body represented in such algorithm is mostly written in machine-specific assembly code (ARMv8 and ARMv7) in order to directly control the memory-related instructions without the unwanted compiler optimizations and side-effects. The type and number of instructions in each microbenchmark depend on the specific interference goal we want to achieve, i.e. on the location and magnitude of effects on shared resources. Among them, it is possible to distinguish two classes used in this work: the memory instructions that read from the main memory or cache (loads) and the ones that write to the main memory or caches (stores).

As shown in the next chapter, for implementation simplicity and flexibility purposes, the initialization/allocation phase and the main loop can be decoupled in different functions increasing the re-usability of the code across different microbenchmark types.

## 4.2 Performance Monitoring Counters

The quantitative evaluation of the results obtained with the microbenchmarks described in the previous section (4.1) is performed through the use of the *Performance Monitoring Units* (PMUs) existing in each core. Each unit includes a set of *Performance Monitoring Counters* (PMCs).

The PMCs available in both the Cortex-A53 and Cortex-R5 processor cores, are useful to verify that the experimental results correspond to the expected ones and to analyze the magnitude of interference in shared hardware

#### Algorithm 1 General structure of the implemented microbenchmarks

```

void Name_Microbenchmark (A, B)

{

Start memory allocation procedures

(...)

End of such operations

Start assembly code

Start Loop of B iterations

Memory Read/Write Instruction (A -> Register/Main Memory)

Memory Read/Write Instruction (A -> Register/Main Memory)

(...)

Memory Read/Write Instruction (A -> Register/Main Memory)

End Loop of B iterations

End assembly code

}

```

#### resources.

Such PMCs can be set to measure different events, so it is important to properly configure them to count the events of interest. Then, PMCs must be enabled or cleared right before the execution of the microbenchmark and disabled right after in order to monitor only the activity of the single microbenchmark. Once this is guaranteed, the values obtained for a given event type with PMCs can be compared against the expected values. As first step, experiments were performed in order to check if the PMCs of such processor works properly, i.e. comparing the experimental results obtained by PMCs counting for one event with the expected ones. When the two kind of results are matched, the PMCs counting for such event is reliable, so that knowledge can be built on top of its results when collecting data for single core and multi-core experiments. Proceeding with this approach, it is possible to define the reliability of the PMCs counting for all the implemented events. After that PMCs are confirmed to properly work, a C programming language interface is built in order to access the PMCs values from the microbenchmarks code. The PMCs interfacing has been integrated in the function where the microbenchmark was defined in order to improve the reliability of the measurements of each event counted. In particular, PMCs interface is nested in each microbenchmark and it is divided in two main

blocks: the first one placed right before the core of the specific microbenchmark, i.e. the beginning of assembly code, and the other one right after the end of iterations made by such assembly code.

Several PMU, or PMC, events are available for these architectures and in the following paragraphs we list the most important ones that have been used for experimental evaluation. Firstly, the common events are described, followed by the Cortex-A53 and Cortex-R5 specific events.

#### 4.2.1 Common events

- L1D\_CACHE L1 Data cache access, which counts how many times the L1 Data cache is accessed by any operation. Read and write accesses are not distinguished.

- 2. L1I\_CACHE L1 Instruction cache access, which counts instruction memory accesses to both the L1 Instruction cache and L1 Instruction memory structures.

- 3. L1D\_CACHE\_REFILL L1 Data cache refill, which corresponds to the number of read and write misses that occur in the L1 Data cache. In this case, the PMC counts each access to L1 cache causing a refill of a cache line brought from the upper level (either main memory or another cache level).

- 4. L1I\_CACHE\_REFILL L1 Instruction cache refill, which corresponds to the number of read misses that occur in the L1 Instruction cache. Note that the L1 I-cache is read-only, because the instructions are in general only read from the main memory.

- 5. CPU\_CYCLES This counter counts the number of processor cycles. To compute the execution time, we need to use the operating frequency of the processor since it may operate at a different frequency than other components (e.g. main memory). Combining this counter with the previous ones, it is possible to figure out the frequency of the occurrence of a specific event (e.g. number of L1 Data cache misses per cycle).

### 4.2.2 Architecture-specific events

Since the cluster Cortex-A53 architecture differs from the Cortex-R5 one, some events are specific of core type. For instance, the Cortex-A53 cluster has an L2 cache, whereas the Cortex-R5 cluster has not.

#### Cortex-A53

- 1. APU\_L2D\_CACHE\_REFILL L2 Data cache refill, which counts the number of accesses to the L2 cache causing a refill of a L2 cache line, regardless of whether they also cause a refill of the L1 Instruction cache, the L1 Data cache or none of them. This means that events 4 and 3 may overlap with this event if there is a miss in L2.

- 2. APU\_L1D\_CACHE\_WB L1 Data cache Write-Back, which corresponds to the number of performed write-backs from L1 Data cache to higher memory levels like L2 cache or the main memory. In other words, it counts how many times a modified line in L1 Data cache is evicted.

- 3. APU\_L2D\_CACHE\_WB L2 Data cache Write-Back, which corresponds to the number of write-back of data performed from L2 Data cache to main memory.

- 4. APU\_L2D\_CACHE L2 Data cache access counter considers all accesses to a cache line of the L2 Data cache caused by read and write operations. Therefore, it includes the number of refills of both L1 Instruction and Data caches and the number of write-backs of data performed from L1 Data cache. This means that this event is the sum of all the accesses performed to a cache line of the L2 cache performed by L1 caches, i.e. the aforementioned events 4, 3 and 2 are included in this event.

- 5. APU\_MEM\_ACCESS The memory accesses counter considers all accesses to L1 Data cache, L2 Data cache and main memory caused by read and write operations. Differently from APU\_L2D\_CACHE counter, it does not include the number of:

- Refilling of any cache.

- Write-backs of data performed from any cache.

- Instruction memory accesses.

- 6. APU\_EXT\_MEM\_REQUESTS The external memory request counter is defined for the APU of Cortex-A53 and it increments for each memory access request to the main memory that is "external" to such unit, thus including L2 cache misses and L2 cache write-back operations.

#### Cortex-R5